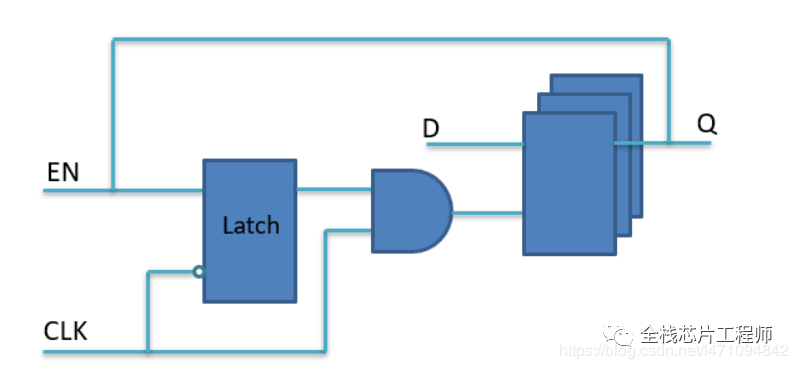

clock gating和power gating是降低芯片功耗的常用手段,相比power gating設計,clock gating的設計和實現更為簡單,多在微架構、RTL coding階段即可充分考慮,在綜合時(compile_ultra -gate_clock)即可自動mapping到clock gating結構上去。本文先講解clock gating,ICG的基本結構如下圖所示:

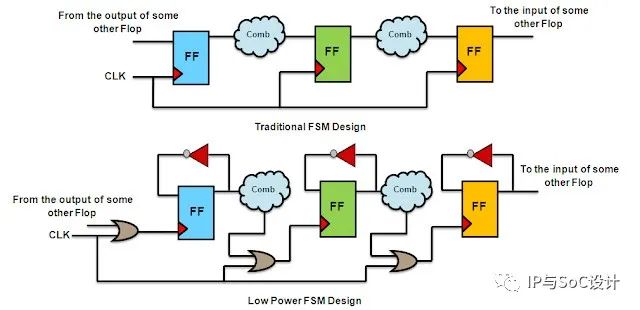

門控時鐘電路有效的降低了動態功耗,因為其減少了時鐘樹的翻轉行為、減少了寄存器clock pin的翻轉行為、減少了大量MUX邏輯消耗的功耗,一般可以節省20%-60%的功耗,同時也節省了MUX面積。

門控時鐘單元分成兩種,一種是帶鎖存器(latch based)的門控時鐘單元,一種是不帶有鎖存器(latch free)的門控時鐘單元。latch based的門控時鐘單元能避免毛刺,因此更推薦使用。

門控時鐘又分為離散的和集成的(ICG)兩種:

- 離散的CG單元

1)帶latch的CG(默認)

set_clock_gating_style -sequential_cell latch

2)不帶latch的CG

set_clock_gating_style -sequential_cell none - 集成的CG單元(ICG)

set_clock_gating_style -negtive_edge_logic "integrated"

通常,在執行命令compile_ultra -gate_clock前需要設置好clock gating的相關配置選項,具體選項如下:

set_clock_gating_style的options解析如下:

- -sequential_cell none | latch

1)-sequential_cell latch(默認)指帶latch的CG(latch based style), 并可指定使用具體某個latch cell,比如:-sequential_cell latch:lib_cell。

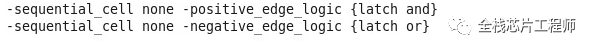

2)-sequential_cell none指不帶latch的CG(latch free style),比如:

與門做CG,時鐘使能為1時鐘穿透AND,但posedge trigger存在毛刺;

或門做CG,時鐘使能為0時鐘穿透OR,但negesge trigger存在毛刺;

- -minimum_bitwidth minsize_value

為了節省gating cell的數量,需達到一定寄存器數量的register bank才使用gating cell。

-

-setup setup_value 指定建立時間

-

-hold hold_value 指定保持時間

-

-positive_edge_logic {cell_list | integrated [active_low_enable]

[invert_gclk]}

-

{cell_list}用于指定“上升沿”觸發使用的CG單元。需要注意的是-sequential_cell指定的是否有latch應該和cell_list的對應電路是否含有latch保持一致,如:

set_clock_gating_style -sequential_cell latch -positive_edge_logic { latch and }

set_clock_gating_style -sequential_cell none -positive_edge_logic { or }

-

{integrated}用于表明使用上升沿觸發的ICG單元。

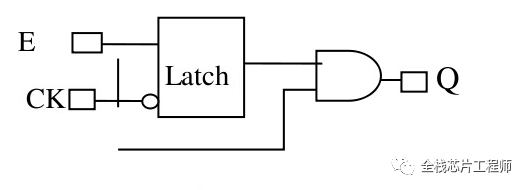

如下圖所示,該ICG單元就是一個pre-conctrolled positive-edge triggered clock gating latch。

-

-

-negative_edge_logic {cell_list | integrated [active_low_enable]

[invert_gclk]}

-

{cell_list}用于指定"下降沿”觸發使用的CG單元。需要注意的是-sequential_cell指定的是否有latch應該和cell_list的對應電路是否含有latch保持一致,如:

set_clock_gating_style -sequential_cell **latch ** -negtive_edge_logic { latch or }

set_clock_gating_style -sequential_cell ** none ** -negtive_edge_logic { and }

如下圖,-sequential_cell none指定latch-free模式,但是cell_list卻指定了latch、and/or, 這種情況下,DC工具仍然會綜合出latch-based clock-gating的電路。

-

{integrated}用于表明使用下降沿觸發的ICG單元。

如下圖所示,該ICG單元就是一個pre-conctrolled negative-edge triggered clock gating latch。

- -control_point none | before | after

對于DFT測試電路,為了滿足電路可控,需要引入TE信號來控制latch的使能端。before就是在Latch之前插入或門,將TE信號和時鐘使能信號或起來然后連接到Latch的D端。同理,after就是在Latch之后插入或門,將TE信號和Latch的Q端或起來然后連接到IGG的AND門。 - -num_stages num_stages_count

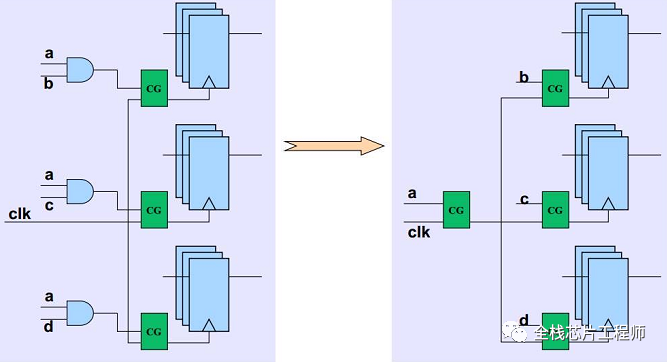

工具默認只使用一級門控時鐘,而使用多級門控時鐘可進一步節省面積、降低功耗。如下圖,a信號被三個CG單元共享,那么將a信號做成第一級CG,b、c、d做成第二級CG。這樣,增加了一個CG但減少了3個與門,同時節省了組合邏輯和第二級的CG的功耗。

set_clock_gating_style -num_stages 2

那么如何編寫門控時鐘的RTL代碼風格呢?

第一種風格:

綜合出來電路有32個MUX2選擇器:

我們換一種寫法,DC工具就可將load_cond作為Latch的使能,從而一個clock gating cell便取代了32個MUX2,節省了大量面積的同時,還節省了32個寄存器的動態功耗,32MUX2組合邏輯的功耗,也節省了時鐘樹上buffer的功耗。

那么如何保證ICG中Latch的時序呢?

除in2reg、reg2reg、reg2out、in2out類型路徑外,我們會經常看到reg2cgate的setu/hold檢查,即clock gate上enable信號要比clock信號提前到達一段時間setup和保持一段時間hold。

通常clock gate上的setup較難收斂,如下圖

- register CK端作為launch clock發起端,latch的CK端作為capture捕獲端,它們之間天然會存在skew k,即clock tree必然不balance。

- Latch的時序檢查只有半個時鐘周期;

- register Q到Latch EN的combo邏輯延遲;

解決辦法:

- 一般將clock gate 單元放在寄存器附近以減小skew。

- 也可以采用set_clock_gating_check,加大對clock gating時序約束。

對于clock gating cell,synthesis時就會插入,和CTS沒太大關系,一般只要確保clock timing check打開的就行。

另外,CTS工具會對其做clone、declone操作。

- ICG cell Clone: 同一個ICG單元控制的寄存器較多或者分布不均勻時,就會導致ICG時鐘連線過長,可通過clone ICG cell進行優化;

- ICG cell De-Clone: 同一個ICG單元控制的寄存器較少,導致ICG cell數量過多,可通過De-clone ICG cell進行優化;

-

寄存器

+關注

關注

31文章

5425瀏覽量

123549 -

鎖存器

+關注

關注

8文章

923瀏覽量

42154 -

RTL

+關注

關注

1文章

388瀏覽量

60737 -

DFT

+關注

關注

2文章

233瀏覽量

23262 -

門控時鐘

+關注

關注

0文章

27瀏覽量

9083

發布評論請先 登錄

低功耗之門控時鐘設計

低功耗之門控時鐘設計

評論