FPGA的設(shè)計流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態(tài)時序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計的流程圖。

1、HDL代碼編寫

行為語言是目前使用較多的高層硬件描述語言,主要有VHDL和Verilog HDL兩個IEEE標準。在使用黑金FPGA開發(fā)板進行學習的過程中使用較多的是HDL。其突出優(yōu)點有:語言與工藝的無關(guān)性;語言的公開可利用性;具有很強的邏輯描述和仿真功能,且輸入效率高;在不同的設(shè)計輸入庫之間轉(zhuǎn)換方便。

之后進行功能仿真是在編譯之前對用戶所設(shè)計的電路進行邏輯功能驗證,此時的仿真沒有延時信息只對初步的功能進行檢測。

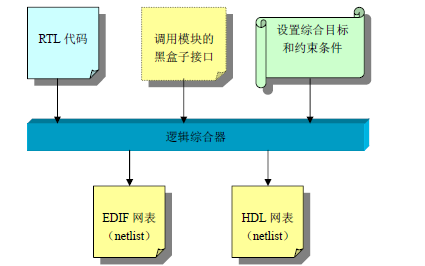

2、RTL綜合

將模塊化層次化設(shè)計的多個文件合并為一個網(wǎng)表,使設(shè)計層次平面化。

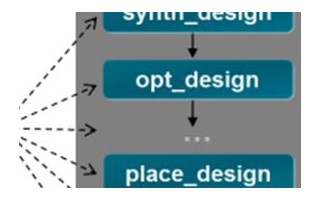

3、布局布線

將已經(jīng)分割的邏輯小塊放到器件內(nèi)部邏輯資源的具體位置并利用布線資源完成各個功能塊之間的連接。

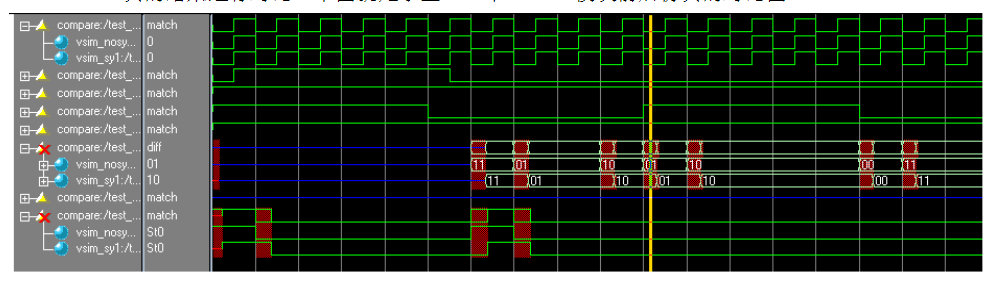

4、靜態(tài)時序分析

靜態(tài)時序分析主要進行時序仿真,它又稱為后仿真或者延時仿真。由于不同器件的內(nèi)部延時不一樣,不同的布局布線方案也會影響延時。因此需要在設(shè)計過程中進行時序仿真,分析其時序關(guān)系,估計設(shè)計的性能,以及檢查和消除競爭冒險等是非常有必要的。

5、生成下載文件

在時序仿真完成之后產(chǎn)生可供器件編程的位流數(shù)據(jù)文件,然后將編程數(shù)據(jù)寫入到器件中。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614669 -

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

27180 -

HDL

+關(guān)注

關(guān)注

8文章

330瀏覽量

47850

發(fā)布評論請先 登錄

如何利用Tcl在Vivado中實現(xiàn)定制化的FPGA設(shè)計流程?

華為FPGA設(shè)計流程指南

華為FPGA設(shè)計流程指南

FPGA的設(shè)計流程是怎樣的

從賽靈思FPGA設(shè)計流程看懂FPGA設(shè)計

FPGA設(shè)計流程“又臭又長”?從eda工具理解超級簡單!

FPGA的設(shè)計流程是怎么樣的?FPGA設(shè)計流程指南詳細資料免費下載

FPGA設(shè)計流程

FPGA設(shè)計流程

評論