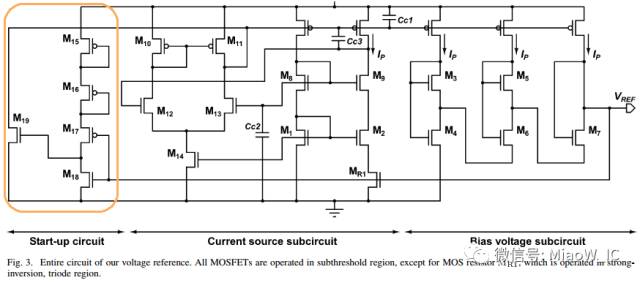

1.2009 A 300 nW, 15 ppm/ C, 20ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs

2. 2004 TOWARDS A SUB-1 V CMOSVOLTAGE REFERENCE

3. 2006us7148672 Low Voltage BANDGAP ReferenceCircuit with Startup Control

4. 2014 a low power CMOS voltage reference generator with temperature and process compensation

5. 2015 A wide temperature range voltage bandgap reference generator in 32nm CMOS technology

6. 2010 low voltage bandgap reference with output regulated current mirror in 90nm CMOS

這里在摘要部分說(shuō)明了“小于1V帶隙基準(zhǔn)面臨的問(wèn)題”,However, these structures have outputvoltage errors due to a mismatchin the temperature dependency of the current in the output current mirrordevice and that of the BGR core, caused by the difference between the drain voltages of these devices . To reduceerrors, the output reference voltage is usually set close to theVBE of the BJT [4]. However, this is not a good solution because theoutput current mirror and output resistor forman open-loop configuration , so that accuracy relies on voltage and layout matching alone . In DSM CMOStechnologies such as 90 nm, the variability of devices becomes more severe andthe changes in temperature dependency of the MOS current caused by changes inthe drain voltage are much bigger than those which occur with long-channeltechnologies. This makes it difficult to obtain an output voltage with anacceptable temperature coefficient using the open-loop mirror structure.

7. 2010 NanoPower CMOS Voltage Reference with Temperature and Process Compensation

這篇文章以前學(xué)習(xí)過(guò)。

8. CN102385405 一種通用的帶隙基準(zhǔn)啟動(dòng)電路

下拉晶體管源極輸出端即為啟動(dòng)電路的啟動(dòng)節(jié)點(diǎn),該啟動(dòng)節(jié)點(diǎn)連接帶隙基準(zhǔn)電路的PMOS電流鏡柵極,啟動(dòng)電路工作時(shí)將帶隙基準(zhǔn)電路中的PMOS電流鏡柵極電平拉低,為三極管充電。用于啟動(dòng)帶隙基準(zhǔn)電路,使帶隙基準(zhǔn)電路脫離錯(cuò)誤工作狀態(tài)。

PMOS管412鏡像帶隙基準(zhǔn)電路的工作電流,NMOS管411鏡像由自由偏置電路41產(chǎn)生的比較基準(zhǔn)電流,412與411漏極連接構(gòu)成電流比較電路。當(dāng)帶隙基準(zhǔn)電路處于錯(cuò)誤兼并點(diǎn)時(shí),412鏡像的帶隙基準(zhǔn)電路支路電流小于411鏡像的比較基準(zhǔn)電流,由于兩管電流應(yīng)保持相等,因此,411管處于深線(xiàn)性區(qū),VX電壓接近地,下拉管413開(kāi)啟,將412柵極也即帶隙基準(zhǔn)電路PMOS電流鏡組柵極電壓拉低,為三極管充電,使帶隙基準(zhǔn)電路脫離錯(cuò)誤兼并點(diǎn),進(jìn)入正確的工作狀態(tài);進(jìn)入正確的工作狀態(tài)后,412管鏡像的帶隙基準(zhǔn)電路工作電流大于411管鏡像的比較基準(zhǔn)電流,因此為保證流過(guò)411管和412管的電流相等,412管進(jìn)入深線(xiàn)性區(qū),VX接近電源電壓,此時(shí)下拉管413關(guān)斷,啟動(dòng)電路不對(duì)正常工作的帶隙基準(zhǔn)電路構(gòu)成影響。

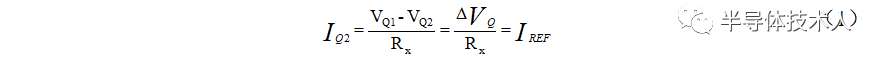

流過(guò)409管的電流為比較基準(zhǔn)電流,設(shè)為Icomp,Icomp滿(mǎn)足下式關(guān)系:

當(dāng)帶隙基準(zhǔn)電路工作在錯(cuò)誤簡(jiǎn)并點(diǎn)時(shí),最大支路電流產(chǎn)生于三極管202導(dǎo)通的臨界狀態(tài),此時(shí)412管鏡像的支路電流IDS,412為

由于NMOS電流鏡411和PMOS電流鏡412中流過(guò)的電流應(yīng)保持相等,均為IDS,412,因此411工作在深線(xiàn)性區(qū),VX~0。下拉晶體管413迅速將電流鏡412管,PMOS管207管、208管和209管的柵極電壓下拉,使得大電流充入帶隙基準(zhǔn)電路的支路,使三極管202和201導(dǎo)通,基準(zhǔn)電路脫離錯(cuò)誤簡(jiǎn)并點(diǎn),其他錯(cuò)誤簡(jiǎn)并點(diǎn)或零簡(jiǎn)并點(diǎn)時(shí)工作原理相同。當(dāng)啟動(dòng)電路進(jìn)入正確工作狀態(tài)后,此時(shí)流過(guò)NMOS電流鏡像管411管的電流為Icomp,而PMOS電流鏡412管鏡像的電流應(yīng)為Inormal,由于

且411管和412管電流應(yīng)保持相等,因此,412管進(jìn)入深線(xiàn)性區(qū),VX~VDD,下拉晶體管413關(guān)閉,啟動(dòng)電路不再對(duì)帶隙基準(zhǔn)電路產(chǎn)生影響。只要帶隙基準(zhǔn)電路進(jìn)入錯(cuò)誤簡(jiǎn)并點(diǎn),啟動(dòng)電路即開(kāi)始工作,直至帶隙基準(zhǔn)電路進(jìn)入正確工作狀態(tài)為止。

圖6為電壓模帶隙基準(zhǔn)電路,只存在一個(gè)錯(cuò)誤簡(jiǎn)并點(diǎn),即零簡(jiǎn)并點(diǎn),此時(shí)比較基準(zhǔn)電流需滿(mǎn)足

本發(fā)明比較基準(zhǔn)電流取值范圍(上限值與下限值之差)為

它是一個(gè)正溫度系數(shù)的PTAT電流,因此,為在所定溫度-40~85范圍內(nèi),實(shí)現(xiàn)比較基準(zhǔn)電流都滿(mǎn)足取值限定條件,偏置電流產(chǎn)生電路42產(chǎn)生的比較基準(zhǔn)電流具有相同的或近似的正溫度系數(shù)

圖4的比較基準(zhǔn)電流為

9. CN101644938A 低電壓帶隙基準(zhǔn)源的安全啟動(dòng)電路

例如,在某工藝下,提供了5V和1.8V電壓下的標(biāo)準(zhǔn)CMOS晶體管。而帶隙基準(zhǔn)源電路由于系統(tǒng)工作需要,要求工作電壓在1.3V~5.5V。由于電路需要工作在5V電壓下,因此必須使用5VCMOS晶體管。而在該CMOS工藝中,P型晶體管的閾值電壓典型值為1.1V。N型晶體管的閾值電壓典型值為0.8V。則在某些情況下,PMOS的閾值電壓幾乎要與電源電壓相等了。這個(gè)時(shí)候,帶隙基準(zhǔn)源的主題電路和啟動(dòng)電路都要求非常嚴(yán)格才能保證在各種工藝下能夠正常啟動(dòng)工作。

電流源電路要在vdd為1.3V正常工作,并保證BGR運(yùn)放正常偏置。

BGR啟動(dòng)電路 ,P管M42相當(dāng)于是電流產(chǎn)生源的鏡像輸出電流,當(dāng)Ibias送入Q3和M30產(chǎn)生了啟動(dòng)電位Vstart,即M32的柵(源)電位,

當(dāng)Vstart-VINN>Vth(M32),則M32會(huì)導(dǎo)通,則VINN將會(huì)被拉高,使Vstart-VINN

一般Ibias電流比Ibgr要小得多,并且可以改變Q3和Q0的個(gè)數(shù)來(lái)調(diào)節(jié),使得正常工作的時(shí)候Vstart電壓小于VINN。圖2中的M32的襯底接地,可以利用晶體管的襯偏效應(yīng)使得正常工作的時(shí)候M32的實(shí)際閾值電壓略高于襯底和源極短接的同樣尺寸的晶體管。因此,該電路既能保證主題電路的正常啟動(dòng),又不會(huì)影響主題電路正常工作時(shí)的特性。

-

三極管

+關(guān)注

關(guān)注

145文章

3654瀏覽量

124063 -

電流鏡

+關(guān)注

關(guān)注

0文章

44瀏覽量

17525 -

晶體管

+關(guān)注

關(guān)注

77文章

9989瀏覽量

140814 -

帶隙基準(zhǔn)電路

+關(guān)注

關(guān)注

0文章

14瀏覽量

10813 -

PMOS管

+關(guān)注

關(guān)注

0文章

84瀏覽量

7019

發(fā)布評(píng)論請(qǐng)先 登錄

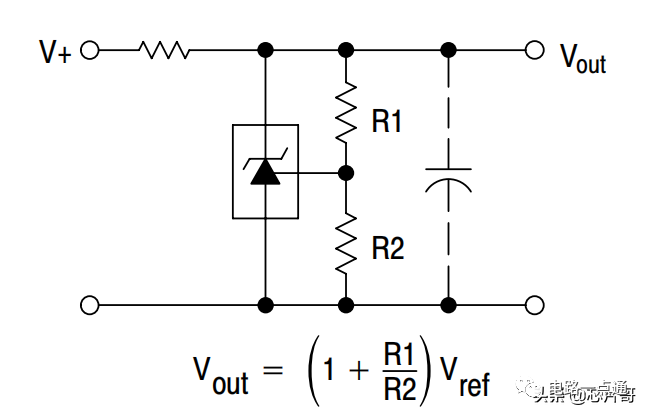

電壓基準(zhǔn)源電路設(shè)計(jì) TL431典型應(yīng)用電路

一種高精度BiCMOS電流模帶隙基準(zhǔn)電路設(shè)計(jì)

基準(zhǔn)電壓源電路設(shè)計(jì)中遇到的挑戰(zhàn)和要求

選擇最佳的電壓基準(zhǔn)源

選擇最佳的電壓基準(zhǔn)源

如何選擇最佳的電壓基準(zhǔn)源

低壓低功耗CMOS帶隙電壓基準(zhǔn)及啟動(dòng)電路設(shè)計(jì)

選擇最佳的電壓基準(zhǔn)源

選擇最佳的電壓基準(zhǔn)源

選擇最佳的電壓基準(zhǔn)源

選擇最佳的電壓基準(zhǔn)源

基于CMOS閾值電壓的基準(zhǔn)電路設(shè)計(jì)

LTC6258LT6656演示電路-適用于小電流啟動(dòng)基準(zhǔn)的低噪聲基準(zhǔn)

用于基準(zhǔn)電壓產(chǎn)生的啟動(dòng)電路設(shè)計(jì)

用于基準(zhǔn)電壓產(chǎn)生的啟動(dòng)電路設(shè)計(jì)

評(píng)論