本文講一下隨路時鐘,什么是隨路的時鐘呢?

第1節 隨路時鐘的概念

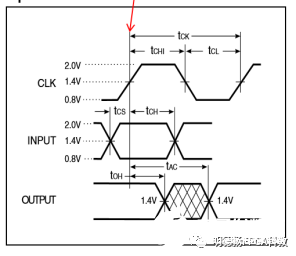

如圖1是一個SDRAM的接口時序圖,大家如果做外部接口,使用過各種芯片,一般也能看到類似這樣接口時序圖。CLK是時鐘信號,INPUT代表輸入SDRAM的各種信號,OUTPUT表示SDRAM輸出的各種信號線。其實芯片接口就是一些寄存器,既然是寄存器,那么這些寄存器想要穩定寄存數據,就會對數據信號有建立時間和保持時間相關的要求。

圖1 SDRAM接口時序圖

如圖1所示,在CLK的上升沿時,要求INPUT必須提前tCS到達,并且延遲tCH,所以該接口寄存器的建立時間為tCS,保持時間為tCH,最后通過數據手冊可以獲取這些參數對應數值。那么在設計時序時就要考慮建立時間和保持時間對數據的影響,即INPUT要在時鐘上升沿的建立時間之前穩定,并且在上升沿之后最少穩定保持時間對應的時間。這是SDRAM的一個接口時序要求,也與多數的芯片接口時序類似。

這是芯片接口需要滿足的時序要求,那我們在做實際項目的時候,如何去滿足這個下游器件的時序要求呢?

第2節 實際應用中,如何做到滿足

2.1建立時間、保持時間的影響因素

那在設計當中如何做才能滿足這個時序要求,首先分析一下影響建立時間和保持時間的因素有哪些呢?

其實影響建立時間、保持時間的因素是很多的,例如說FPGA內部的寄存器傳輸延時、寄存器到管腳的延時和PCB板上的走線延時等等,這些延時最終都會影響時鐘與數據的關系,從而就會影響到下游器件的輸入數據到底能不能滿足芯片接口時序的建立時間和保持時間要求了。

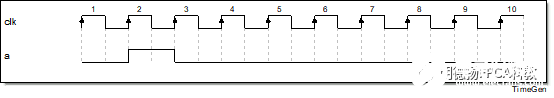

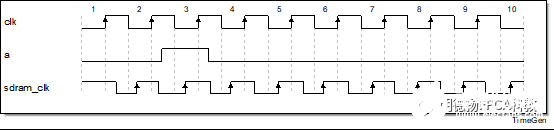

2.1.1 理想波形

如圖2是一個理想的波形,信號a的波形在時鐘的上升沿發生變化,在第2個時鐘上升沿到達時,信號a從低電平變為高電平,在第3個時鐘上升沿到達時,信號a由高電平變為低電平。在兩次變化過程中,沒有任何延遲。能夠在時鐘變化時立即發生相應的變化,這種理想的波形,它的數據會立即到達下一個寄存器,會發現時鐘上升沿之前的時間周期就是時鐘周期T,而且在時鐘上升沿之后穩定的時間是0。由此,很明顯理想觀點是不滿足保持時間要求的。

圖2 理想的時序圖

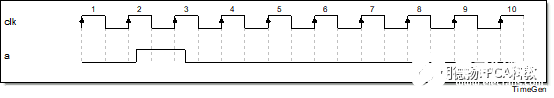

2.1.2 帶有寄存器延時、寄存器到管腳延時的波形

如果信號a在傳輸時經過寄存器延時、寄存器到FPGA管腳的傳輸延遲Tco后,那么可能看到FPGA管腳上出來的信號相位關系就變成如圖3所示。

圖3 引入寄存器延遲和寄存器到管腳延時

clk是時鐘,信號a可能對時鐘會有一定的延時。由圖3中可以看到,信號a會在時鐘的第2個上升沿之后的一段時間才發生變化,這是由于寄存器延時造成的。在時鐘上升沿第3個去采樣時候,才發現信號a會提前時鐘周期T-Tco這么長的時間變為穩定。上升沿之后保持了Tco,有時候延時多久就保持多久,對不對?

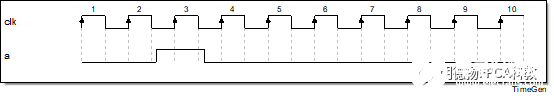

2.1.3 加上走線或其他延時(Tpcb)

實際波形如下:

增加延遲,信號可能會相對時鐘往后延遲,在時鐘上升沿之前的時間會保持多久?在時鐘2時信號a變高,經過寄存器延時(tco)之后,在經過走線延遲等等,信號傳遞時鐘3,因此時鐘上升沿前的時間為(T-tco-tpcb),上升沿后保持的時間為(tco+tpcb)。那這是正常的延時情況。

那么只要滿足T-tco-tpcb這個延時大于建立時間要求,并且tco+tpcb這個延時大于保持時間要求。那電路就是正常的,那如何才能做到這一點呢?但時鐘周期,PCB走線延遲一般都是固定的,對于特定的FPGA芯片,寄存器延遲也是固定的,只有信號從寄存器傳輸到芯片管腳的延遲可以改變。

第3節 兩種有效解決方法

3.1 添加時序約束,設置輸出延時set_output_delay

有兩種做法,一種是添加時序約束,Set output delay。這個約束會告訴綜合軟件下游器件的建立要求是多少和PCB走線延遲是多少,由于時鐘周期和PCB走線延遲是固定的,對于特定的器件,寄存器延時也是固定的,根據T-TCO-TPCB,綜合軟件就會通過調整寄存器到管角的延時,這個延時放大或放小,從而使下游器件能采集到這個數據,滿足下游器件的建立時間和保持性要求。

3.2 添加隨路時鐘

另一種方式添加隨路時鐘,什么是隨路時鐘再看一下。

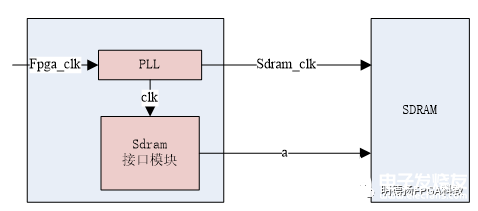

如上圖所示,信號a是在clk時鐘域產生的信號。Sdram_clk是與clk同源、頻率相同、相位不同的時鐘信號。當sdram_clk 輸出作為sdram的工作時鐘,通過調整sdram_clk的相位就能調整時序,從而滿足建立時間和保持時間的要求。假如這是CLK,用PLL產生一個SDRAM的CLK,這兩個CLK的使用頻率是一樣的。比如說一開始有個150M的FPGA時鐘clk ,FPGA的時鐘clk通過PLL產生一個相位有一定偏差的150M時鐘sdram_clk。可以看到clk上升沿的時候,隔了很久,sdram_clk的上升沿才出現,而這兩個時鐘的時鐘頻率一樣、相位不一樣。

那么sdram_clk如何產生呢?可以通過PLL來產生,PLL可以保證頻率相同、相位偏移量,所以該系統的結構如圖:

第一個時鐘clk可能就給Sdram接口模塊作為系統時鐘,sdram_clk直接就給SDRAM芯片作為數據采集的時鐘了,那這樣就有什么后果呢?

由于信號a是在clk時鐘產生的,使得信號a是相對于時鐘clk有一定的延時的。sdram_clk相對時鐘clk有一定延時,有一定項目偏差。只要調整sdram_clk相位,就可以使得信號a在時鐘sdram_clk的上升沿滿足建立時間和保持時間的要求。比如可以調整sdram_clk,讓sdram_clk上升沿剛好在信號a變化的中間。也就是說項目開始可以通過調節鎖相環PLL的sdram_clk相位,使得下游芯片使用sdram_clk的上升沿去采集信號a時,能夠同時滿足建立時間和保持時間要求。只要調整好,那么這個系統就可以正常工作。

Sdram_clk就是隨路時鐘,隨時鐘把數據一起送到下游芯片。通過調整Sdram_clk相位,讓接口信號和時鐘滿足下游接口芯片的建立時間和保持時間要求,這就是隨路時鐘的方法。

第4節 兩種方法優缺點及取舍

4.1 第一種方法優缺點

那這種方法有什么優缺點,如何取舍,第一點就是常規做法,就是一個時序約束的做法。產生兩個時鐘,但調試還是比較麻煩的。并且有一點就是我們用的時間,對不對?它是有時間有限度的,因為調整是TCO,它一定是有限度的,就是任意調都可以是吧?比如說是調不了的,這時候就需要用Sdram_clk隨路時鐘的方法去做了。

4.2 第二種方法優缺點

隨路時鐘調試起來簡單,PLL設置簡單,出錯可能性小。不斷的調整相位,總能找到一個點讓時序滿足。但是也明顯的,需要有個PLL來產生這個時鐘,會消耗鎖相環硬件資源。如果使用這種方法,就不用設置output delay之類的約束,直接用調整相位方式找到同時滿足建立時間和保持時間要求的點就ok 了,所以隨路時鐘這種方法很多項目都喜歡用。

第5節 接收方向

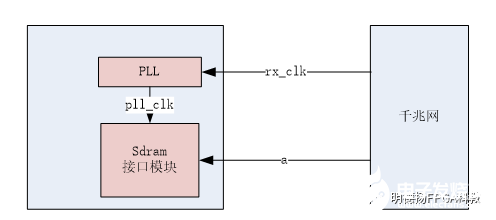

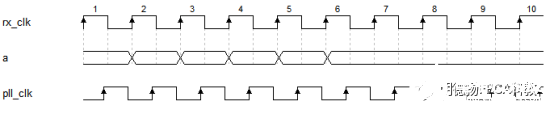

SDRAM是TX(輸出)方向的,輸入方向是同樣的道理。比如說千兆網模塊就是接收數據的,如下圖所示。

它有個時鐘rx_clk,假設信號a為輸入數據,時鐘信號與數據a對齊。這個時候如果我直接用rx_clk去采集信號a,可能就就不滿足了寄存器的建立時間和保持時間了,那怎么辦呢?以下兩種方法:此時就可以時鐘信號,

5.1 方法1

設置輸入延時set_input_delay。FPGA根據時序情況,增加寄存器延時、時鐘延時等,從而滿足FPGA本身的建立時間和保持時間要求。比如說set input delay,FPGA 根據調整,去增加寄存器延時等方式,來滿足自身建立時間和保持要求。

5.2 方法2

另一種方式也可以跟SDRAM一樣,用rx clk通過鎖相環生成一個與rx_clk頻率相同,相位不同的pll_clk作為千兆網接口模塊的時鐘信號。用pll_clk去采集信號a的數據,這樣不斷調整pll_clk相位,使得pll_clk時鐘上升沿位于信號a中間,此時就可能滿足寄存器建立時間和保持時間要求了。這個時候就不用設input delay 了,就不用設時序約束了,這個時候就ok 了。所以這種方法特別是做接口調試的時候特別有用。像千兆網、SDRAM、DDR2這種東西,全部都可以用這種方式去做。

要注意的是由于這種方式,使用了一個鎖相環PLL的,鎖相環PLL對其輸入時鐘是有要求的,要求輸入的時鐘必須來自于FPGA芯片的時鐘管腳,否則綜合軟件會報錯,這是唯一的要求。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21979瀏覽量

614477 -

寄存器

+關注

關注

31文章

5424瀏覽量

123477 -

時鐘

+關注

關注

11文章

1886瀏覽量

132877 -

時序約束

+關注

關注

1文章

118瀏覽量

13633

發布評論請先 登錄

FPGA主時鐘約束詳解 Vivado添加時序約束方法

時序約束連載04~隨路時鐘

時序約束連載04~隨路時鐘

評論