1.1? 概述

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

1.2? FPGA整體概念

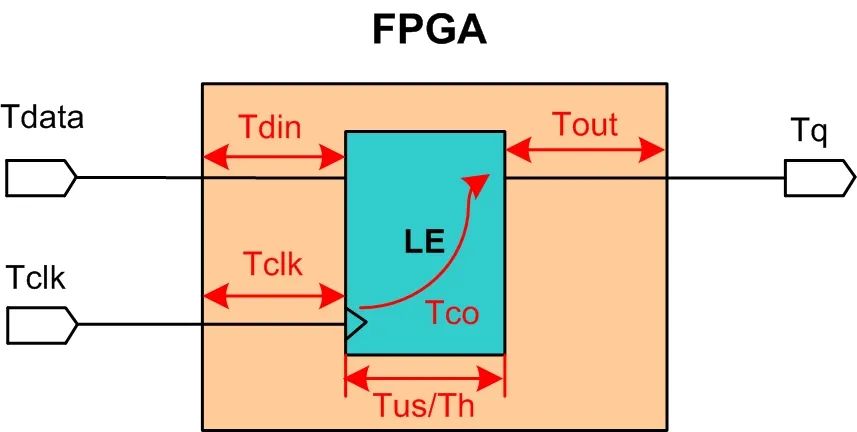

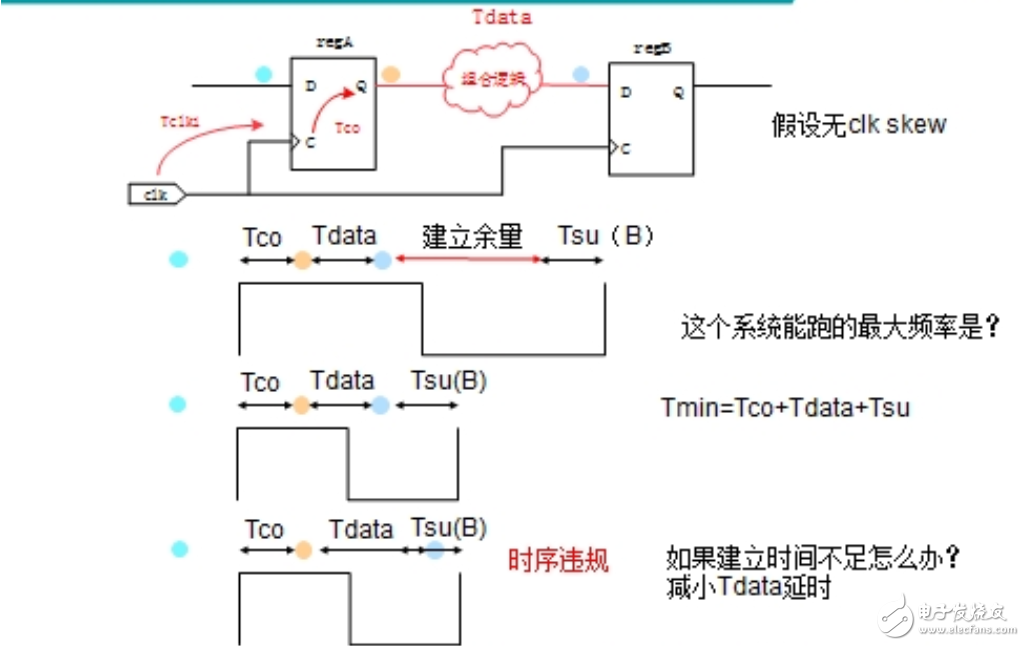

由于IO口時序約束分析是針對于電路板整個系統進行時序分析,所以FPGA需要作為一個整體分析,其中包括FPGA的建立時間、保持時間以及傳輸延時。傳統的建立時間、保持時間以及傳輸延時都是針對寄存器形式的分析。但是針對整個系統FPGA的建立時間保持時間可以簡化。

?

圖1.1? FPGA整體時序圖

如圖1.1所示,為分解的FPGA內部寄存器的性能參數:

(1) Tdin為從FPGA的IO口到FPGA內部寄存器輸入端的延時;

(2) Tclk為從FPGA的IO口到FPGA內部寄存器時鐘端的延時;

(3) Tus/Th為FPGA內部寄存器的建立時間和保持時間;

(4) Tco為FPGA內部寄存器傳輸時間;

(5) Tout為從FPGA寄存器輸出到IO口輸出的延時;

對于整個FPGA系統分析,可以重新定義這些參數:FPGA建立時間可以定義為:

(1) FPGA建立時間:FTsu = Tdin + Tsu – Tclk;

(2) FPGA保持時間:FTh = Th + Tclk;

(3) FPGA數據傳輸時間:FTco = Tclk + Tco + Tout;

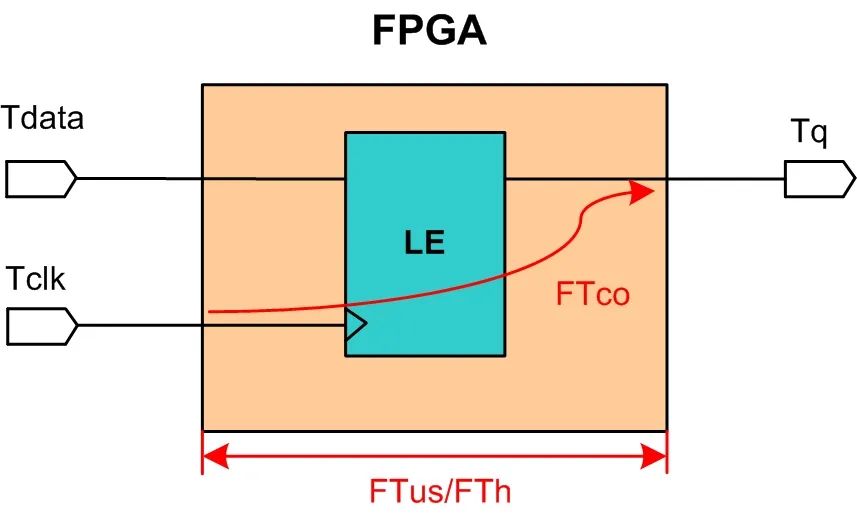

由上分析當FPGA成為一個系統后即可進行IO時序分析了。FPGA模型變為如圖1.2所示。

?

圖1.2? FPGA系統參數

1.3? 輸入最大最小延時

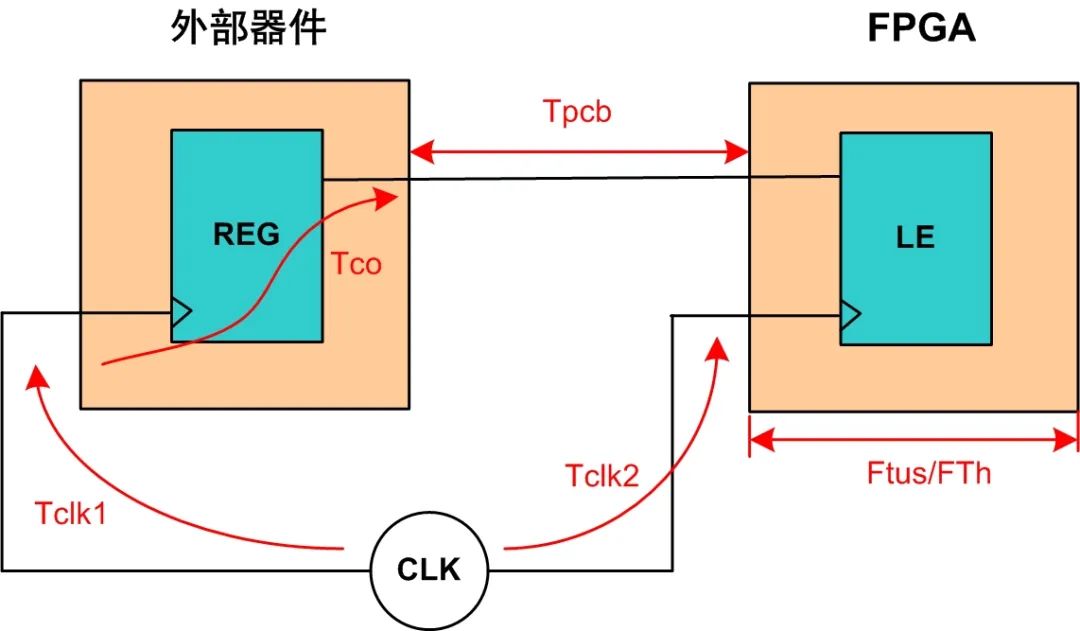

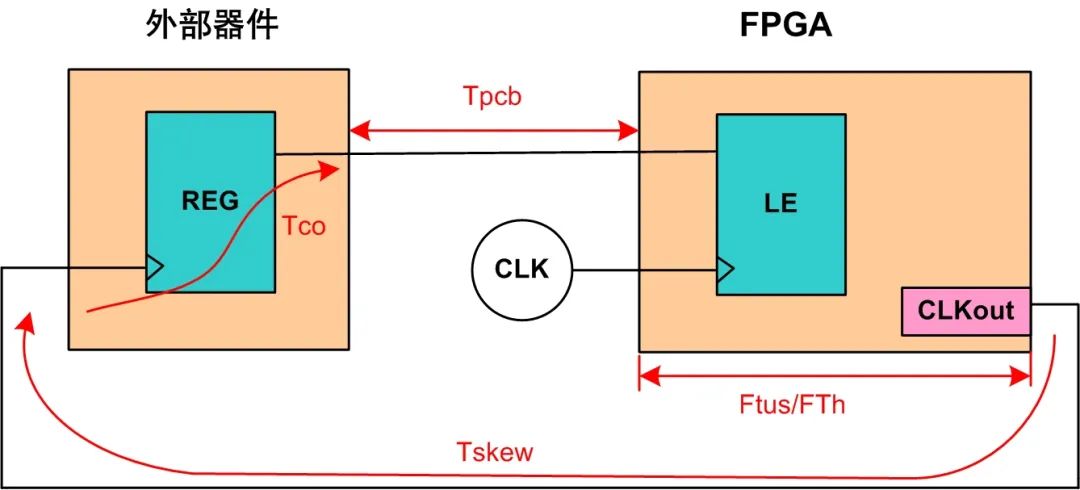

外部器件發送數據到FPGA系統模型如圖1.3所示。對FPGA的IO口進行輸入最大最小延時約束是為了讓FPGA設計工具能夠盡可能的優化從輸入端口到第一級寄存器之間的路徑延遲,使其能夠保證系統時鐘可靠的采到從外部芯片到FPGA的信號。

圖1.3? FPGA數據輸入模型

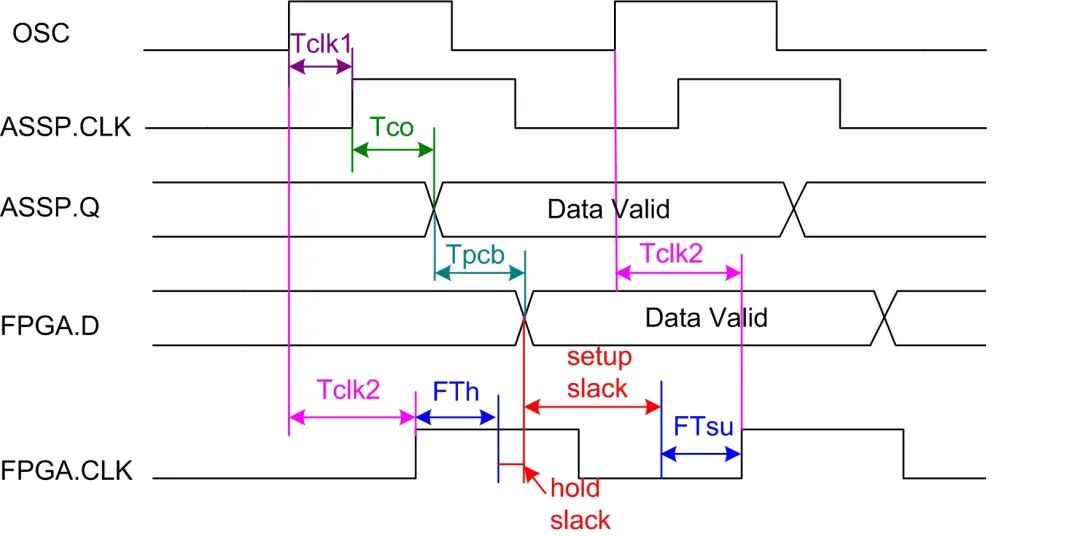

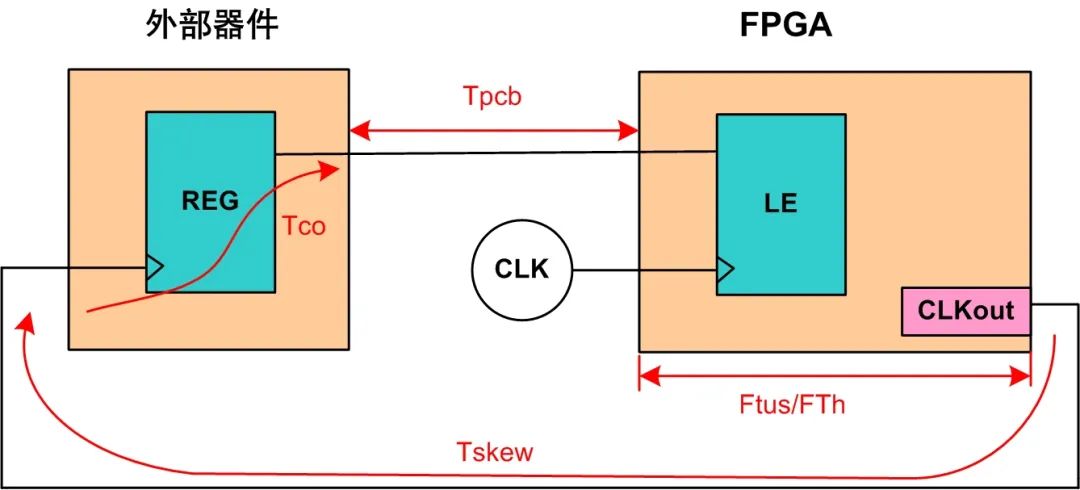

輸入延時即為從外部器件發出數據到FPGA輸入端口的延時時間。其中包括時鐘源到FPGA延時和到外部器件延時之差、經過外部器件的數據發送Tco,再加上PCB板上的走線延時。如圖1.4所示,為外部器件和FPGA接口時序。

?

圖1.4? 外部器件和FPGA接口時序

1.???????? 最大輸入延時

最大輸入延時(input delay max)為當從數據發送時鐘沿(lanuch edge)經過最大外部器件時鐘偏斜(Tclk1),最大的器件數據輸出延時(Tco),再加上最大的PCB走線延時(Tpcb),減去最小的FPGA時鐘偏移(FTsu)的情況下還能保證時序滿足的延時。這樣才能保證FPGA的建立時間,準確采集到本次數據值,即為setup slack必須為正,如圖1.1的所示,計算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max)?+Tco(max)?+Tpcb(max)?+FTsu)≥0

推出如下公式:

Tclk1(max)?+ Tco(max)?+ Tpcb(max)?–Tclk2(min)?≤ Tclk + FTsu?????????

由Altera官方數據手冊得知:

input delay max = Board Delay?(max)?– Board clock skew?(min)?+ Tco(max)?????

結合本系統參數公式為:

input delay max = Tpcb(max)?– (Tclk2(min)–Tclk1(max)) + Tco(max)?????????

2.???????? 最小輸入延時

最小輸入延時(input delay min)為當從數據發送時鐘沿(lanuch edge)經過最小外部器件時鐘偏斜(Tclk1),最小器件數據輸出延時(Tco),再加上最小PCB走線延時(Tpcb),此時的時間總延時值一定要大于FPGA的最大時鐘延時和建立時間之和,這樣才能不破壞FPGA上一次數據的保持時間,即為hold slack必須為正,如圖1.1的所示,計算公式如下式所示:

Hold slack = (Tclk1(min)?+ Tco(min)?+ Tpcb(min))–(FTh + Tclk2(max))≥ 0??

推出如下公式:

Tclk1(min)?+ Tco(min)?+ Tpcb(min)?– Tclk2(max)?≥ FTh???????????????????????????????

由Altera官方數據手冊得知:

input delay max = Board Delay?(min)?- Board clock skew?(min)?+ Tco(min)????????

結合本系統參數公式為

input delay max = Tpcb(min)?– (Tclk2(max)–Tclk1(min)) + Tco(min)??????????????????

由公式4和公式8得知,進行輸入最大最小延時的計算,我們需要估算4個值:

(1) 外部器件輸出數據通過PCB板到達FPGA端口的最大值和最小值Tpcb,PCB延時經驗值為600mil/ns,1mm = 39.37mil;

(2)?外部器件接收到時鐘信號后輸出數據延時的最大值和最小值Tco;

(3) 時鐘源到達外部器件的最大、最小時鐘偏斜Tclk1;

(4) 時鐘源到達FPGA的最大、最小時鐘偏斜Tclk2;

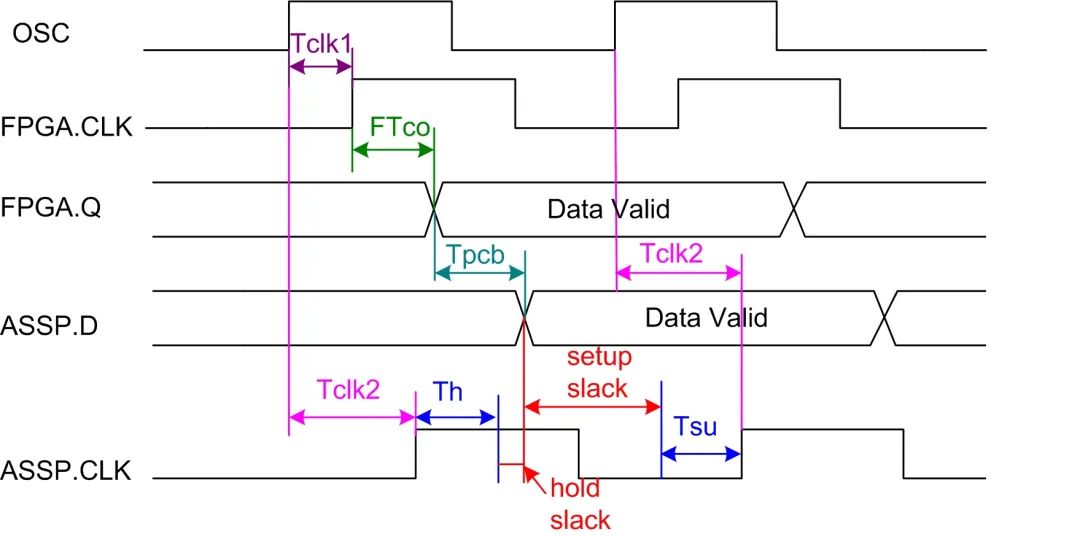

當外部器件時鐘為FPGA提供的時候,Tclk1和Tclk2即合成Tshew,如圖1.5所示:

?

圖1.5? FPGA輸出時鐘模型

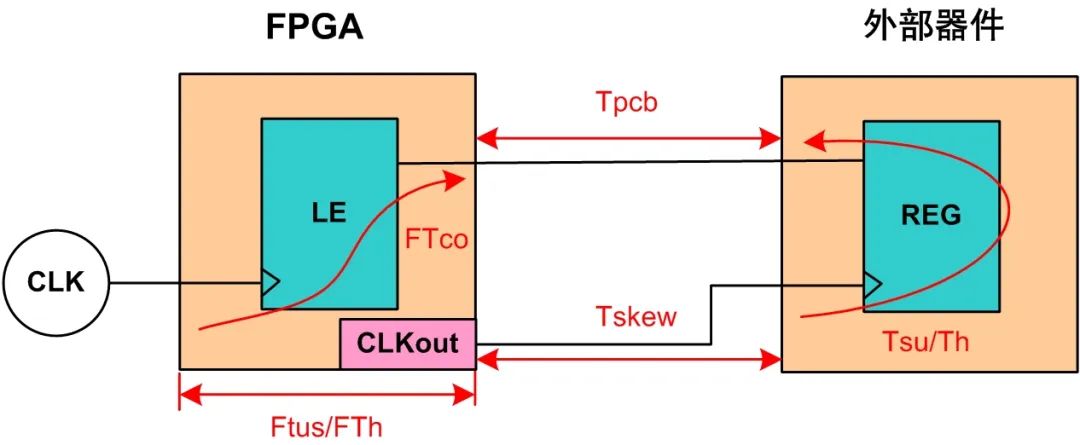

1.4? 輸出最大最小延時

FPGA輸出數據給外部器件模型如圖1.6所示。對FPGA的IO口進行輸出最大最小延時約束是為了讓FPGA設計工具能夠盡可能的優化從第一級寄存器到輸出端口之間的路徑延遲,使其能夠保證讓外部器件能準確的采集到FPGA的輸出數據。

圖1.6? FPGA輸出延時模型

輸出延時即為從FPGA輸出數據后到達外部器件的延時時間。其中包括時鐘源到FPGA延時和到外部器件延時之差、PCB板上的走線延時以及外部器件的數據建立和保持時間。如所示,為FPGA和外部器件接口時序圖。

?

圖1.7? FPGA輸出延時

1.???????? 最大輸出延時

由Altera官方數據手冊得知:

Output delay max = Board Delay (max) – Board clock skew (min) + Tsu???????

由公式得知,最大輸出延時(output delay max)為當從FPGA數據發出后經過最大的PCB延時、最小的FPGA和器件時鐘偏斜,再加上外部器件的建立時間。約束最大輸出延時,是為了約束IO口輸出,從而使外部器件的數據建立時間,即為setup slack必須為正,計算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max)?+FTco(max)?+Tpcb(max)?+Tsu)≥0

推導出如下公式:

FTco(max)?+ Tpcb(max)?–(Tclk2(min)?– Tclk1(max))+Tsu ≤Tclk?????????????????

再次推導,得到如下公式:

FTco(max)?+ Output delay max ≤Tclk?????????????????????

由此可見,約束輸出最大延時,即為通知編譯器FPGA的FTco最大值為多少,根據這個值做出正確的綜合結果。

2. ?輸出最小延時

由Altera官方數據手冊得知:

Output delay min = Board Delay (min) – Board clock skew (max) –Th????????

由公式得知,最小輸出延時(output delay min)為當從FPGA數據發出后經過最小的PCB延時、最大的FPGA和器件時鐘偏斜,再減去外部器件的建立時間。約束最小輸出延時,是為了約束IO口輸出,從而使IO口輸出有個最小延時值,防止輸出過快,破壞了外部器件上一個時鐘的數據保持時間,導致hlod slack為負值,不能正確的鎖存到數據,最小輸出延時的推導計算公式如下式所示:

Hold slack = (Tclk1(min)?+ FTco(min)?+ Tpcb(min))–(Th + Tclk2(max))≥ 0?

推導出如下公式:

FTco(min)?+ Tpcb(min)?– (Tclk2(max)?– Tclk1(min))– Th ≥ 0????

再次推導,得出如下公式:

FTco(min)?+ Output delay min ≥ 0????????????????????

由公式得知,約束輸出最大延時,即為通知編譯器FPGA的FTco最小值為多少,根據這個值做出正確的綜合結果。

由公式10和公式14得知,進行輸出最大最小延時的計算,我們需要估算4個值:

(1) FPGA輸出數據通過PCB板到達外部器件輸入端口的最大值和最小值Tpcb,PCB延時經驗值為600mil/ns,1mm = 39.37mil;

(2) 時鐘源到達外部器件的最大、最小時鐘偏斜Tclk2;

(3)?時鐘源到達FPGA的最大、最小時鐘偏斜Tclk1;

(4)?外部器件的建立時間Tsu和保持時間Th;

當外部器件時鐘為FPGA提供的時候,Tclk1和Tclk2即合成Tshew,如圖1.8所示:

圖1.8? FPGA提供時鐘模型

1.5? 使用范圍

通過作者使用總結情況,IO口時序約束主要使用在以下情況:

1.???????? 數據交換頻率較高

由于IO時序約束一般計算值都是在幾納秒,當FPGA和外部數據交換頻率較低,如FPGA操作640*480的TFT液晶進行刷屏,數據傳輸頻率僅僅24Mhz,一個數據時鐘都有41.666ns,完全不用約束都能滿足時序要求。但是當操作SDRAM運行到120M時候,由于一個數據變換周期才8ns,因此IO口的少量延時都會影響到SDRAM數據,因此這種情況下需要對輸入輸出進行完整的IO口時序約束,并且分析正確,才能消除數據傳輸不穩定過的情況。

2.???????? 代碼已經比較優化

當數據交換頻率較高,但是時序約束還是不滿足時序要求的時候,我們都需要對代碼進行分析,好的時序都是設計出來的,不是約束出來的。如程序清單 1.1所示,首先hcount_r 和vcount_r 都為10位計數器,這樣的代碼TFT的三色輸出的端口就會有很大的延時,因為dat_act的膠合邏輯太多,輸出路徑太長導致。這種情況下應該不是首先做時序約束,應該修改代碼,盡量做到寄存器直接輸出。只有當代碼比較優化的情況,再做時序約束這樣才能得到較好的結果。

程序清單 1.1? 示例程序

1 assign dat_act = ((hcount_r >= hdat_begin) && (hcount_r < hdat_end))

2 && ((vcount_r >= vdat_begin) && (vcount_r < vdat_end));

3 assign tft_r = (dat_act) ? {rgb16_dat[15:11], 3'b111} : 8'h00;

4 assign tft_g = (dat_act) ? {rgb16_dat[10:5], 3'b111} : 8'h00;

5 assign tft_b = (dat_act) ? {rgb16_dat[4:0], 3'b111} : 8'h00;

1.6? 總結

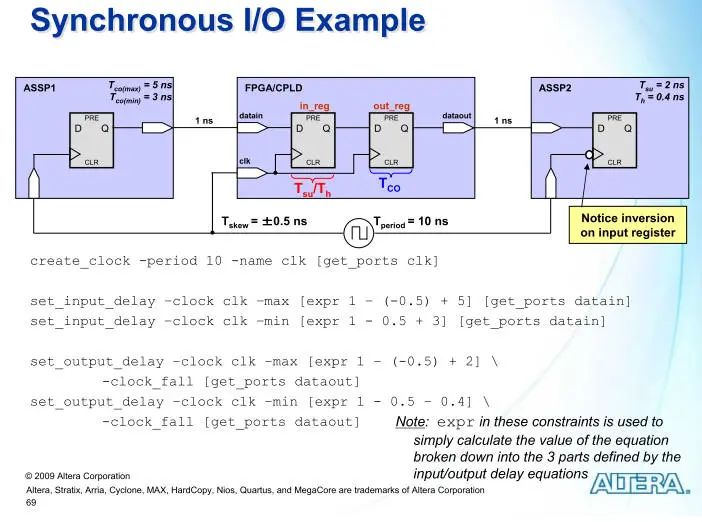

本文檔主要是對FPGA的IO口時序約束進行相應的分析,并未做實際的使用分析,在后續文檔中將會結合軟件,以及實際案例對IO口時序約束進行詳細的使用介紹。最后附上一個Altera官方的IO時序約束分析例子,如圖1.9所示。

?

?

審核編輯:湯梓紅

? 電子發燒友App

電子發燒友App

評論