在給FPGA做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在FPGA設計工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯

2023-10-12 12:00:02 866

866

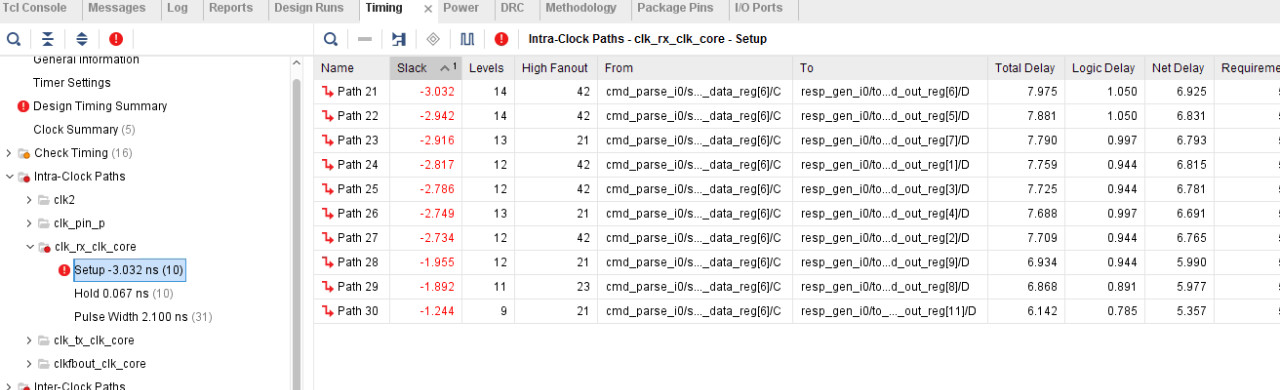

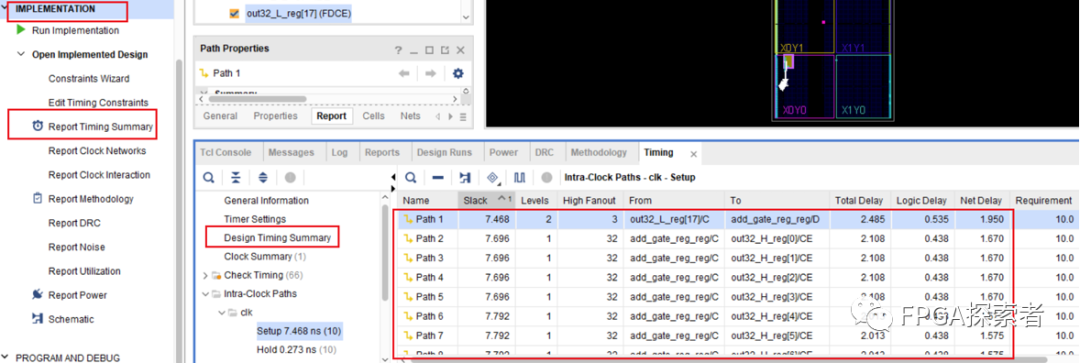

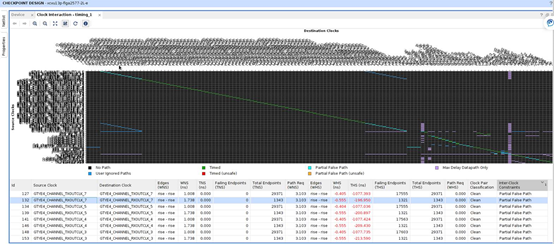

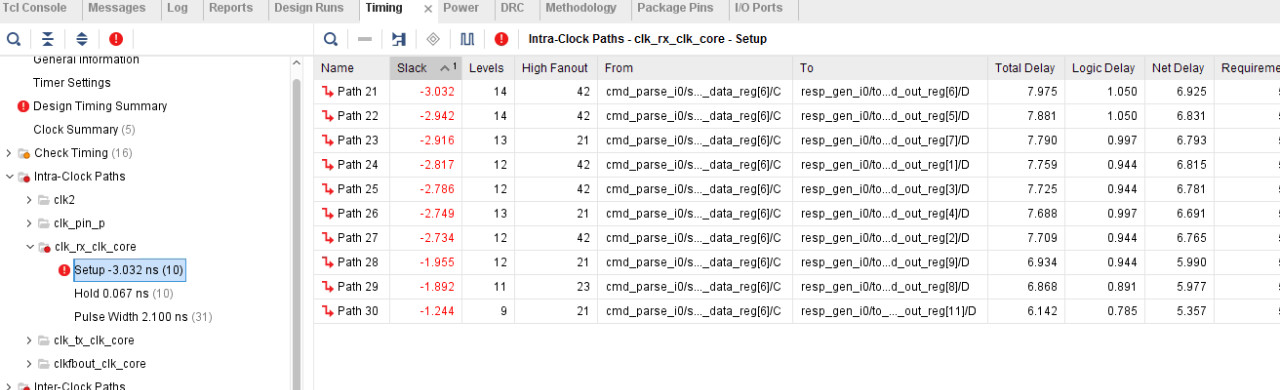

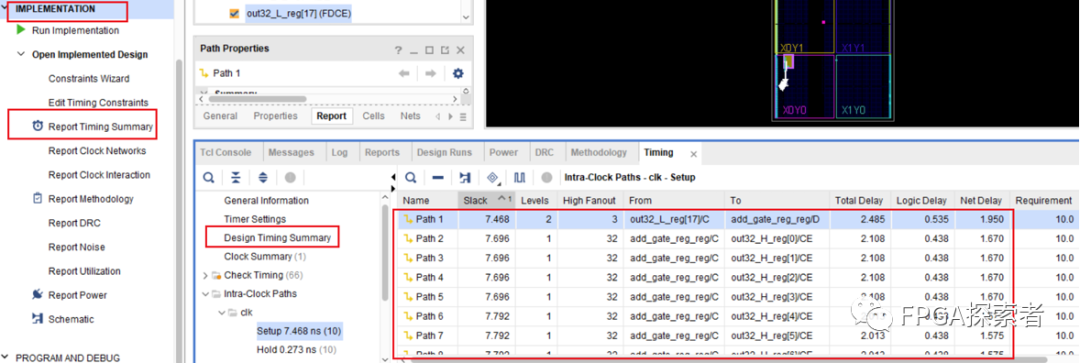

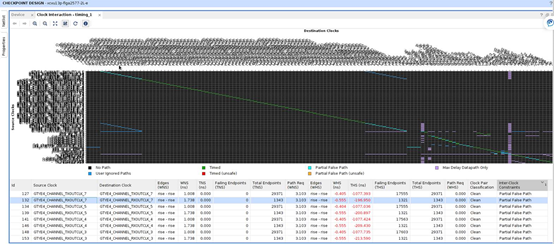

首先來看帶有使能的數據,在本工程中的Tming Report中,也提示了同一個時鐘域之間的幾個路徑建立時間不滿足要求

2020-11-14 11:13:12 4986

4986

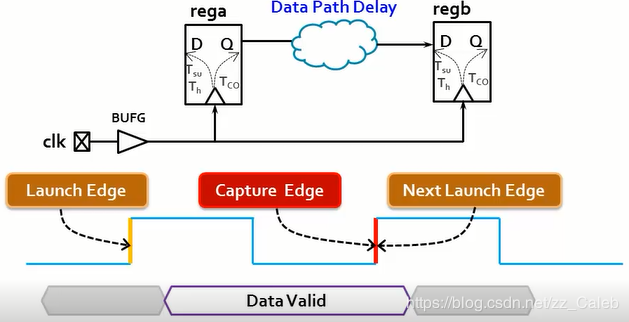

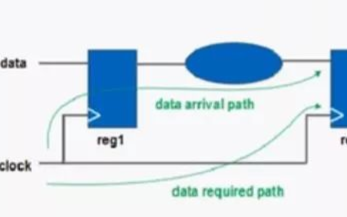

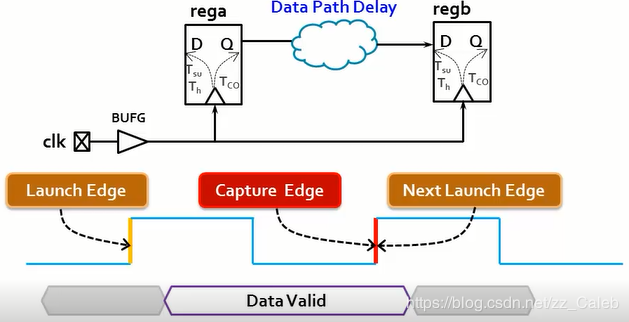

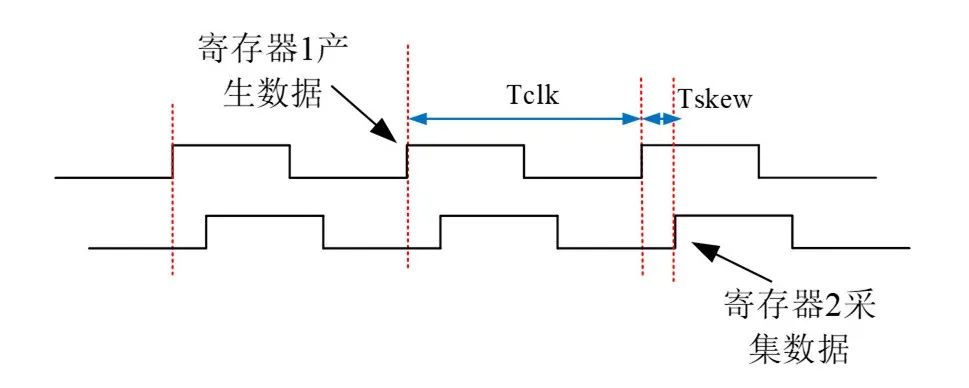

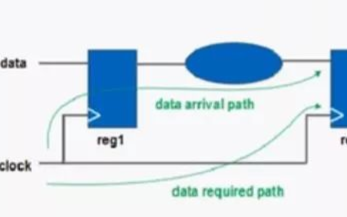

表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 2768

2768

邊沿。 ④ 通常情況下這兩個邊沿會有一個時鐘周期的差別。 2、時序路徑 (Timing path典型時序路徑有四種) ① ② 第一類時序路徑(紅色) - 從device A的時鐘到FPGA的第一

2020-11-25 15:27:21 8566

8566

時序不滿足約束,會導致以下問題: 編譯時間長的令人絕望 運行結果靠運氣時對時錯 導致時序問題的成因及其發生的概率如下表: 由上表可見,造成時序問題的主要原因除了約束不完整,就是路徑問題,本文就時序

2020-11-29 10:34:00 7410

7410 跨時鐘域路徑分析報告分析從一個時鐘域(源時鐘)跨越到另一個時鐘域(目標時鐘)的時序路徑。

2020-11-27 11:11:39 5449

5449

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 6213

6213

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

1230 關鍵路徑通常是指同步邏輯電路中,組合邏輯時延最大的路徑(這里我認為還需要加上布線的延遲),也就是說關鍵路徑是對設計性能起決定性影響的時序路徑。

2023-06-21 14:14:16 1220

1220

reg2reg路徑約束的對象是源寄存器(時序路徑的起點)和目的寄存器(時序路徑的終點)都在FPGA內部的路徑。

2023-06-26 14:28:01 604

604

同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。

2023-06-28 09:35:37 490

490

時序路徑作為時序約束和時序分析的物理連接關系,可分為片間路徑和片內路徑。

2023-08-14 17:50:02 452

452

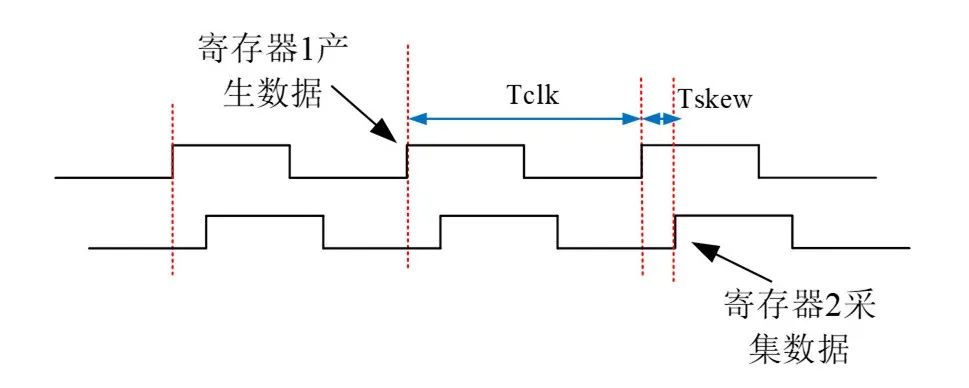

針對第2章節時序路徑中用到skew,在本章再仔細講解一下。

2023-08-14 17:50:58 548

548

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

時鐘周期約束是用于對時鐘周期的約束,屬于時序約束中最重要的約束之一。

2023-08-14 18:25:51 472

472 在輸入信號到輸出信號中,因為經過的傳輸路徑、寄存器、門電路等器件的時間,這個時間就是時序。開發工具不知道我們路徑上的要求,我們通過時序約束來告訴開發工具,根據要求,重新規劃,從而實現我們的時序要求,達到時序的收斂。

2019-07-31 14:50:41 6185

6185

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

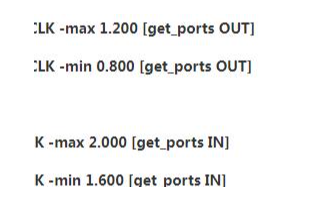

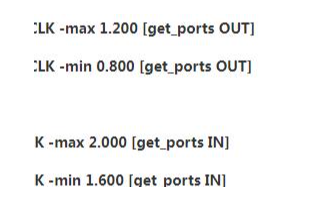

FPGA時序約束,總體來分可以分為3類,輸入時序約束,輸出時序約束,和寄存器到寄存器路徑的約束。其中輸入時序約束主要指的是從FPGA引腳輸入的時鐘和輸入的數據直接的約束。共分為兩大類:1、源同步系統

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束

2016-06-02 15:54:04

不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束+時序例外約束+I/O約束 I/O約束包括引腳分配位置、空閑引腳驅動方式、外部走線延時

2017-12-27 09:15:17

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數據和時鐘傳輸路徑是由相應的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

FPGA畢竟不是ASIC,對時序收斂的要求更加嚴格,本文主要介紹本人在工程中學習到的各種時序約束技巧。 首先強烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒有之一。它提倡

2020-12-23 17:42:10

時序違規情況如果我們按照實際的需求對FPGA進行如下的時序約束:din1 < 10ns, din2 < 10ns, din3 < 20ns, din4 < 20ns。接下來,如圖

2015-07-14 11:06:10

,他們共用一個時鐘(當然也有不共用一個時鐘的reg2reg路徑,這種路徑的分析會復雜一些,這里不做深入討論)。對于reg2reg路徑,我們只要告訴FPGA的時序設計工具他們的時鐘頻率(或時鐘周期),那么

2015-07-20 14:52:19

reg2reg路徑的時序分析本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 我們可以先重點研究一下

2015-07-24 12:03:37

VGA驅動接口時序設計之3時鐘約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 如圖8.26所示

2015-07-30 22:07:42

的約束,來控制這些內部的時序延時,使得前面給出的兩個基本公式得到滿足。但是,FPGA并不知道這兩個公式中FPGA外部的路徑延時參數,所以我們下一步的數據路徑約束要做的就是把這些參數告訴FPGA

2015-08-02 19:26:19

VGA驅動接口時序設計之6建立和保持時間約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 接著,我們可以

2015-08-06 21:49:33

的時序路徑分析。(特權同學,版權所有)CMOS Sensor接口相對于FPGA來說是不折不扣的pin2reg所覆蓋的約束類型。在開始這個CMOS Sensor的時序約束前,我們先來進一步認識一下

2015-08-12 12:42:14

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

一組合電路,從Trig_sig輸入一個上升沿觸發信號,這個信號分別通過兩條路徑:路徑1(path_1[0]到path_1[64])和路徑2(path_2[0]到path_2[64])。希望約束路徑1和路徑2的延時差絕對值盡量小(即約束路徑1和路徑2的延時相等),如何做? 謝謝!

2013-12-30 15:12:19

的一條或多條路徑。在 FPGA 設計中主要有四種類型的時序約束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)約束。賽靈思FPGA設計時序約束指南[hide][/hide]`

2012-03-01 15:08:40

,因此,為了避免這種情況,必須對fpga資源布局布線進行時序約束以滿足設計要求。因為時鐘周期是預先知道的,而觸發器之間的延時是未知的(兩個觸發器之間的延時等于一個時鐘周期),所以得通過約束來控制觸發器之間的延時。當延時小于一個時鐘周期的時候,設計的邏輯才能穩定工作,反之,代碼會跑飛。

2018-08-29 09:34:47

當邏輯行為以默認的方式不能正確的定時邏輯行為,想以不同的方式處理時序時,必須使用時序例外命令。1. 多周期路徑約束指明將數據從路徑開始傳播到路徑結束時,所需要的時鐘周期

2018-09-21 12:55:34

的延時指的是任意兩個相鄰的寄存器之間的最長的組合邏輯延時,也就是關鍵路徑的延時。當然,組合邏輯的延時也不能無限短,必須要滿足公式(2) 的要求。 三、在FPGA中對時序進行約束在FPGA設計中,時序

2020-08-16 07:25:02

時序約束可以很復雜,這里我們先介紹基本的時序路徑約束,復雜的時序約束我們將在后面進行介紹。在本節的主要內容如下所示:·時序路徑和關鍵路徑的介紹 ·建立時間、保持時間簡述 ·時鐘的約束(寄存器-寄存器之間的路徑約束) ·輸入延時的約束 ·輸出延...

2021-07-26 08:11:30

各位大俠,能否分享一下找到影響時序的關鍵路徑的一些經驗

2014-02-27 11:17:52

TS_FastPath = FROM clk_a TO clk_b 20 ns;而我們的違規路徑多是從某個模塊下的寄存器到另一個模塊下的寄存器,時序分析報告中會給出具體的路徑。在QII中可以針對這條路徑進行多周期約束

2015-04-30 09:52:05

滿足vlx760 fpga的時序要求。將偏移輸入/輸出約束添加到vlx760 fpga-IN ANY WAY- 幫助滿足125MHz周期約束?幫幫我 !!! :)?。以上來自于谷歌翻譯以下為原文hi

2019-04-08 10:27:05

在給 FPGA 做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在 FPGA 中都包含有4 種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入 到輸出的純組合邏輯

2012-03-05 15:02:22

大部分的時序分析和約束都寫在這里了。 一、基本時序路徑1、clock-to-setup周期約束跨時鐘域約束: (1)當源觸發器和目標觸發器的驅動時鐘不同,且時鐘的占空比不是50

2017-03-09 14:43:24

SDR和DDR兩場景,而DDR又可再細分成邊沿對齊和中心對齊。以上每種情況,其約束語句、獲取參數的方法都是不一樣的。想知道具體情況,歡迎觀看本節視頻。05 時序例外約束本節視頻講述多周期路徑、異步時鐘以及

2017-06-14 15:42:26

小技巧和幫助來設置時鐘;使用像Synopsys Synplify Premier一樣的工具正確地設置時序約束;然后調整參數使之滿足賽靈思FPGA設計性能的目標。 會有來自不同角度的挑戰,包括:更好

2019-08-11 08:30:00

、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。2. 核心頻率約束+時序例外約束+I/O約束 I/O

2017-10-20 13:26:35

高速到低速上圖給定的條件:高速時鐘到低速時鐘兩個時鐘有2ns的offset源端時鐘是目的端時鐘頻率兩倍如果不使用多周期約束,quartus II的時序分析工具將按照數據建立時間setup time

2015-03-17 17:43:52

什么是時序路徑和關鍵路徑?常見的時序路徑約束有哪些?

2021-09-28 08:13:15

約束報告找到相關路徑。看是什么原因導致的違規。違規的原因有可能是路徑本身需要多周期約束,或者程序代碼if嵌套太多,判斷條件太長,組合邏輯亂用等。如果是代碼問題,看是否能優化設計。能夠通過

2016-09-13 21:58:50

時可以引用這個標識符,大大方便了派生時鐘的定義。 一種特殊情況的周期約束是相關時鐘。前面提到周期約束不會覆蓋異步路徑,如圖1所示的D路徑。但是如果兩個時鐘是“相關”的,則實現工具和時序分析工具會考

2015-02-03 14:13:04

小技巧和幫助來設置時鐘;使用像Synopsys Synplify Premier一樣的工具正確地設置時序約束;然后調整參數使之滿足賽靈思FPGA設計性能的目標。會有來自不同角度的挑戰,包括:?更好

2021-05-18 15:55:00

時序分析是FPGA設計的必備技能之一,特別是對于高速邏輯設計更需要時序分析,經過基礎的FPGA是基于時序的邏輯器件,每一個時鐘周期對于FPGA內部的寄存器都有特殊的意義,不同的時鐘周期執行不同的操作

2017-02-26 09:42:48

在給FPGA做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在FPGA設計工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯。

2019-11-08 07:27:54

的目標:多路復用輸入到FIFO并使其正常工作。 (多路復用使用固定輸入,但不使用不同的輸入)。2.或者是否知道如何正確約束數據路徑的延遲?我使用set_max_delay -from [FIR

2020-07-27 09:55:39

本文轉載IC_learner - 博客園數字IC之路-SDC篇(一):基本的時序路徑約束_u012675910的博客-CSDN博客_sdc約束 RTL代碼描述了電路的時序邏輯和組合邏輯,即RTL代碼

2022-03-01 06:48:09

方法來限制關鍵路徑,而不是將周期約束放在它上面? (沒有虛假路徑或多周期路徑)。我的理解是正確的,如果我應用10ns的周期約束,那么連接到該時鐘的所有路徑都被約束到那個時間段,那么它也會自動約束關鍵路徑

2019-04-08 08:58:57

design內部,都是同步時序電路,各處的延時等都能夠估計出來,但是FPGA內部并不知道外部的設備的時序關系。所以,TIming constraints包括輸入路徑(Input paths )寄存器

2019-07-09 09:14:48

時序約束的概念 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(STA, IPAD到OPAD)等3種。通過附加約束條件可以使綜合布線工具調整映射和布局布線過程,使設計達到時序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 賽靈思FPGA設計時序約束指南,下來看看

2016-05-11 11:30:19 48

48 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 時序約束可以使得布線的成功率的提高,減少ISE布局布線時間。這時候用到的全局約束就有周期約束和偏移約束。周期約束就是根據時鐘頻率的不同劃分為不同的時鐘域,添加各自周期約束。對于模塊的輸入輸出端口添加

2017-02-09 02:56:06 605

605 ,您經常需要定義時序和布局約束。我們了解一下在基于賽靈思 FPGA 和 SoC 設計系統時如何創建和使用這兩種約束。 時序約束 最基本的時序約束定義了系統時鐘的工作頻率。然而,更高級的約束能建立時鐘路徑之間

2017-11-17 05:23:01 2417

2417

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

我們知道XDC與UCF的根本區別之一就是對跨時鐘域路徑(CDC)的缺省認識不同,那么碰到FPGA設計中常見的CDC路徑,到底應該怎么約束,在設計上又要注意些什么才能保證時序報告的準確性?CDC

2017-11-18 04:04:24 5809

5809

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 4903

4903

在給FPGA做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在FPGA設計工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯

2017-11-24 20:12:54 1520

1520 在網絡視頻和實時通信應用中需要研究帶長度約束的K端網絡可靠性分析問題,即任意兩端點之間在給定時間延遲D約束內的K端網絡可靠性。對帶長度約束的K端網絡可靠性問題進行了研究,主要是在傳統不帶路徑約束

2017-12-06 14:03:03 0

0 典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。

2020-01-27 10:37:00 2460

2460

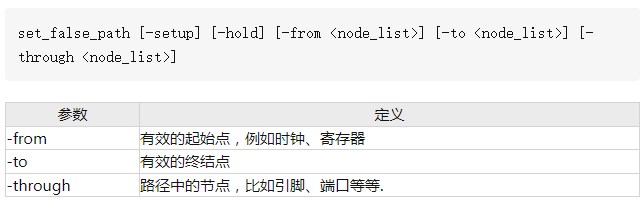

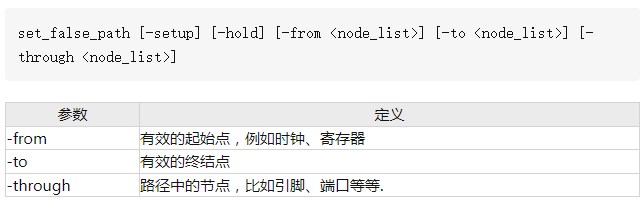

偽路徑約束 在本章節的2 約束主時鐘一節中,我們看到在不加時序約束時,Timing Report會提示很多的error,其中就有跨時鐘域的error,我們可以直接在上面右鍵,然后設置兩個時鐘的偽路徑

2020-11-14 11:28:10 2636

2636

下面舉一個最簡單的例子來說明時序分析的基本概念。假設信號需要從輸入到輸出在FPGA內部經過一些邏輯延時和路徑延時。我們的系統要求這個信號在FPGA內部的延時不能超過15ns,而開發工具在執行過程中

2021-01-11 17:44:43 8

8 在 FPGA 設計進程中,時序收斂無疑是一項艱巨的任務。低估這項任務的復雜性常常導致工作規劃面臨無休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時序收斂所需時間,從而加速產品上市。本篇博文描述了一種

2021-05-19 11:25:47 2677

2677

A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(IPAD到OPAD)等3種。通過附加

2021-09-30 15:17:46 4401

4401 A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(IPAD到OPAD)等3種。通過附加

2021-10-11 10:23:09 4861

4861

本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

左邊的電路圖是需要分析的電路,我們的目的是要對此電路進行時序分析,那首先要找到該電路需要分析的時序路徑,既然找路徑,那找到時序分析的起點與終點即可。

2022-05-04 17:13:00 1827

1827 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-05-11 10:07:56 3462

3462

明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

2022-07-11 11:33:10 2922

2922

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

要從時序分析刪除一組路徑,如果您確定這些路徑不會影響時序性能(False 路徑),可用FROM-TO 約束以及時序忽略 (TIG) 關鍵字。

2022-08-02 08:57:26 517

517 隨著設計復雜度和調用IP豐富度的增加,在調試時序約束的過程中,用戶常常會對除了自己設定的約束外所涉及的繁雜的時序約束感到困惑而無從下手。舉個例子,我的XDC里面并沒有指定set_false_path

2022-08-02 08:03:36 1014

1014

在 FPGA 設計進程中,時序收斂無疑是一項艱巨的任務。低估這項任務的復雜性常常導致工作規劃面臨無休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時序收斂所需時間,從而加速產品上市。本篇博文描述了一種方法,能夠有效減少時序路徑問題分析所需工作量

2022-08-02 09:25:06 425

425

時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時間或保持時間所多出的時間,那么“裕量”越多,意味著時序約束越寬松。

2022-08-04 17:45:04 657

657 一、什么是多周期路徑約束? 不管是quartus中還是在Vivado中,默認的建立時間和保持時間的檢查都是單周期的,如圖1所示,也就是說如果A時刻發送,B時刻捕獲,這兩者之間相差一個時鐘周期,也就

2022-12-10 12:05:02 779

779 ? ? 1、時序錯誤的影響 ? ? ? 一個設計的時序報告中,design run 時序有紅色,裕量(slack)為負數時,表示時序約束出現違例,雖然個別違例不代表你的工程就有致命的問題,但是這是

2023-03-17 03:25:03 426

426 典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。

2023-06-26 10:30:43 247

247

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

FPGA開發過程中軟件的綜合布線耗時很長,這塊對FPGA產品開發的進度影響很大。

2023-06-26 14:58:09 367

367

今天我們要介紹的時序分析概念是 **時序路徑** (Timing Path)。STA軟件是基于timing path來分析timing的。

2023-07-05 14:54:43 985

985

命令set_multicycle_path常用來約束放松路徑的約束。通常情況下,這種路徑具有一個典型的特征:數據多個周期翻轉一次,如下圖所示。因此,我們把這種路徑稱為多周期路徑(FPGA設計中更多的是單周期路徑,每個周期數據均翻轉)。

2023-09-14 09:05:02 466

466

電子發燒友App

電子發燒友App

評論