什么是靜態(tài)時序分析?

通俗來說:在輸入信號到輸出信號中,因為經(jīng)過的傳輸路徑、寄存器、門電路等器件的時間,這個時間就是時序。開發(fā)工具不知道我們路徑上的要求,我們通過時序約束來告訴開發(fā)工具,根據(jù)要求,重新規(guī)劃,從而實現(xiàn)我們的時序要求,達(dá)到時序的收斂。

我們對整個設(shè)計添加時序約束,讓整個設(shè)計。

時序的欠約束:約束的少了;

時序的過約束:約束了過了;

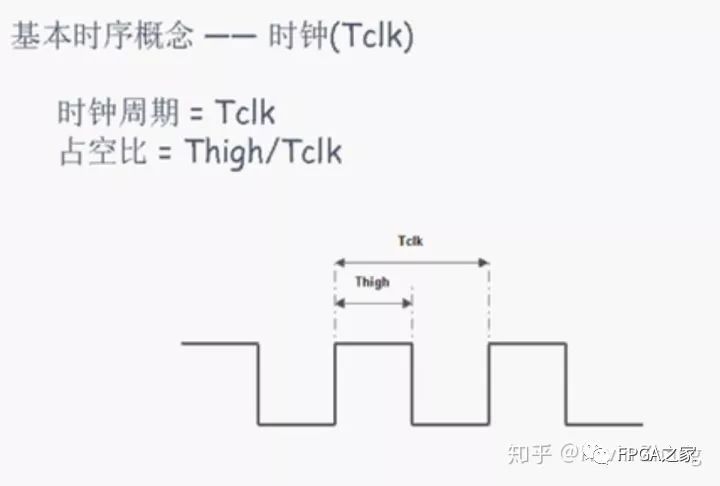

時序基本概念:時鐘

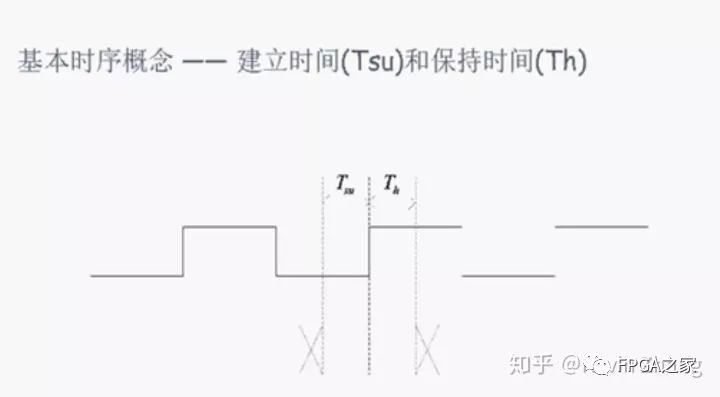

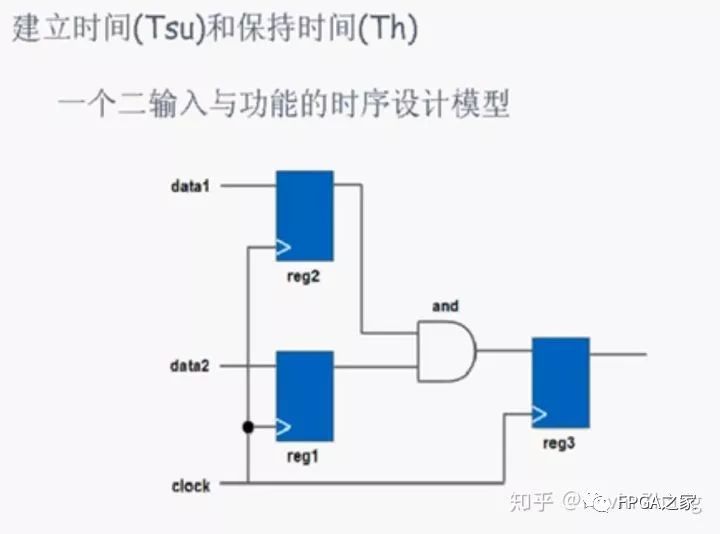

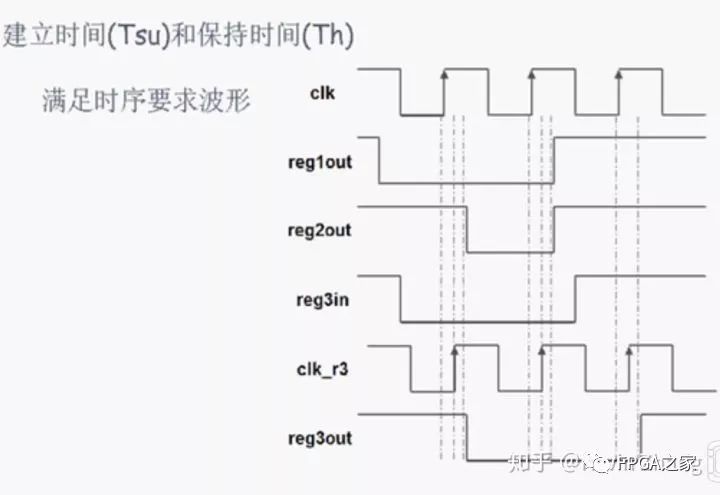

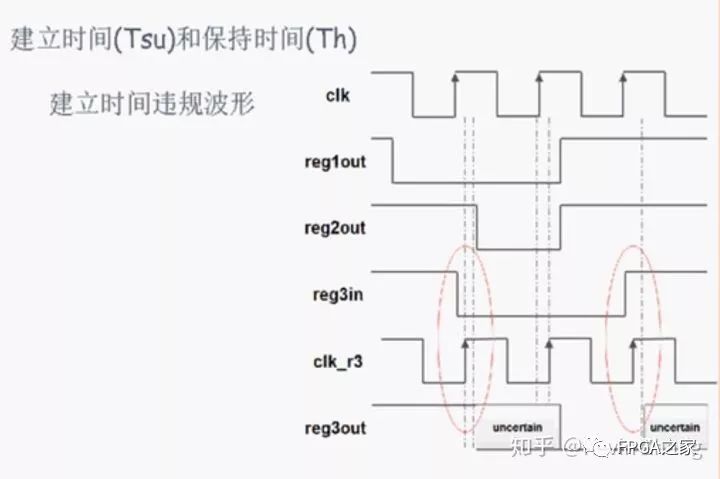

建立時間setup和保持時間hold

建立時間:在時鐘上升沿前,數(shù)據(jù)不能改變的最小時間;

保持時間:在數(shù)據(jù)上升沿后,數(shù)據(jù)不能改變的最小時間;

例子

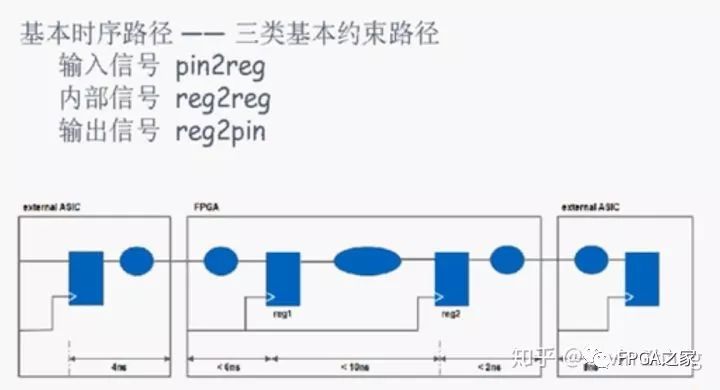

三種時序路徑

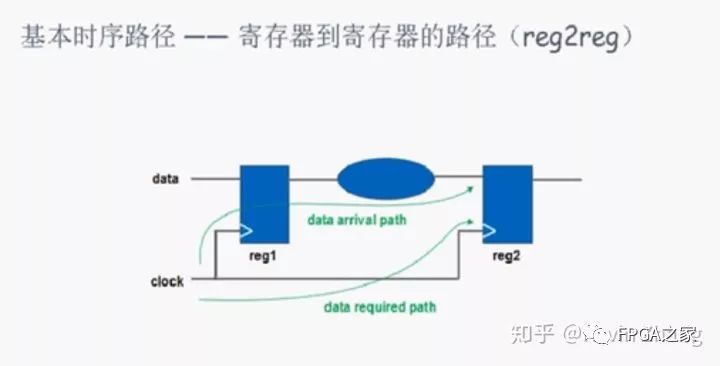

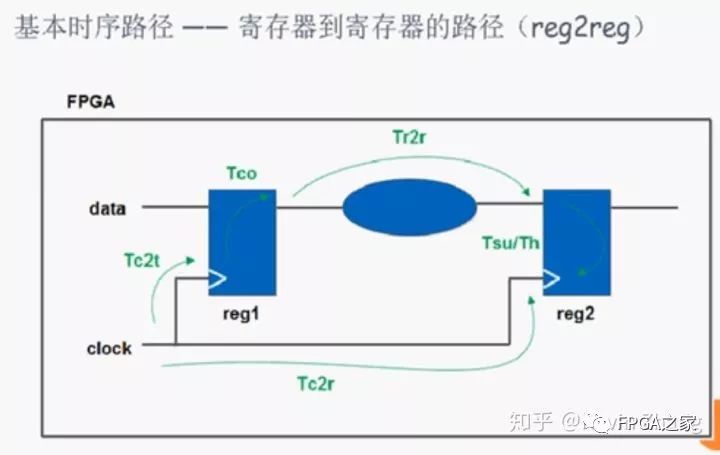

分析一個寄存器的延時

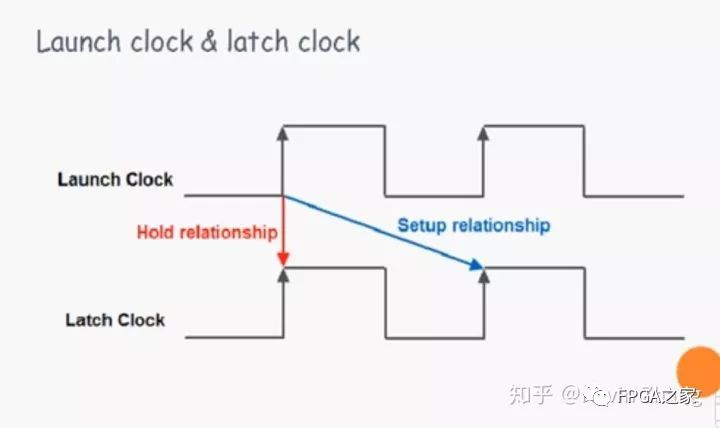

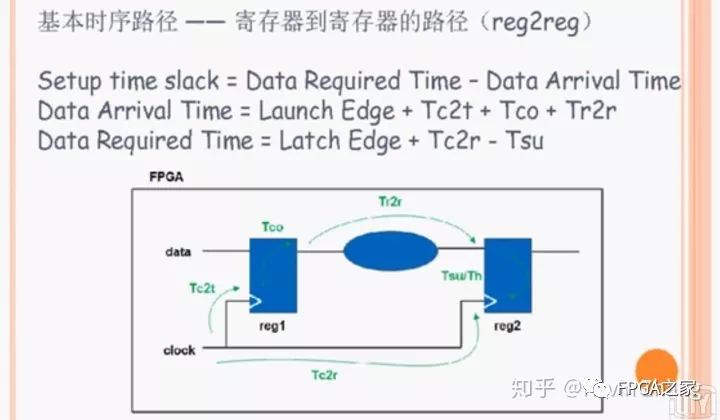

setup slack余量,這個時間是差了一個時鐘周期;

數(shù)據(jù)達(dá)到時間,首先是發(fā)射時鐘+時鐘到REG1的延時+reg1的延時+傳輸路徑的延時

數(shù)據(jù)時間需求:鎖存時鐘+時鐘到reg2的延時-setup時間

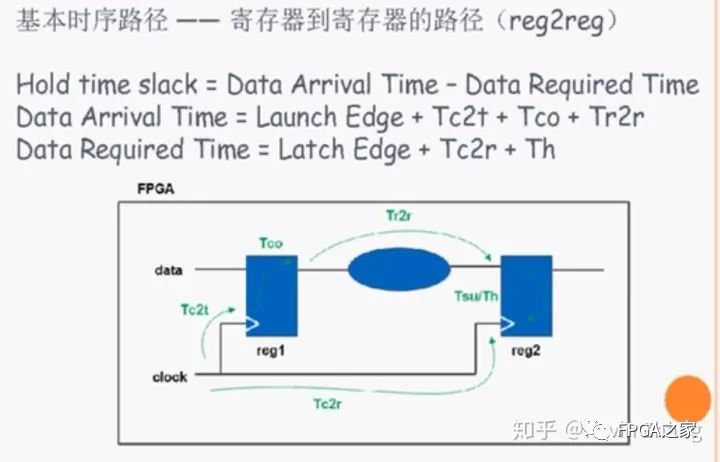

hold時間余量,這里分析的應(yīng)該是同一個周期里面的時間,這個時間是對齊的;

-

FPGA

+關(guān)注

關(guān)注

1645文章

22012瀏覽量

616649 -

時序設(shè)計

+關(guān)注

關(guān)注

0文章

21瀏覽量

44013

原文標(biāo)題:FPGA學(xué)習(xí)-時序分析基礎(chǔ)001

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發(fā)商

【火爆】全國大學(xué)生FPGA大賽配套圖像教學(xué)視頻已連載更新40+期

【國產(chǎn)FPGA必備教程】——紫光同創(chuàng)FPGA圖像視頻教程,適用于小眼睛FPGA盤古全系列開發(fā)板

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

助力AIoT應(yīng)用:在米爾FPGA開發(fā)板上實現(xiàn)Tiny YOLO V4

時序約束一主時鐘與生成時鐘

Verilog vhdl fpga

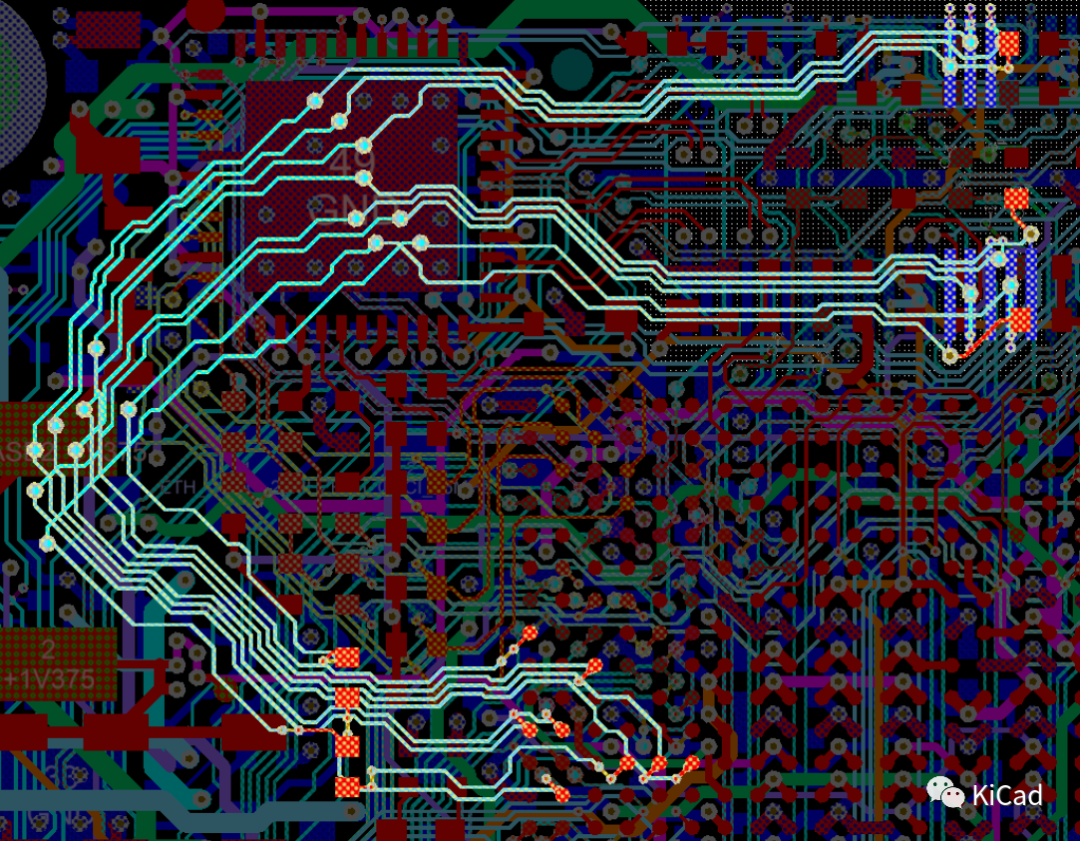

KiCad 7中添加網(wǎng)絡(luò)類(一)

常用時序約束使用說明-v1

高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時序誤差的設(shè)計考慮

FPGA開發(fā)中如何對整個設(shè)計添加時序約束

FPGA開發(fā)中如何對整個設(shè)計添加時序約束

評論