我知道,我對與電子有關的所有事情都很著迷,但不論從哪個角度看,今天的現場可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個智能時代,在這個領域,想擁有一技之長的你還沒有關注FPGA,那么世界將拋棄你,時代將拋棄你。本公眾號作者ALIFPGA,多年FPGA開發經驗,所有文章皆為多年學習和工作經驗之總結。

FPGA時序約束簡介。

時序約束的場景:

在簡單電路中,當頻率較低時,數字信號的邊沿時間可以忽略時,無需考慮時序約束。但在復雜電路中,為了減少系統中各部分延時,使系統協同工作,提高運行頻率,需要進行時序約束。通常當頻率高于50MHz時,需要考慮時序約束。

限制FPGA最大頻率的因素:

組合邏輯延時

越多的門電路,所構成的組合邏輯延時越大,以ALTERA C4為例,FPGA實際上是用四輸入查找表(LUT, Look-Up-Tables)的方式實現門電路的,變量數目小于4的所有組合邏輯延時相同,大于4時需要多個查找表組合,延時增加。

信號路徑延時

路徑延時是所有延時中最需要考慮的,甚至可以占到總延時的一半以上,一般EDA工具不會尋找最快的路徑,需要施加時序約束。

時鐘偏移、抖動和延時

時鐘傳到每個觸發器的時間會由于距離時鐘源路徑長度不同而有偏移,時鐘偏移可以通過走時鐘樹的結構解決,但時鐘偏斜永遠存在,不可能消除。時鐘抖動是由于溫度分布,信號串擾等因素使得晶振、PLL等產生的時鐘信號周期不會嚴格相等而造成的。

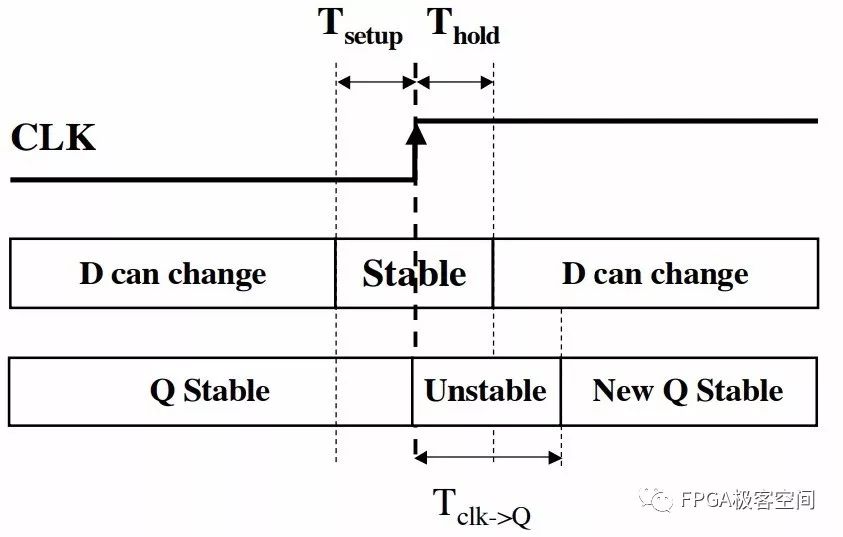

觸發器建立時間Tsu、保持時間Th

輸入管腳的數據必須在時鐘有效之前提前出現的時間稱為建立時間Tsu;保持時間Th是指在時鐘上跳沿后,數據必須保持的最小時間。

觸發器時鐘到輸出時間Tco

在時鐘有效后,D的數據并不能立即傳到Q端,這段等待的時間就是觸發器的時鐘到輸出時間。

以上時間是觸發器固有時間,無法更改。

功耗

合理的時序約束可以提高運行頻率,但往往會使得功耗增加, 在性能要求不高的移動設備中,需要綜合考慮。

高扇出信號延時

高扇出信號是指帶多負載的信號,在多負載情況下,信號的延時會增大,信號到達某些負載的時間增加,從而可能造成該信號相對時鐘信號是一個晚到的信號。

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618821 -

時序

+關注

關注

5文章

398瀏覽量

37979

原文標題:簡述FPGA時序約束理論

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA中的時序約束設計

深入了解時序約束以及如何利用時序約束實現FPGA 設計的最優結果

正點原子FPGA靜態時序分析與時序約束教程

詳解FPGA的時序input delay約束

FPGA時序約束簡介

FPGA時序約束簡介

評論