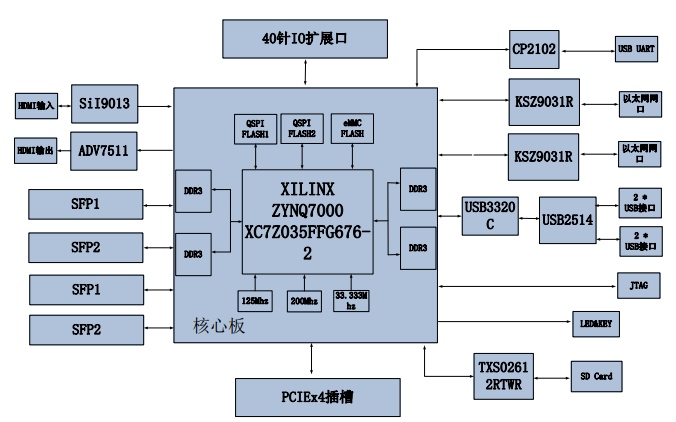

(基于TI KeyStone架構C6000系列TMS320C6657雙核C66x 定點/浮點DSP以及Xilinx Zynq-7000系列SoC處理器XC7Z035-2FFG676I設計的異構多核評估板,由核心板與評估底板組成。)

1.1.1 例程位置

ZYNQ例程保存在資料盤中的DemoZYNQPLaurora_8b10b_0_ex文件夾下。

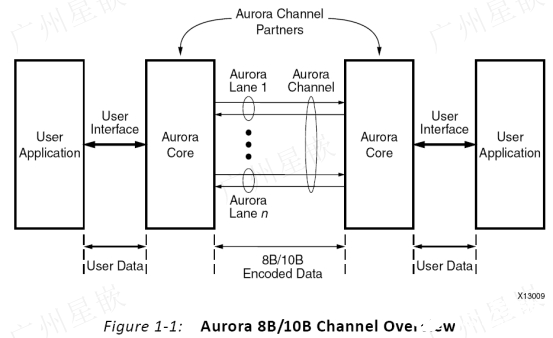

1.1.2 功能簡介

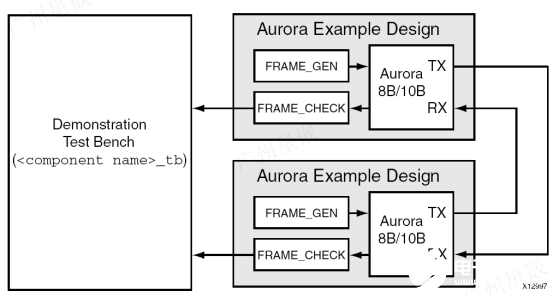

使用Aurora 8B/10B IP核生成后帶的例子工程,稍作修改。

圖 Aurora 8B/10B例子工程

FRAME_GEN: 本地并行數據發送模塊

功能:本地產生GTX并行發送數據

接口說明:

// User Interface

output [0:15] TX_D; //發送數據

output TX_REM; //最后一個16bits數據的高低字節有效標識,0表示,表示TX_D[0:7]有效;1表示TX_D[0:15]有效。

output TX_SOF_N; //發送開始標識,低電平有效

output TX_EOF_N; //發送結束標識,低電平有效

output TX_SRC_RDY_N; //發送數據源端準備好標志,低有效

input TX_DST_RDY_N; //發送數據目的端準備好標,為0時才允許發送數據

// System Interface

input USER_CLK;//用戶時鐘,由Aurora IP核提供,數據發送模塊用此時鐘作為同步時鐘

input RESET;//復位,高有效

input CHANNEL_UP;//GTX通道初始化完成標志,為1時表示完成

數據發送模塊只有在RESET=0、CHANNEL_UP=1和TX_DST_RDY_N=0時,才允許發送數據。

FRAME_CHECK: 本地并行數據接收檢測模塊

功能:本地接收GTX并行數據,并檢測數據是否存在誤碼

接口說明:

// User Interface

input [0:15] RX_D; //接收數據

output RX_REM; //最后一個16bits數據的高低字節有效標識,0表示,表示RX_D[0:7]有效;1表示RX_D[0:15]有效。

output RX_SOF_N; //接收開始標識,低電平有效

output RX_EOF_N; //接收結束標識,低電平有效

input RX_SRC_RDY_N; //接收數據有效,低電平有效

// System Interface

input USER_CLK; //用戶時鐘,由Aurora IP核提供,數據發送模塊用此時鐘作為同步時鐘

input RESET; //復位,高有效

input CHANNEL_UP; //GTX通道初始化完成標志,為1時表示完成

output [0:7] ERR_COUNT; //接收數據錯誤個數

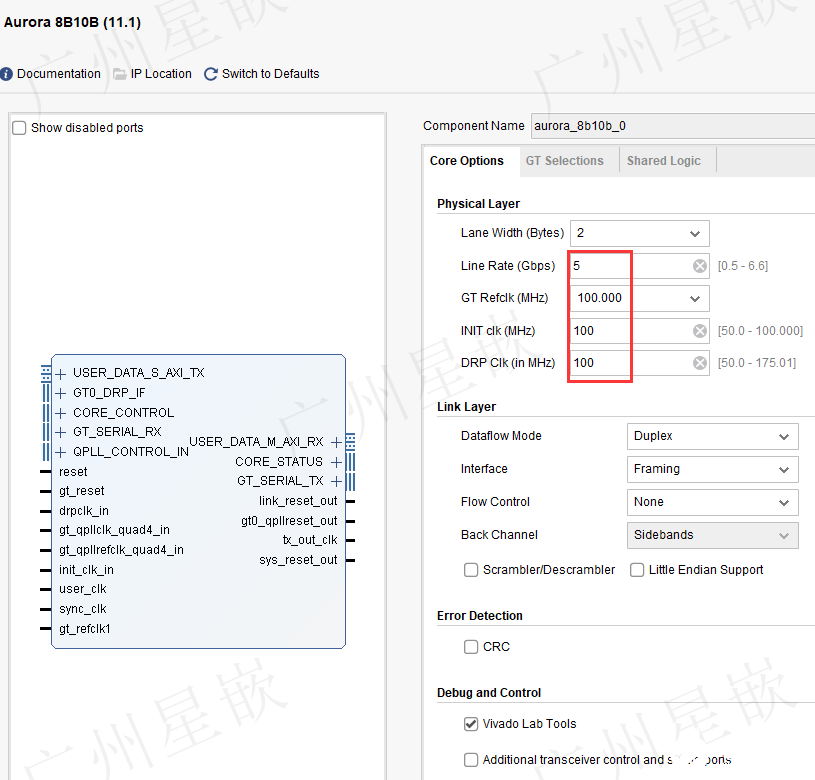

Aurora 8B10B IP核參數設置如下圖所示:

Aurora 8B10B IP核顯示最高只支持6.6Gbps,這里我們將線速率設置為5Gbps,參考時鐘設置為100MHz。

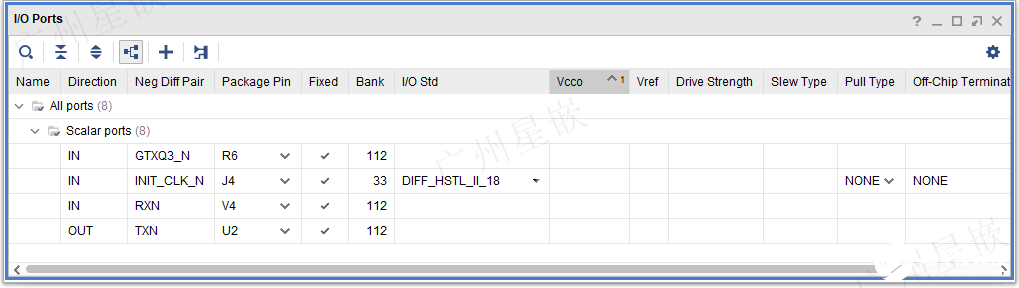

1.1.3 管腳約束

ZYNQ PL工程管腳約束如下圖所示:

1.1.4 例程使用

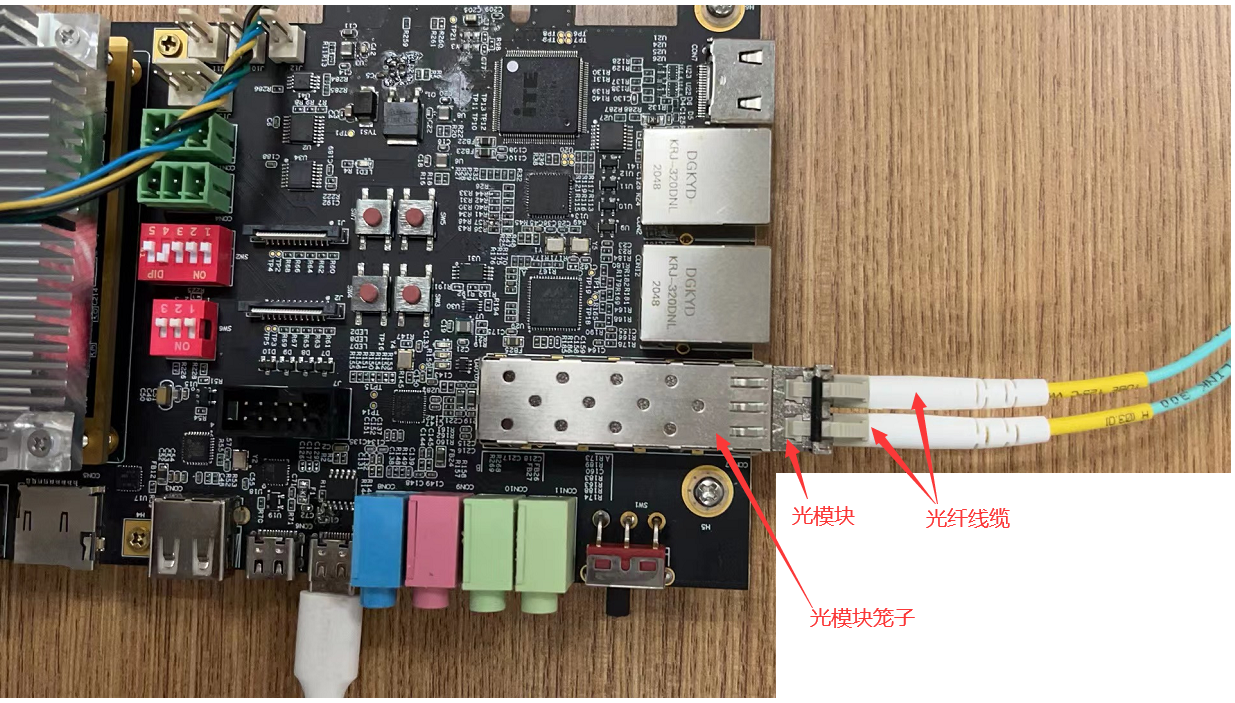

1.1.4.1 連接光纖模塊

將光模塊插入光模塊籠子,并使用光纖線纜將光模塊的收、發端口自環對接:

1.1.4.2 加載運行ZYNQ程序

1.1.4.2.1 打開Vivado工程

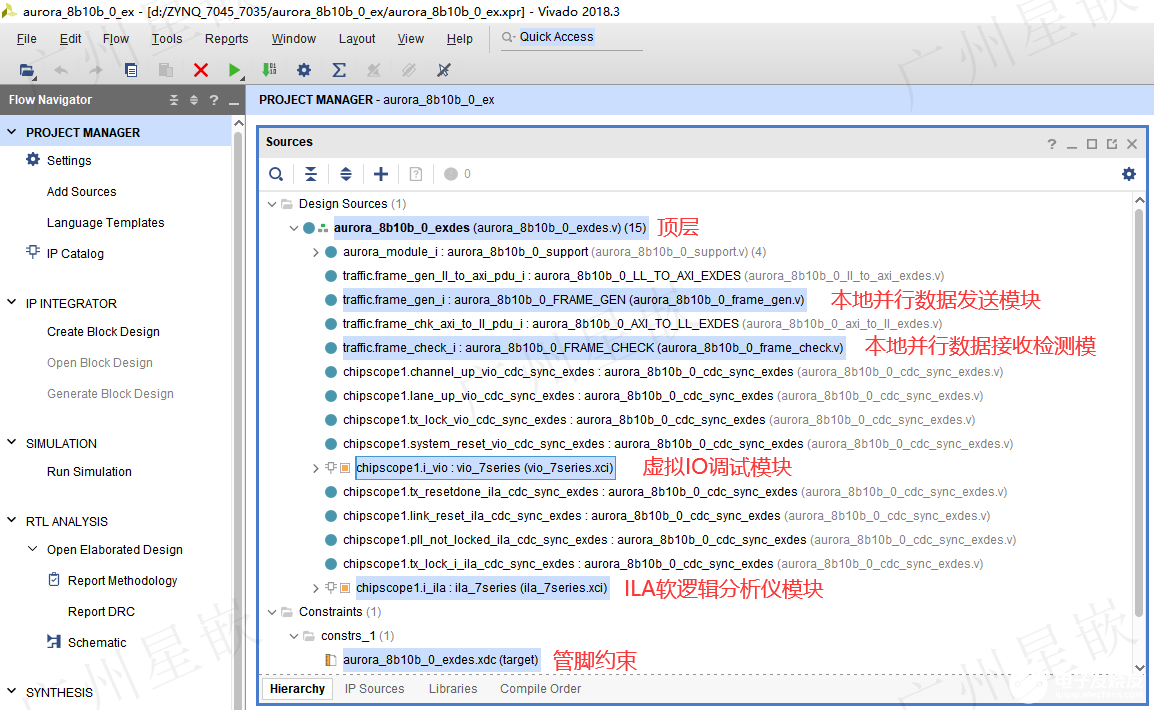

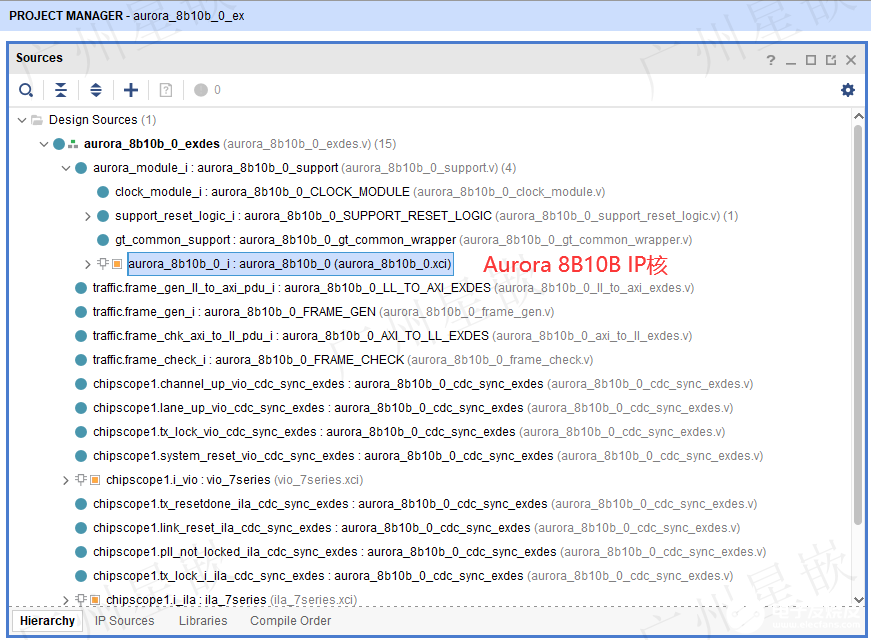

打開Vivado示例工程:

工程打開后界面及工程主要模塊說明如下圖所示:

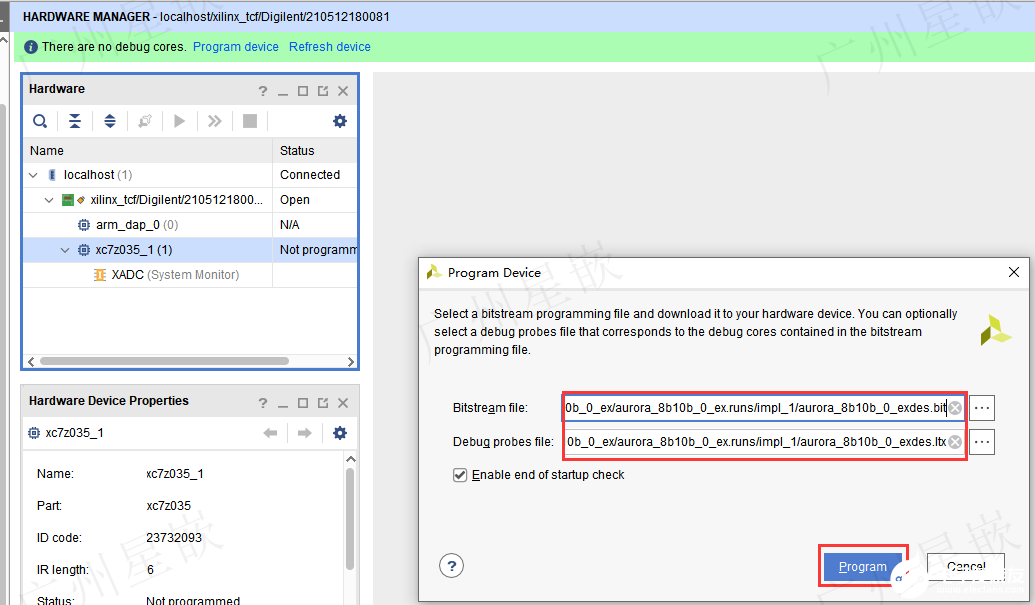

1.1.4.2.2 下載ZYNQ PL程序

下載bit流文件aurora_8b10b_0_exdes.bit,并且配套aurora_8b10b_0_exdes.ltx調試文件,如下圖下載界面所示:

1.1.4.3 運行結果說明

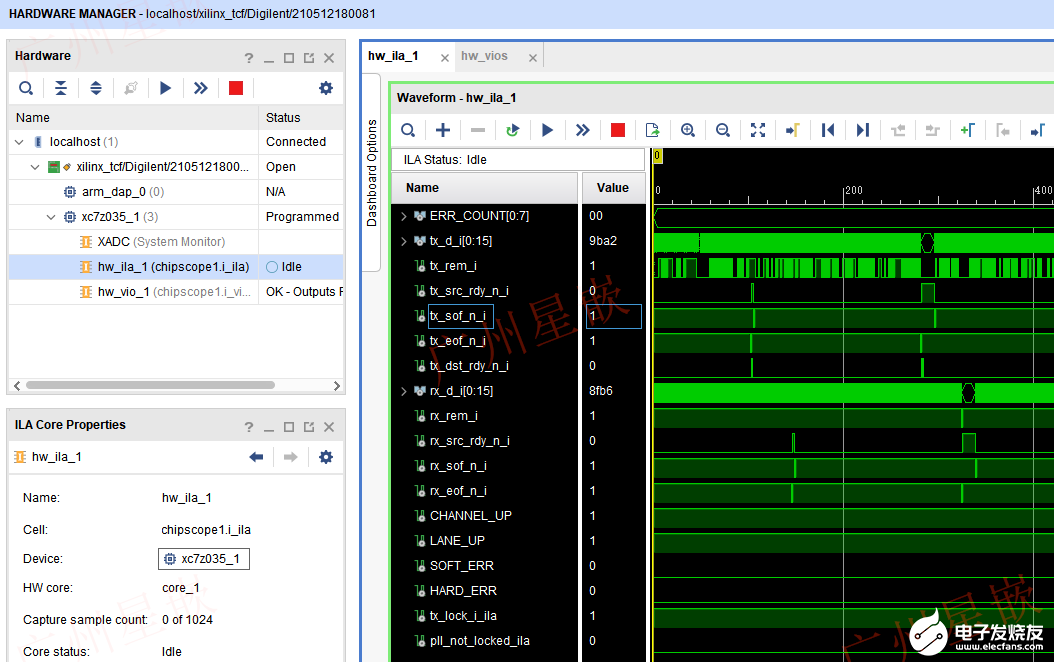

ZYNQ PL端提供的ILA調試窗口,可以實時抓取采集GTX收發本地并行信號以及錯誤檢測信號的時序波形。

ILA抓取波形如下圖所示:

ILA抓取信號說明如下:

ERR_COUNT[0:7]:接收數據錯誤個數,接收模塊分析接收數據是否正確;

tx_d_i[0:15]:發送數據;

tx_rem_i:最后一個發送數據的高低字節有效標識,0表示,表示tx_d_i[0:7]有效,1表示tx_d_i[0:15]有效;

tx_src_rdy_n_i:發送數據源端準備好標志,結合tx_dst_rdy_n_i使用,都為0時表示可以發送數據,

tx_sof_n_i:發送開始標識,低電平有效;

tx_eof_n_i:發送結束標識,低電平有效;

tx_dst_rdy_n_i:發送數據目的端準備好標志;

rx_d_i[0:15]:接收數據

rx_rem_i:最后一個接收數據的高低字節有效標識,0表示,表示rx_d_i[0:7]有效,1表示rx_d_i[0:15]有效;

rx_src_rdy_n_i:接收數據源端準備好標志;

rx_sof_n_i:接收開始標識,低電平有效;

rx_eof_n_i:接收結束標識,低電平有效;

CHANNEL_UP:為1表示GTX通道完成正常初始化;

LANE_UP:指示GTX每個lane是否正常初始化成功,這里只有1個Lane;

SOFT_ERR、HARD_ERR:軟、硬件錯誤指示,正常情況應該為0

tx_lock_i_ila:GTX時鐘鎖定指示,正常情況應該為1

pll_not_locked_ila:GTX時鐘失鎖指示,正常情況應該為0

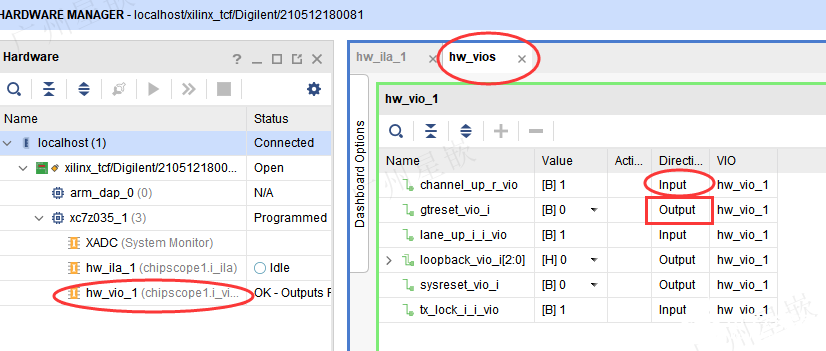

VIO虛擬IO界面如下圖所示:

VIO界面上標識Input的為采集信號,用戶只能查看對應信號當前的邏輯電平值,1表示高電平,0表示低電平;VIO界面上標識Output的為用戶控制信號,用于控制用戶邏輯的,用戶可以在Value一欄輸入0/1電平值,從而達到控制用戶邏輯的目的。VIO界面主要用于復位用戶邏輯,以及查看通道是否鏈接成功,VIO界面可以不用操作。

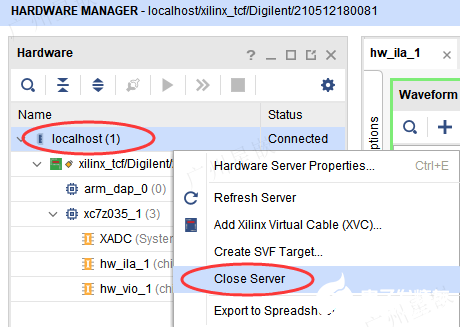

1.1.4.4 退出實驗

Vivado調試界面Hardware Manager窗口,右鍵單擊localhost(1),在彈出的菜單中點擊Close Server,斷開ZYNQ JTAG仿真器與板卡的連接:

最后,關閉板卡電源,實驗結束。

審核編輯:湯梓紅

-

通信

+關注

關注

18文章

6206瀏覽量

137840 -

Xilinx

+關注

關注

73文章

2185瀏覽量

125382 -

SFP

+關注

關注

4文章

156瀏覽量

36030 -

Zynq

+關注

關注

10文章

615瀏覽量

48257

發布評論請先 登錄

[XILINX] 正點原子ZYNQ7035/7045/7100開發板發布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

百科:BIDI SFP光模塊和普通SFP光模塊的區別

zynq XC7Z100板卡學習資料:基于zynq XC7Z100 FMC接口通用計算平臺

基于FPGA的光口通信開發案例|基于FPGA Kintex-7 SFP+光口的10G UDP網絡通信開發案例

Xilinx Zynq7035算力指標

DSP+ZYNQ多核例程使用手冊-XQTyer【開源】

Xilinx Zynq7035 PL SFP光口通信例程

Xilinx Zynq7035 PL Cameralink回環實現

ZYNQ(FPGA)與DSP之間GPIO通信實現

Xilinx ZYNQ UltraScale+RFSoCZU27DR 開源RFSOC算法驗證評估板

易天光通信SFP電口模塊和10G SFP+電口模塊介紹

ZYNQ7000開發平臺的AX7Z035開發板用戶手冊免費下載

Xilinx Zynq7035 PL SFP光口通信例程

Xilinx Zynq7035 PL SFP光口通信例程

評論