配置組電壓選擇(CFGBVS)引腳必須設置為高電平或低電平,以確定I/O電壓支持的引腳在bank0,以及多功能引腳在bank14和15在配置時使用。CFGBVS是一個邏輯輸入,VCCO_0和GND之間的引腳引用。當CFGBVS引腳為高(例如,連接VCCO_0提供3.3V或2.5V),在bank0上的配置和JTAG I/O支持在配置期間和配置后,在3.3V或2.5V下運行。

當CFGBVS引腳為Low時(例如,連接到GND),bank0的I/O支持1.8V或1.5V運行。

在1.2V時不支持配置。

CFGBVS引腳設置決定I/O電壓支持bank0在任何時候,和配置中的bank14和bank15。VCCO為每個配置組提供,如果在配置過程中使用CFGBVS,必須匹配CFGBVS的選擇,如果CFGBVS與VCCO_0綁定,電壓選擇為2.5V或3.3V,若CFGBVS與GND綁定,則為1.8V或1.5V。

關于FPGA的配置模式。

注意:無論如何,在VCCO_0電壓級別的bank0中始終支持JTAG接口配置模式。

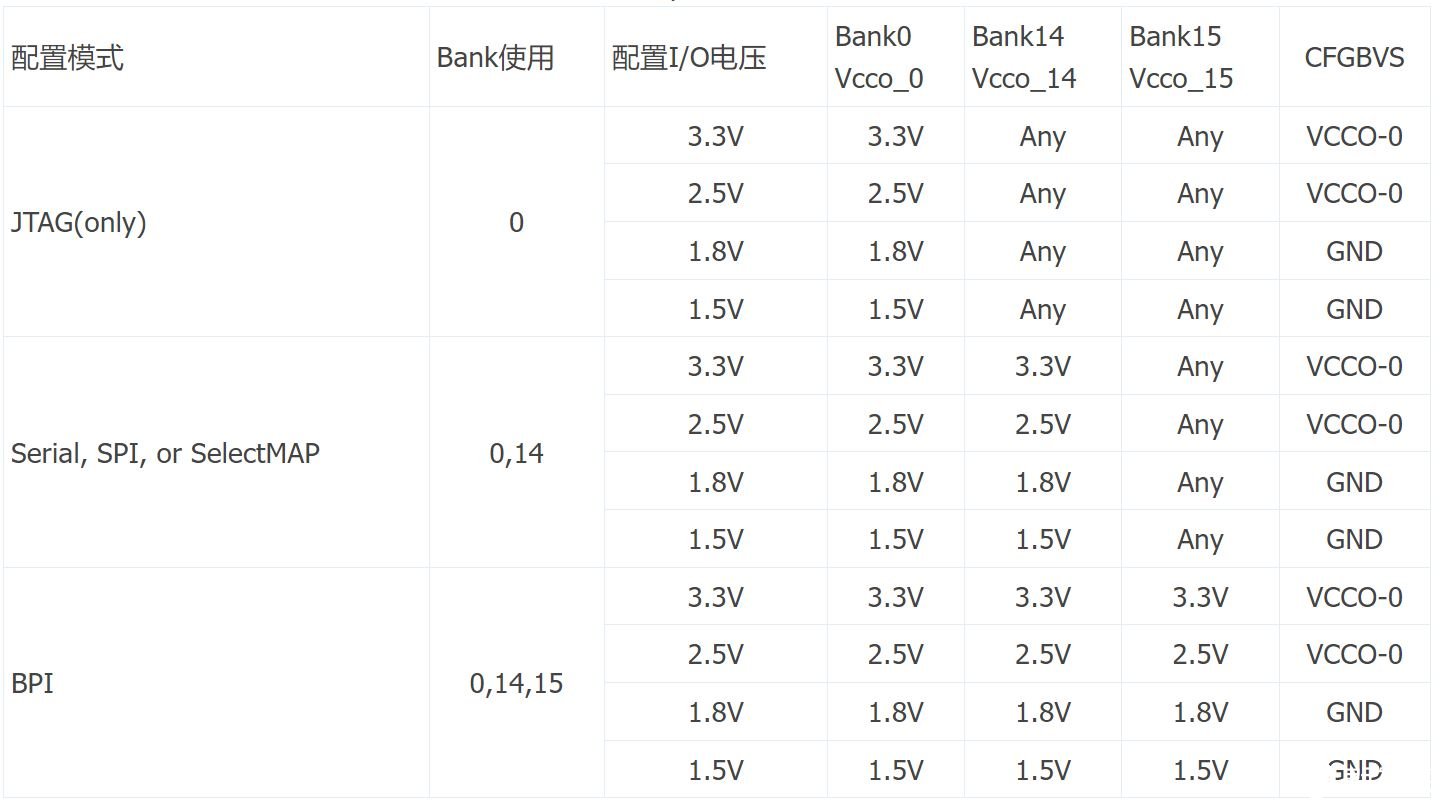

設置CFGBVS引腳支持所需的配置I/O電壓。(僅支持Spartan-7、Artix-7和Kintex-7 FPGA配置模式)見下表:

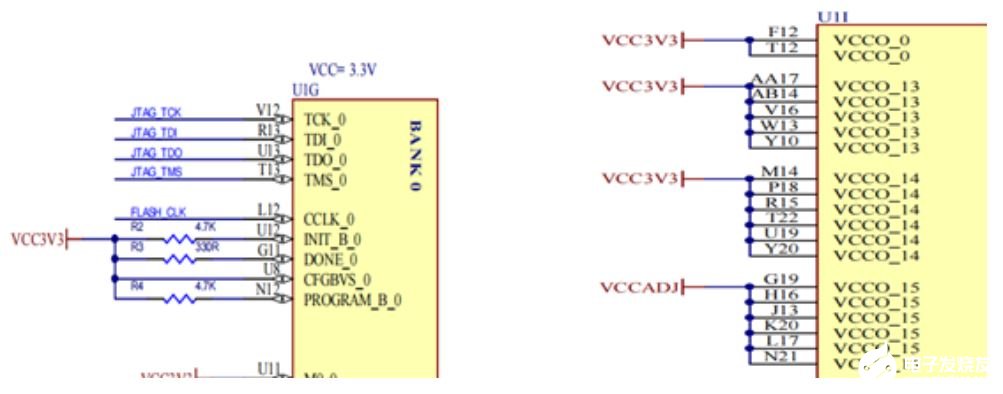

下圖所演示的為米聯客MA703核心板中,CFGBVS接入3.3V后bank0和bank14、15可接入的電壓,由于使用的是QSPI FLASH BANK14必須和BANK0是相同電壓,這里設置的是3.3V。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21974瀏覽量

614365 -

Xilinx

+關注

關注

73文章

2182瀏覽量

124398 -

引腳

+關注

關注

16文章

1594瀏覽量

52391 -

硬件設計

+關注

關注

18文章

426瀏覽量

45096

發布評論請先 登錄

Xilinx FPGA CFGBVS 引腳以及BANK電壓硬件設計注意事項

Xilinx FPGA CFGBVS 引腳以及BANK電壓硬件設計注意事項

評論