關(guān)于阻塞賦值和非阻塞賦值的問題,明德?lián)P的學(xué)員提得比較多,今天小黑老師專門給大家普及一下阻塞賦值和非阻塞賦值的相關(guān)知識(shí)。

一、概述

1、阻塞賦值對(duì)應(yīng)的電路往往與觸發(fā)沿沒有關(guān)系,只與電平的變化有關(guān)系。

阻塞賦值符號(hào)“=”。

2、非阻塞賦值對(duì)應(yīng)的電路結(jié)構(gòu)往往與邊沿觸發(fā)有關(guān)系,只有在觸發(fā)沿時(shí)才有可能發(fā)生賦值的情況。

非阻塞賦值符號(hào)“<=”。

二、賦值方式

1、阻塞賦值

阻塞賦值操作符用等號(hào)(即 = )表示。阻塞賦值時(shí)先計(jì)算等號(hào)右手方向(RHS)部分的值,這時(shí)賦值語句不允許任何別的語句的干擾,直到現(xiàn)行的賦值完成時(shí)刻,即把RHS賦值給 LHS的時(shí)刻,它才允許別的賦值語句的執(zhí)行。一般可綜合的阻塞賦值操作在RHS不能設(shè)定有延遲,(即使是零延遲也不允許)。若在RHS 加上延遲,則在延遲期間會(huì)阻止賦值語句的執(zhí)行, 延遲后才執(zhí)行賦值,這種賦值語句是不可綜合的,在需要綜合的模塊設(shè)計(jì)中不可使用這種風(fēng)格的代碼。

阻塞賦值的執(zhí)行可以認(rèn)為是只有一個(gè)步驟的操作:

所謂阻塞的概念是指在同一個(gè)always塊中,其后面的賦值語句從概念上(即使不設(shè)定延遲)是在前一句賦值語句結(jié)束后再開始賦值的。

如果在一個(gè)過程塊中阻塞賦值的RHS變量正好是另一個(gè)過程塊中阻塞賦值的LHS變量,這兩個(gè)過程塊又用同一個(gè)時(shí)鐘沿觸發(fā),這時(shí)阻塞賦值操作會(huì)出現(xiàn)問題,即如果阻塞賦值的次序安排不好,就會(huì)出現(xiàn)競(jìng)爭(zhēng)。若這兩個(gè)阻塞賦值操作用同一個(gè)時(shí)鐘沿觸發(fā),則執(zhí)行的次序是無法確定的。

2、非阻塞賦值

非阻塞賦值操作符用小于等于號(hào) (即 <= )表示。在賦值操作時(shí)刻開始時(shí)計(jì)算非阻塞賦值符的RHS表達(dá)式,賦值操作時(shí)刻結(jié)束時(shí)更新LHS。在計(jì)算非阻塞賦值的RHS表達(dá)式和更新LHS期間,其他的Verilog語句,包括其他的Verilog非阻塞賦值語句都能同時(shí)計(jì)算RHS表達(dá)式和更新LHS。非阻塞賦值允許其他的Verilog語句同時(shí)進(jìn)行操作。

非阻塞賦值的操作可以看作為兩個(gè)步驟的過程:

1)在賦值時(shí)刻開始時(shí),計(jì)算非阻塞賦值RHS表達(dá)式。

2)在賦值時(shí)刻結(jié)束時(shí),更新非阻塞賦值LHS表達(dá)式。

非阻塞賦值操作只能用于對(duì)寄存器類型變量進(jìn)行賦值,因此只能用在“initial”塊和“always”塊等過程塊中。非阻塞賦值不允許用于連續(xù)賦值。

三、舉例

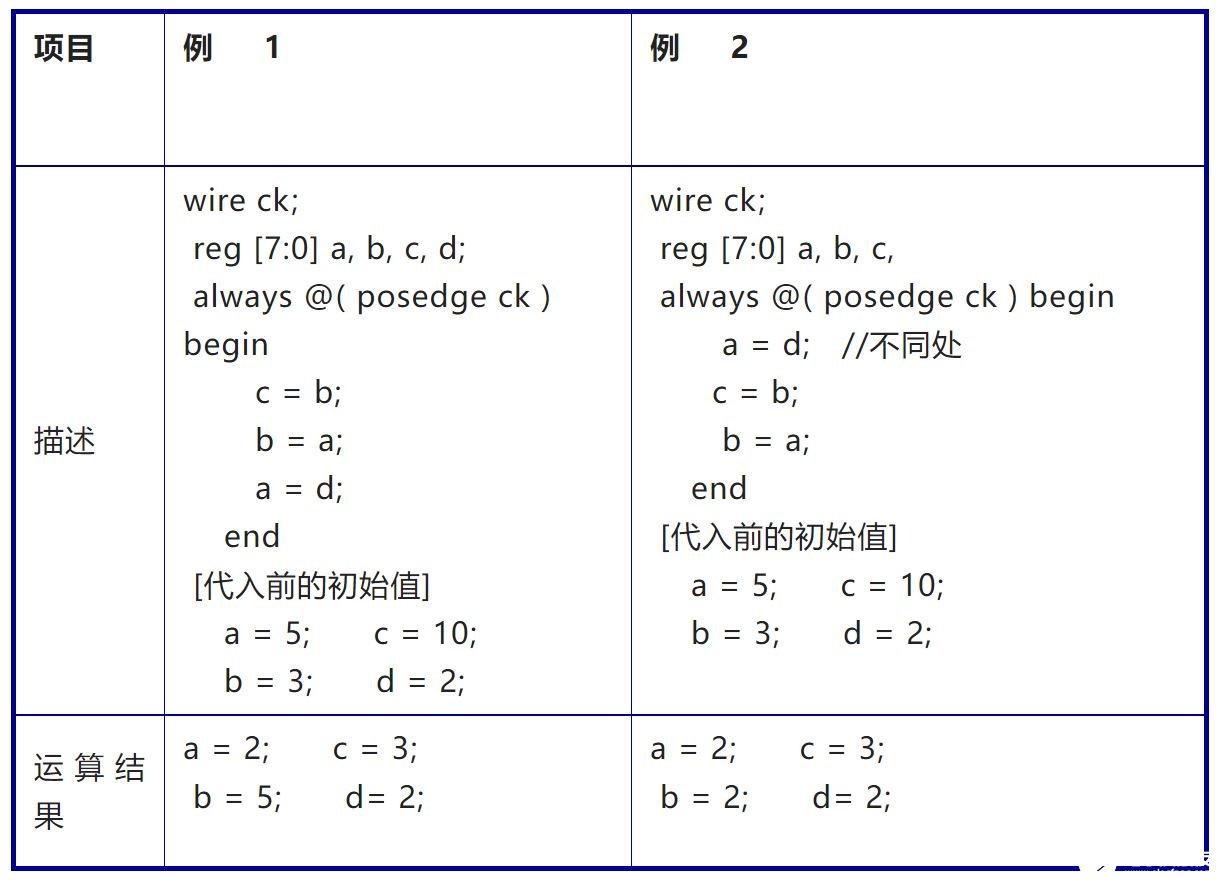

1、阻塞賦值

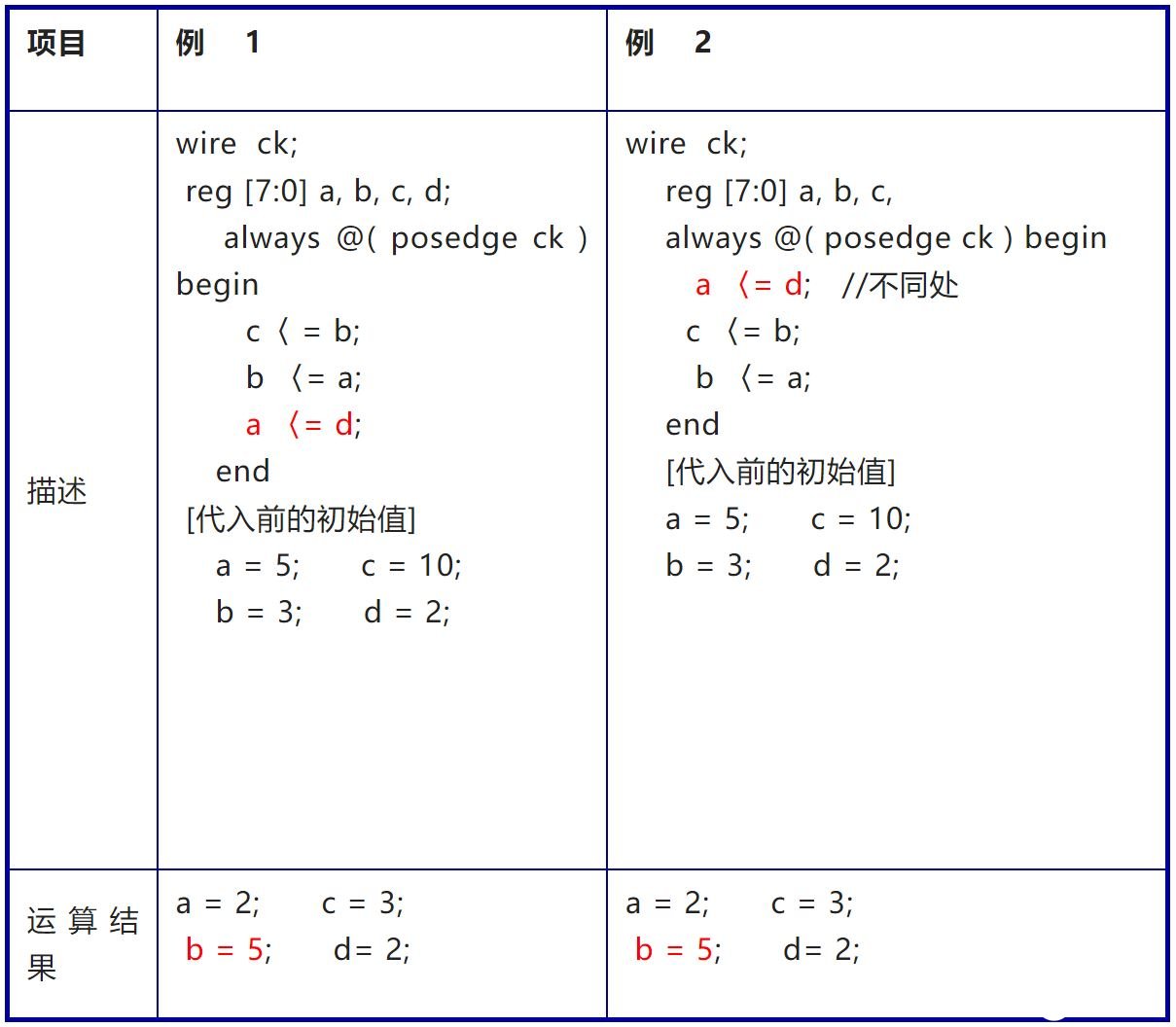

2、非阻塞賦值

四、總結(jié)

綜上所述,明德?lián)P至簡(jiǎn)設(shè)計(jì)法提出這樣的規(guī)則:

時(shí)序邏輯用非阻塞賦值

組合邏輯用阻塞賦值。

審核編輯:湯梓紅

-

變量

+關(guān)注

關(guān)注

0文章

614瀏覽量

28859 -

阻塞賦值

+關(guān)注

關(guān)注

0文章

10瀏覽量

9244 -

非阻塞賦值

+關(guān)注

關(guān)注

0文章

11瀏覽量

10066

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA基礎(chǔ)篇(一):阻塞與非阻塞賦值,不只是比原始信號(hào)差一個(gè)時(shí)鐘周期的問題!(深入剖析)

Verilog語言中阻塞和非阻塞賦值的不同

【技巧分享】FPGA至簡(jiǎn)設(shè)計(jì)-阻塞賦值與非阻塞賦值

FPGA學(xué)習(xí)系列:5.阻塞賦值與非阻塞賦值

阻塞賦值和非阻塞賦值的用法一篇文章就夠了

verilog中阻塞賦值和非阻塞賦值到底有什么區(qū)別

IEEE Verilog阻塞賦值和非阻塞賦值的區(qū)別

簡(jiǎn)述阻塞賦值和非阻塞賦值的可綜合性

一文了解阻塞賦值與非阻塞賦值

一文了解阻塞賦值與非阻塞賦值

評(píng)論