阻塞與非阻塞賦值

首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執(zhí)行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續(xù)程序的執(zhí)行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看,被賦值對象會比賦值對象差一個時鐘周期。

有了上述理解之后,我們就很容易明白為什么阻塞賦值的對象會立即發(fā)生改變,在fpga中我們多接觸到的是時序電路,并不希望被賦值對象立即改變,所以有對于組合電路而言,常用阻塞賦值,時序電路常用非阻塞賦值。

先看一個大家都熟悉的例子:

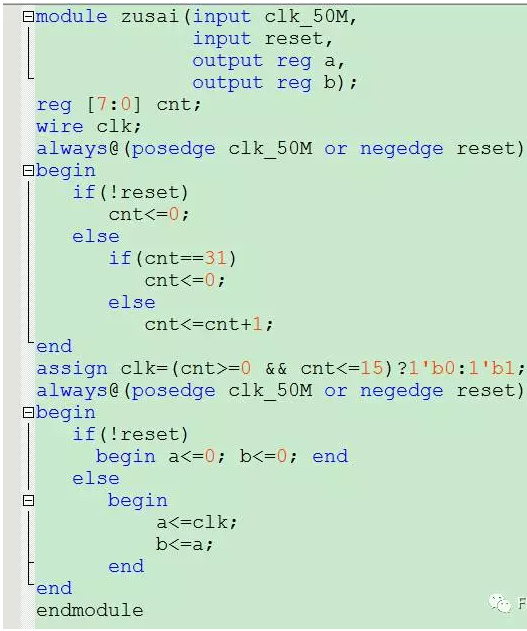

先看非阻塞代碼:

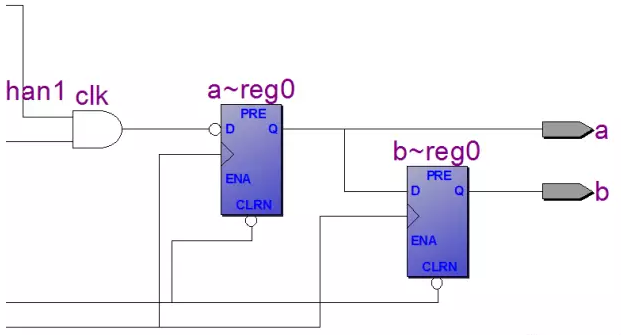

clk為主時鐘分頻之后的時鐘,clk先賦值給a,然后a在賦值給b,看一看生成的電路圖

可以看出是兩個觸發(fā)器,而且前一個觸發(fā)器的輸出是后一個觸發(fā)器的輸入,再來看看阻塞的

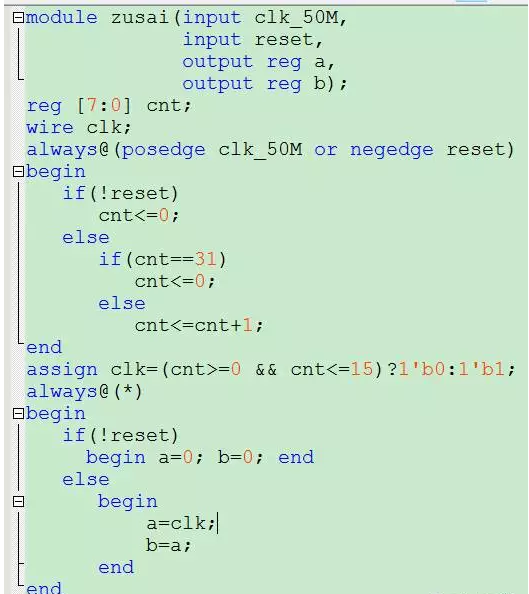

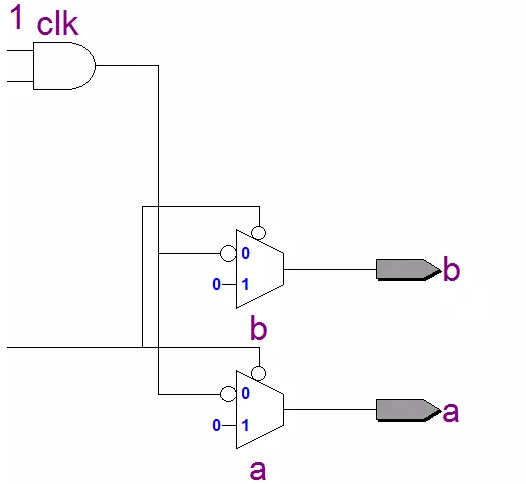

由于完全為組合電路并未有觸發(fā)器產(chǎn)生,從仿真結(jié)果來看兩種的區(qū)別

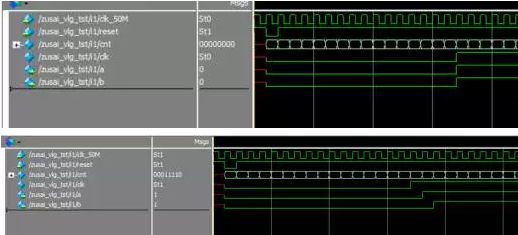

相信大家能夠很容易看出哪個是阻塞的,哪個是非阻塞的,從非阻塞的時序來看,a比clk延遲了一個主時鐘,b比a又延遲了一個主時鐘,這不是我想說的重點(diǎn),我想讓大家看看a和b是什么時候開始發(fā)生變化的,教材上一直說是當(dāng)整個進(jìn)程結(jié)束時,a和b的值才發(fā)生更新,試問你知道什么時候進(jìn)程結(jié)束么?從仿真結(jié)果來看,還不如理解為,在每個時鐘的上升沿到來時a,b的值立即改變,只不過比原始信號差一個時鐘周期。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22016瀏覽量

616889

發(fā)布評論請先 登錄

Verilog語言中阻塞和非阻塞賦值的不同

fpga基礎(chǔ)篇(一):阻塞與非阻塞賦值

【技巧分享】FPGA至簡設(shè)計(jì)-阻塞賦值與非阻塞賦值

verilog中阻塞賦值和非阻塞賦值

阻塞賦值和非阻塞賦值的用法一篇文章就夠了

IEEE Verilog阻塞賦值和非阻塞賦值的區(qū)別

簡述阻塞賦值和非阻塞賦值的可綜合性

FPGA基礎(chǔ)篇(一):阻塞與非阻塞賦值,不只是比原始信號差一個時鐘周期的問題!(深入剖析)

FPGA基礎(chǔ)篇(一):阻塞與非阻塞賦值,不只是比原始信號差一個時鐘周期的問題!(深入剖析)

評論