來源:EETOP

作者:Daniel Payne

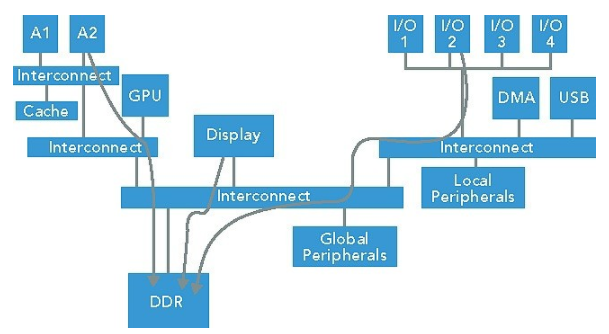

移動電話技術(shù)的進步不斷挑戰(zhàn)極限,要求SoC在提供不斷提升的性能的同時,還能保持較長的電池續(xù)航時間。為了滿足這些需求,業(yè)界正在逐步采用更低的技術(shù)節(jié)點,目前的設(shè)計都是在5納米或更低的工藝下完成的。在這些更低的幾何尺寸下設(shè)計和驗證時鐘帶來了越來越多的復(fù)雜性和驗證挑戰(zhàn)。在這種快速發(fā)展的形勢下,必須重新評估當前的時鐘驗證方法,以確保最佳的時鐘性能和可靠性。

現(xiàn)有的時鐘方法主要依賴靜態(tài)時序分析 (STA) 作為獨立解決方案或更高級的方法,將 STA 與 SPICE 模擬器結(jié)合起來分析關(guān)鍵路徑。此流程需要 CAD 部門的參與來建立流程和嚴格的方法來產(chǎn)生準確且及時的結(jié)果,但即便如此,對于較低工藝節(jié)點的 SoC 級時鐘信號,仿真可能缺乏容量和/或精度要求。而且,關(guān)鍵路徑的識別很大程度上依賴于工程師的判斷和經(jīng)驗。這種方法會導(dǎo)致不必要的guard-banding,從而使寶貴的時序裕度未被利用,限制了整體性能。

在 7nm、5nm 和 3nm 工藝節(jié)點,晶體管和互連尺寸均減小,從而導(dǎo)致對各種設(shè)計和工藝相關(guān)問題的敏感性,例如軌到軌故障和時鐘信號中的占空比失真。

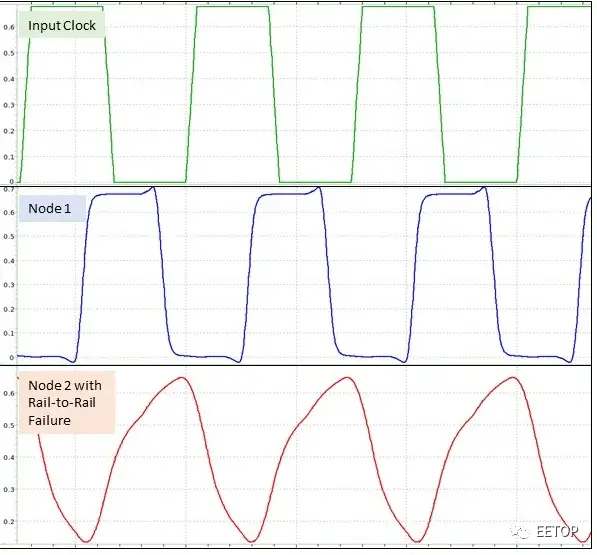

軌到軌故障(Rail to Rail Failure)

如果時鐘網(wǎng)絡(luò)的驅(qū)動器較弱、互連較長且電容負載較大,則可能會導(dǎo)致插入延遲增加,最壞的情況會導(dǎo)致軌到軌故障。在軌到軌故障中,時鐘上的電壓電平根本達不到 VSS 和 VDD 電平。單獨運行 STA 不會檢測到這種故障機制,因為 STA 在特定電壓閾值下測量時序。

時鐘頻率的增加會減少時鐘周期,從而縮短時鐘達到電源軌電壓電平的時間窗口。電壓縮放還使時鐘信號更容易受到軌到軌故障的影響,因為電源和 Vth 之間的間隙較小會導(dǎo)致非線性操作增加,從而降低驅(qū)動強度。即使 Vth 的工藝變化、晶體管 W 和 L 變化或寄生電容也會導(dǎo)致軌到軌故障。本地電源電平會因 IR 壓降效應(yīng)而反彈,從而降低時鐘信號中的信號電平和時序。

時鐘軌到軌故障檢測

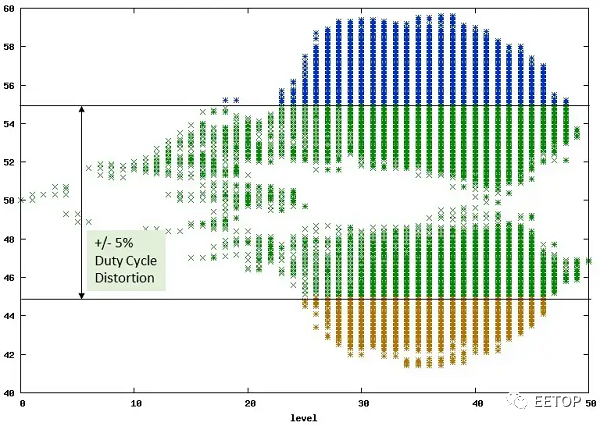

時鐘占空比失真

當時鐘信號通過一系列具有不對稱上拉和下拉驅(qū)動強度的門傳播時,會導(dǎo)致占空比失真(DCD)。時鐘的理想占空比是 50% 低脈沖寬度和 50% 高脈沖寬度。增加時鐘頻率會加劇時序不平衡并導(dǎo)致 DCD 等信號完整性問題。時鐘互連受到電容效應(yīng)和電阻效應(yīng)的影響,這些效應(yīng)會改變上升時間和下降時間的轉(zhuǎn)換速率,延遲時鐘并導(dǎo)致不對稱,從而使 DCD 效應(yīng)更加明顯。工藝變化直接改變互連,增加電路時序的不平衡,增加 DCD。

時鐘占空比失真

對于具有不對稱 PVT 角的工藝節(jié)點,DCD 變得更加明顯。STA 工具的結(jié)果主要關(guān)注插入延遲,因此報告 DCD 和最小脈沖寬度 (MPW) 的準確性較低。

轉(zhuǎn)換速率和過渡失真

在較低的工藝節(jié)點,寄生互連具有更明顯的電阻屏蔽和電容耦合,降低了轉(zhuǎn)換速率和時鐘沿轉(zhuǎn)換。STA 工具使用簡化的互連寄生模型,該模型可能會低估時鐘信號的衰減。

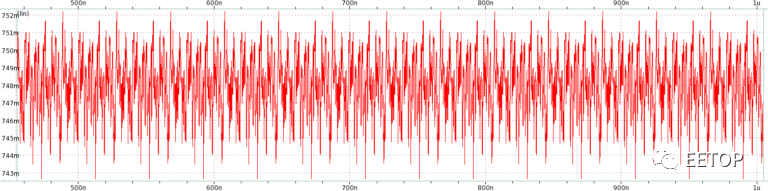

電源引起的抖動

供電網(wǎng)絡(luò) (PDN) 中的噪聲會影響時鐘時序,產(chǎn)生抖動,從而影響時鐘性能。當電源經(jīng)歷波動或噪聲時,它會引入電壓變化,直接影響時鐘信號的穩(wěn)定性和完整性。電源引起的抖動可能會導(dǎo)致時鐘信號出現(xiàn)定時錯誤,導(dǎo)致它們比預(yù)期提前或晚到達。這可能會導(dǎo)致建立和保持違規(guī),從而導(dǎo)致時鐘中潛在的功能故障。增加的抖動還會降低時序余量,使設(shè)計更容易受到時序違規(guī)和潛在性能下降的影響。STA 工具主要側(cè)重于基于電路的靜態(tài)表示來分析設(shè)計的時序行為,而不能分析抖動。設(shè)計人員通常使用抖動效應(yīng)的近似值,

電源噪聲

使用時鐘網(wǎng)格和主干的拓撲

網(wǎng)格和脊柱架構(gòu),特別是在 7 納米及以下技術(shù)節(jié)點,可以提供顯著的優(yōu)勢,包括增強的信號完整性以及功率和面積效率。網(wǎng)格和脊柱結(jié)構(gòu)為路由時鐘信號提供了規(guī)則且結(jié)構(gòu)化的框架,減少了較低技術(shù)節(jié)點工藝變化增加的影響,提高了信號完整性并減輕了時鐘偏差、抖動和噪聲等問題。此外,網(wǎng)格和脊柱架構(gòu)允許優(yōu)化時鐘信號的路由。

電路仿真是驗證網(wǎng)格和脊椎的唯一準確方法,但大多數(shù)商業(yè) SPICE 模擬器無法處理如此大的網(wǎng)格的容量。在沒有充分、快速和準確的驗證方法的情況下設(shè)計具有網(wǎng)格和脊柱的較低技術(shù)節(jié)點時鐘可能是一個危險的提議。

概括

移動設(shè)備需要移動處理器,而它們往往推動著 IC 工藝技術(shù)的前沿發(fā)展。及時實現(xiàn) PPA 目標對于移動 SoC 的成功至關(guān)重要。在 7 納米及以下技術(shù)節(jié)點,必須采用新的時鐘驗證方法。如果不采用這種方法,就會增加保護帶,從而導(dǎo)致面積和功率要求的增加。最重要的是,保護帶的保守性質(zhì),留下了寶貴的性能。

審核編輯:湯梓紅

-

驅(qū)動器

+關(guān)注

關(guān)注

54文章

8643瀏覽量

149227 -

soc

+關(guān)注

關(guān)注

38文章

4356瀏覽量

221865 -

時鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132912 -

SPICE

+關(guān)注

關(guān)注

6文章

190瀏覽量

43421 -

模擬器

+關(guān)注

關(guān)注

2文章

894瀏覽量

44089

原文標題:移動SoC的時鐘驗證

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何設(shè)計和驗證SoC

SoC設(shè)計與驗證整合

SoC驗證平臺的FPGA綜合怎么實現(xiàn)?

SoC驗證未來將朝什么方向發(fā)展?

SoC芯片驗證技術(shù)的研究

SoC驗證環(huán)境搭建方法的研究

基于FPGA的驗證平臺及有效的SoC驗證過程和方法

適用于復(fù)雜SoC的軟件定義驗證和驗證環(huán)境

SoC互連的功能和性能驗證

為什么SoC驗證一定需要FPGA原型驗證呢??

FPGA原型驗證系統(tǒng)的時鐘資源設(shè)計

淺析FPGA原型驗證系統(tǒng)的時鐘資源

SoC設(shè)計的IO PAD怎么移植到FPGA原型驗證

為什么SoC驗證一定需要FPGA原型驗證呢?

移動SoC的時鐘驗證

移動SoC的時鐘驗證

評論