摘要

物理層器件PHY(Physical Layer Interface Devices)是將各網(wǎng)元連接到物理介質(zhì)上的關(guān)鍵部件。負(fù)責(zé)完成互連參考模型(OSI)第1層中的功能,即為鏈路層實(shí)體之間進(jìn)行bit傳輸提供物理連接所需的機(jī)械、電氣、光電轉(zhuǎn)換和規(guī)程手段。其功能包括建立、維護(hù)和拆除物理電路,實(shí)現(xiàn)物理層比特bit流的透明傳輸?shù)取MǔN锢韺拥墓δ芫患稍谝粋€(gè)芯片之中,本文主要介紹了物理層的主要功能和主要接口以及以太網(wǎng)PHY芯片是如何實(shí)現(xiàn)這些功能的。

物理層(PHY)的結(jié)構(gòu)

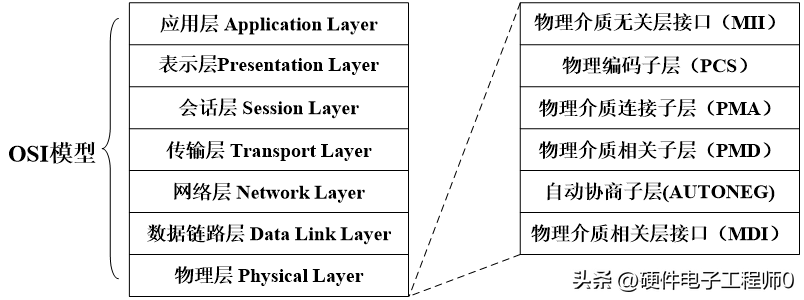

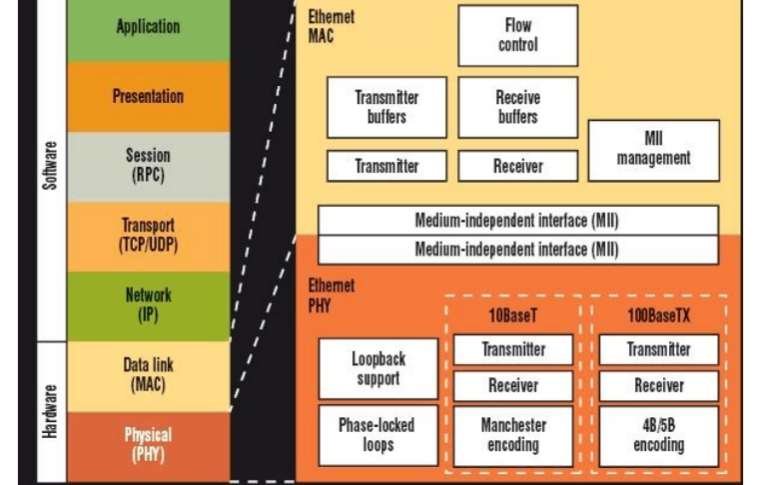

為了更好的闡述以太網(wǎng)物理層PHY芯片的主要功能,我們首先介紹一下物理層的結(jié)構(gòu)。物理層是OSI的第一層,它雖然處于最底層,卻是整個(gè)開(kāi)放系統(tǒng)的基礎(chǔ)。物理層為設(shè)備之間的數(shù)據(jù)通信提供傳輸媒體及互連設(shè)備,為數(shù)據(jù)傳輸提供可靠的環(huán)境。其功能:透明的傳送比特流;如圖1所示,物理層包括四個(gè)功能層和兩個(gè)層接口,四個(gè)功能層為:物理編碼子層、物理介質(zhì)連接子層、物理介質(zhì)相關(guān)子層和自動(dòng)協(xié)商子層;兩個(gè)層接口為物理介質(zhì)無(wú)關(guān)層接口(MII)和物理介質(zhì)相關(guān)層接口(MDI),在MII的上層是邏輯數(shù)據(jù)鏈路層(DLL),而MDI的下層則直接與傳輸介質(zhì)相連,以太網(wǎng)物理層PHY芯片實(shí)現(xiàn)的功能就是上面所提到的四層和兩個(gè)接口的功能。

圖1 物理層結(jié)構(gòu)

以太網(wǎng)PHY芯片主要功能

以太網(wǎng)中PHY芯片的種類(lèi)繁多,芯片支持的物理層規(guī)范標(biāo)準(zhǔn)也是多種多樣,數(shù)據(jù)單板上使用PHY芯片是BROADCOM公司的BCM5248和MARVELL公司的88E1111,BCM5248支持的10Base-T、100Base-TX和100Base-FX規(guī)范標(biāo)準(zhǔn),88E1111支持10Base-T、100Base-TX和1000Base-T規(guī)范標(biāo)準(zhǔn)。

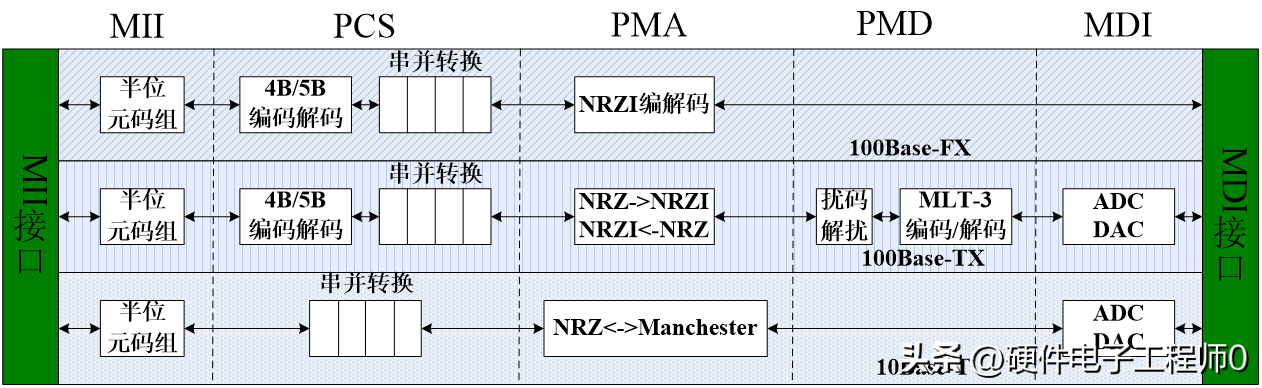

這里主要介紹了常用的10Base-T、100Base-TX和100Base-FX標(biāo)準(zhǔn)下PHY芯片主要完成的功能,如圖2所示。在10Base-T的標(biāo)準(zhǔn)下,發(fā)送數(shù)據(jù)的過(guò)程為由MAC層的數(shù)據(jù)首先經(jīng)過(guò)Manchester編碼,然后經(jīng)過(guò)串并轉(zhuǎn)換,轉(zhuǎn)換后的串行碼流經(jīng)過(guò)NRZ編碼,最后經(jīng)過(guò)DAC轉(zhuǎn)換后送到5類(lèi)雙絞線上去進(jìn)行傳輸,接受數(shù)據(jù)過(guò)程相反。

在100Base-TX的標(biāo)準(zhǔn)下,發(fā)送數(shù)據(jù)的過(guò)程為由MAC層的數(shù)據(jù)首先經(jīng)過(guò)4B/5B編碼,然后經(jīng)過(guò)串并轉(zhuǎn)換,轉(zhuǎn)換后的串行碼流經(jīng)過(guò)NRZI編碼,NRZI編碼后的數(shù)據(jù)還需要經(jīng)過(guò)擾碼和MLT-3編碼,最后經(jīng)過(guò)DAC轉(zhuǎn)換后送到5類(lèi)雙絞線或者更高的電纜上去進(jìn)行傳輸,接受數(shù)據(jù)過(guò)程相反。在10Base-T的標(biāo)準(zhǔn),發(fā)送數(shù)據(jù)的過(guò)程為由MAC層的數(shù)據(jù)首先經(jīng)過(guò)串并轉(zhuǎn)換,轉(zhuǎn)換后的串行碼流經(jīng)過(guò)NRZ編碼,再經(jīng)過(guò)Manchester編碼,最后經(jīng)過(guò)DAC轉(zhuǎn)換后送到5類(lèi)雙絞線上去進(jìn)行傳輸,接受數(shù)據(jù)過(guò)程相反。在100Base-FX的標(biāo)準(zhǔn)下,發(fā)送數(shù)據(jù)的過(guò)程為由MAC層的數(shù)據(jù)首先經(jīng)過(guò)4B/5B編碼,然后經(jīng)過(guò)串并轉(zhuǎn)換,轉(zhuǎn)換后的串行碼流經(jīng)過(guò)NRZI編碼,直接送到光纖上進(jìn)行傳輸,接受數(shù)據(jù)過(guò)程相反。下面將詳細(xì)講述各個(gè)子層和接口的功能。

圖2 在10Base-T/100Base-TX/100Base-FX標(biāo)準(zhǔn)下PHY芯片主要完成的功能

物理介質(zhì)無(wú)關(guān)層接口(MII)

MII滿(mǎn)足ISO/IEC8802-3和IEEE802.3標(biāo)準(zhǔn)的要求,支持以太網(wǎng)數(shù)據(jù)傳輸速率為10Mbit/s、100Mbit/s、1000Mbit/s或10Gbit/s。MII接口主要由與鏈路層之間的端口(MAC-PHY)和與站管理實(shí)體(STA: Station Management Entity)之間的端口(STA-PHY)兩部分組成。

3.1 MAC-PHY端口

這是MAC與PHY器件之間的接口,包括同步收發(fā)接口和介質(zhì)狀態(tài)控制接口。在介質(zhì)狀態(tài)控制接口中有載波讀出信號(hào)(CRS: Carrier Sense Signal)和碰撞檢測(cè)信號(hào)(COL: Collision Detection Signal)等。

3.2 STA-PHY端口

STA-PHY作為MII接口的一部分,用于在STA和PHY器件之間交換有關(guān)控制、狀態(tài)和配置方面的信息。為此,ISO/IEC、IEEE規(guī)范了這個(gè)雙線串行管理接口的相關(guān)協(xié)議及管理信息幀的結(jié)構(gòu)和管理寄存器的標(biāo)準(zhǔn)。

(1) 管理寄存器

按標(biāo)準(zhǔn),管理寄存器集(Management Register set)包括強(qiáng)制性“基本控制”寄存器(Mandatory “Basic Control” Registers)、狀態(tài)寄存器(Status Registers)和專(zhuān)用擴(kuò)展寄存器ICS(Specific Extended Registers)幾部分。

(2) 管理信號(hào)幀結(jié)構(gòu)

管理接口是一個(gè)雙向串行接口,用于交換PHY與STA之間的配置、控制和狀態(tài)數(shù)據(jù),利用定義的寄存器集來(lái)實(shí)現(xiàn)PHY和STA的數(shù)據(jù)交換。STA可以啟動(dòng)所有的處理功能。ISO/IEC、IEEE對(duì)串行管理數(shù)據(jù)流定義了相關(guān)管理幀結(jié)構(gòu)和協(xié)議。

3.3 常用PHY芯片的MII接口

常用PHY芯片的物理介質(zhì)無(wú)關(guān)層接口包括:媒質(zhì)無(wú)關(guān)接口(MII: Medium Independent Interface)、簡(jiǎn)化媒質(zhì)無(wú)關(guān)接口(RMII: Reduced Media Independent Interface)、串行媒質(zhì)無(wú)關(guān)接口(SMII: Serial Media Independent Interface)、源同步串行媒質(zhì)無(wú)關(guān)接口(SS-SMII: Source Synchronous-Serial Media Independent Interface)、千兆媒質(zhì)無(wú)關(guān)接口(GMII: Gigabit Media Independent Interface)、簡(jiǎn)化千兆媒質(zhì)無(wú)關(guān)接口(RGMII: Reduced Gigabit Media Independent Interface)和串行千兆媒質(zhì)無(wú)關(guān)接口(SGMII: Serial Gigabit Media Independent Interface)。具體每種接口的信號(hào)定義和數(shù)據(jù)發(fā)送時(shí)序在此就不多講,實(shí)際工作過(guò)程中遇到某種接口查閱相關(guān)文檔即可。

物理編碼子層(PCS)

物理編碼子層PCS有兩個(gè)對(duì)外接口,一是與MII的接口,二是與物理介質(zhì)連接子層(PMA: Physical Medium Attachment Sublayer)的接口。PCS子層遵循ISO/IEC8802.3和IEEE802.3標(biāo)準(zhǔn),物理編碼子層的主要功能包括對(duì)信號(hào)的編碼譯碼、收發(fā)處理、管理和控制等。這里可用100Base-TX速率來(lái)討論P(yáng)CS子層要完成的功能。

4.1 PCS在100Mbit/s與10Mbit/s 下的工作模式

一般稱(chēng)10Base-T為以太網(wǎng),100Base-TX為快速以太網(wǎng),兩者信號(hào)的速率,執(zhí)行的協(xié)議以及采用的傳輸介質(zhì)均有所不同。PCS子層對(duì)于100Base-TX信號(hào)進(jìn)行4B/5B編譯碼、擾碼(Scrambled)和MLT-3編碼,將信號(hào)交換為62.5MHz的三元數(shù)據(jù),然后通過(guò)隔離變壓器送入5類(lèi)雙絞線電纜或者比5類(lèi)雙絞線電纜更好地電纜線路中傳輸。對(duì)于10Base-T信號(hào)則需進(jìn)行曼切斯特(Manchester)編譯碼和相關(guān)的處理。對(duì)100Base-TX信號(hào)和10Base-T信號(hào)處理的功能比較如表1所示。

表1 100Base-TX和10Base-T信號(hào)處理功能的比較

| 信號(hào) | 名稱(chēng) | 速率 | 協(xié)議 | 傳輸介質(zhì) | 信號(hào)主要處理過(guò)程 |

| 10Base-T | 以太網(wǎng)信號(hào) | 10 | IEEE 802.3 | 3類(lèi)UTP、STP | Manchester編碼 |

| 100Base-TX | 快速以太網(wǎng)信號(hào) | 62.5 | IEEE 802.3u | 5類(lèi)UTP、STP | 4B/5B->擾碼->MLT-3 |

4.2 PCS發(fā)送子層

這里討論10Mbit/s和100Mbit/s兩種情況。PCS發(fā)送子層的功能是編碼、碰撞檢測(cè)與并/串變換等。

4.2.1 100Mbit/s PCS發(fā)送子層

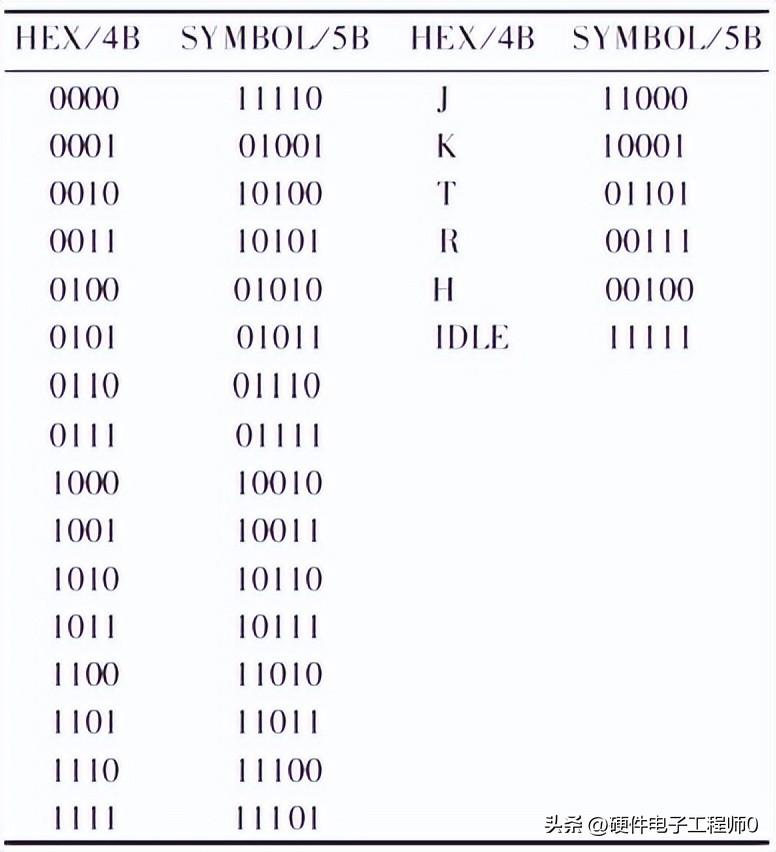

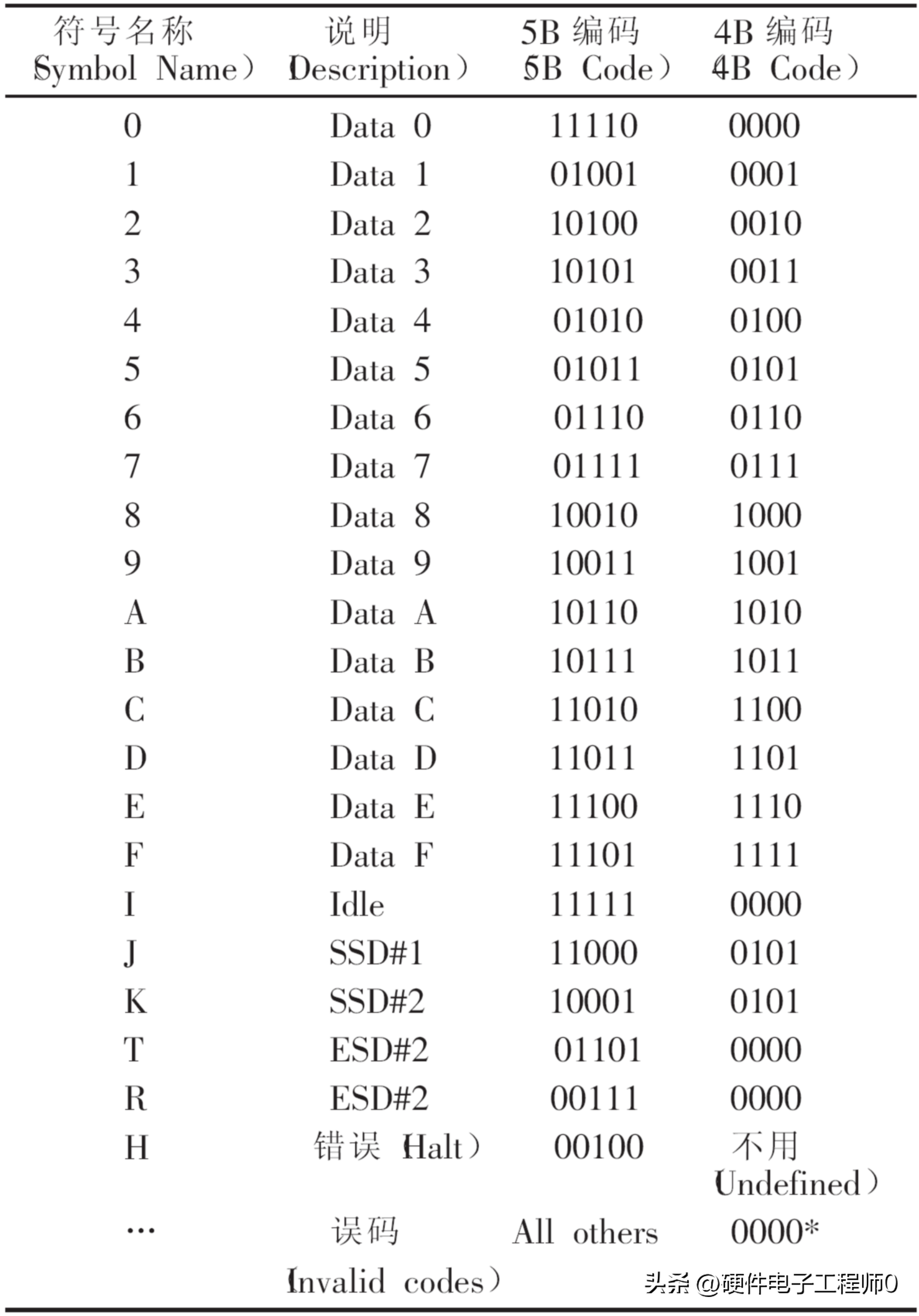

PCS發(fā)送10Base-TX的數(shù)據(jù)需要進(jìn)行4B/5B編碼,即是將4bit數(shù)據(jù)組成的奈培(nib)變換成由5bit數(shù)據(jù)組成的碼字。4B/5B編碼的目的就是將數(shù)據(jù)包的起始符、幀結(jié)束、空載與控制功能等符號(hào)都編成碼組進(jìn)行傳輸。將4B碼的nib映射入5B碼字的過(guò)程是按IEEE 802.3標(biāo)準(zhǔn)規(guī)范進(jìn)行的。

每個(gè)MAC/Repeater幀的前16nib(16×4=64bit)表示幀前序(Frame Preamble)。PCS將前二個(gè)奈培用數(shù)據(jù)流起始標(biāo)幟符/J/K/代替,并在幀結(jié)束時(shí)加入數(shù)據(jù)流結(jié)束標(biāo)幟符/T/R/,用于表示包的結(jié)束(ESD: End-of-Stream Delimiter)。4B/5B編碼器同樣在包之間填充間隔空信號(hào)(Idle Period)。用間隔空(Idle)符號(hào)實(shí)現(xiàn)數(shù)據(jù)流的連續(xù)性。表2即是4B/5B編碼表,編碼后的符號(hào)送入后面的擾碼器。

表2 4B/5B編碼表

PCS發(fā)送的子層4B/5B編碼,有32種5bit的編碼組合,其中16種5bit組合用于表示原16捉nib(4bit)的組合;另16種5bit組合,IEEE標(biāo)準(zhǔn)定義了6種用于控制使用的組合,還有10種認(rèn)為非法的組合。IEEE定義的6種控制碼組是:

1. /H/表示一個(gè)發(fā)送差錯(cuò);

2. /I/表示一個(gè)IDLE空載;

3. 兩個(gè)碼組表示數(shù)據(jù)流起始標(biāo)識(shí)符(SSD);

4. /J/和/K/;

5. 兩個(gè)碼組表示數(shù)據(jù)流結(jié)束標(biāo)幟符(ESD);

6. /T/和/R/;

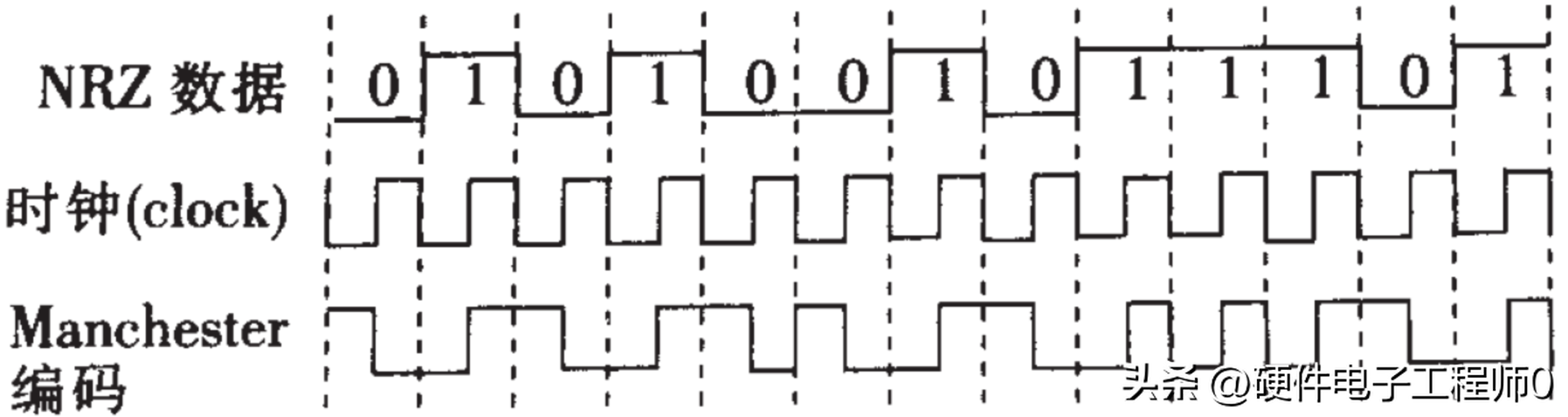

4.2.2 10Mbit/s的PCS發(fā)送子層

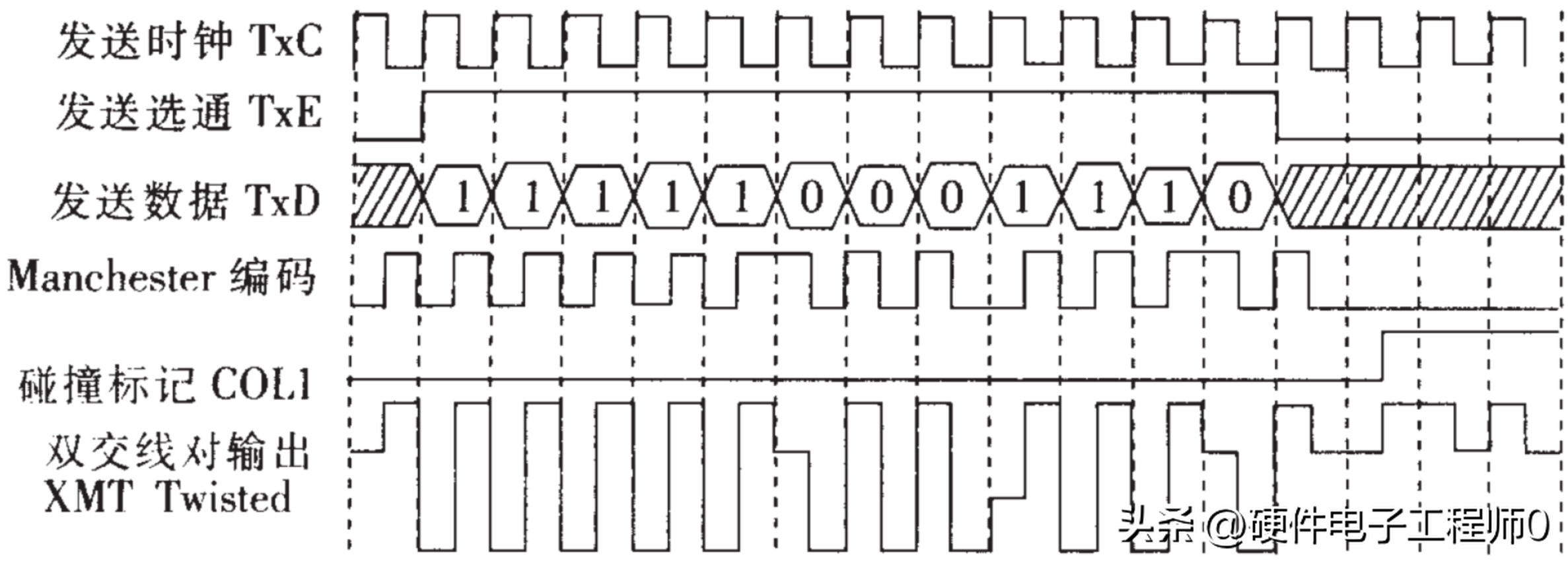

按ISO/IEC、IEEE標(biāo)準(zhǔn)的要求,10Mbit/s的PCS發(fā)送子層采用Manchester編碼,即利用數(shù)據(jù)與時(shí)鐘相“異或”,使數(shù)據(jù)每bit的前一半CLK取數(shù)據(jù)的補(bǔ)碼,后一半CLK取數(shù)據(jù)的原碼,從而保證躍變沿總是發(fā)生在每bit的中央處。Manchester編碼器在數(shù)據(jù)包結(jié)束后加入一個(gè)起始空脈沖(SOI: Start of Idle Pulse)。在編碼過(guò)程中包與包之間的間隔則不進(jìn)行編碼,由鏈路脈沖填充。Manchester編碼過(guò)程的時(shí)間關(guān)系如圖3所示。

圖3 Manchester編碼過(guò)程的時(shí)間關(guān)系圖

從MAC/Repeater接口來(lái)的4bit的nib流或串行bit流,利用Manchester編碼進(jìn)行編碼。編碼的邏輯是:

1、二進(jìn)制NRZ數(shù)據(jù)“1”

當(dāng)碼元(bit)周期前半周期時(shí)取負(fù)值;

當(dāng)碼元(bit)周期后半周期時(shí)取正值。

2、二進(jìn)制NRZ數(shù)據(jù)“0”

當(dāng)碼元(bit)周期前半周期時(shí)取正值;

當(dāng)碼元(bit)周期后半周期時(shí)取負(fù)值。

使用Manchester編碼的優(yōu)點(diǎn),一是每個(gè)bit周期可有一編碼時(shí)鐘;二是不必考慮數(shù)據(jù)本身是“0”還是“1”,增加了數(shù)據(jù)的躍變沿。但它的缺點(diǎn)是編碼后的數(shù)據(jù)率增加了一倍。

PCS子層還可完成碰撞檢測(cè),即在數(shù)據(jù)傳輸和接收同時(shí)發(fā)生時(shí),需按標(biāo)準(zhǔn)規(guī)范和根據(jù)工作模式進(jìn)行處理。在半雙工工作模式下,發(fā)生碰撞時(shí)產(chǎn)生檢測(cè)信號(hào)(COL: Collision Detection Signal),而在全雙工工作模式下,不產(chǎn)生COL。

4.3 PCS接收子層

4.3.1 PCS接收子層的功能

PCS接收子層主要完成以下功能:

串/并變換;載波檢測(cè);4B/5B或Manchester譯碼;碼組成幀。

即PCS接收子層狀態(tài)機(jī)連續(xù)接收從PMA來(lái)的數(shù)據(jù),將其由串行變換為并行,以及成幀和譯碼,之后送到MAC/Repeater接口。接收狀態(tài)機(jī)則在接收和數(shù)據(jù)狀態(tài)判斷之間進(jìn)行轉(zhuǎn)換并連續(xù)這個(gè)過(guò)程,直到發(fā)生下述情況之一時(shí)為止:

數(shù)據(jù)流結(jié)束標(biāo)幟符(ESD,即/T/R/符號(hào));

有差錯(cuò)發(fā)生;

過(guò)早結(jié)束(空號(hào))。

依據(jù)ESD,接收狀態(tài)機(jī)返回到Idle狀態(tài)時(shí),ESD并沒(méi)有被送入MAC/Repeater接口,因此檢測(cè)出的差錯(cuò)將迫使接收狀態(tài)機(jī)宣告接收錯(cuò),并等待后面符號(hào)。若接收狀態(tài)機(jī)檢出“過(guò)早結(jié)束信號(hào)(Premature end)”,同樣也要宣告接收錯(cuò),而返回Idle狀態(tài)。

4.3.2 100Mbit/s的PCS接收子層4B/5B譯碼

由于從雙絞線對(duì)輸入的數(shù)據(jù)在發(fā)端進(jìn)行了4B/5B編碼,因此在接收端必須利用4B/5B譯碼器進(jìn)行譯碼,即將5B碼組映射成4B碼。4B/5B譯碼器的輸入來(lái)自解擾器(Descrambler)。按表3所示,將5bit碼組變換為4bit的nib。4B/5B譯碼器應(yīng)首先將SSD幀符(/J/K/符號(hào))拆除并用兩個(gè)4B數(shù)據(jù)“5”nb(/5/符號(hào))來(lái)代替,對(duì)ESD幀符(/T/R/符號(hào))也需要被拆除并用兩個(gè)4B數(shù)據(jù)“0”nib(/I/符號(hào))代替。

表3 4B/5B符號(hào)譯碼表

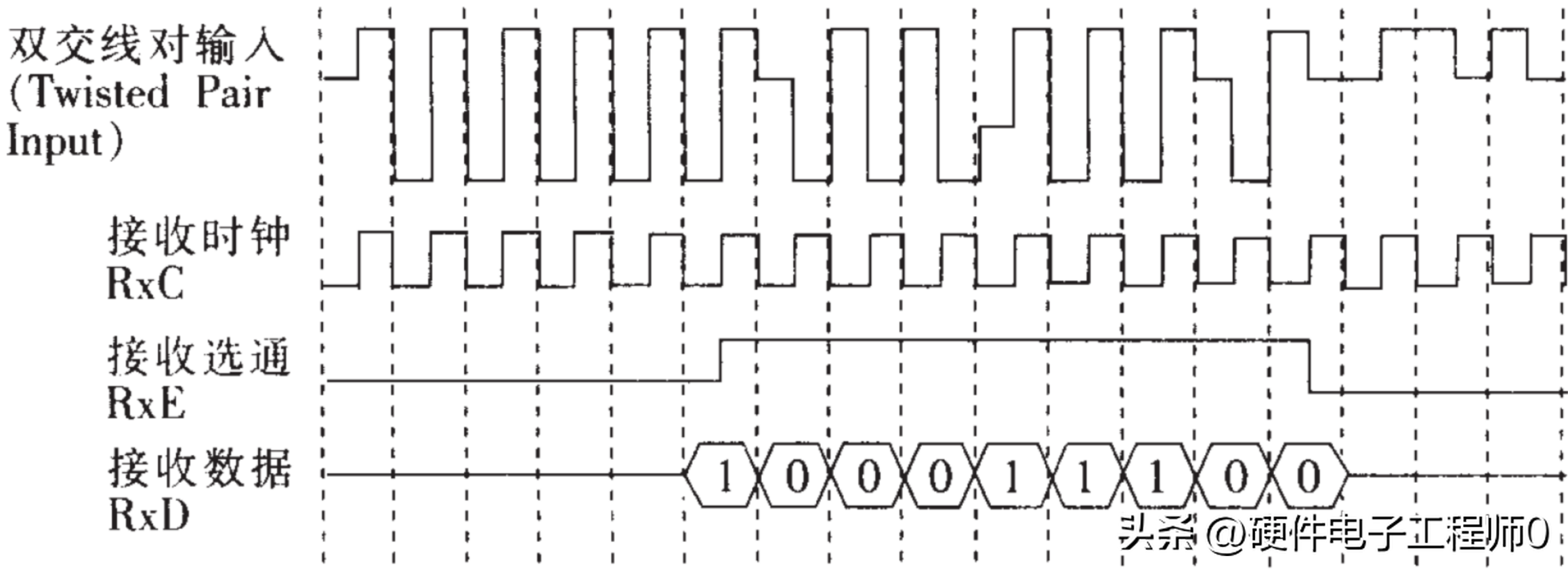

10Mbit/s PCS接收子層Manchester譯碼

Manchester譯碼器將從雙絞線對(duì)接收到的Manchester編碼信號(hào)變換為原NRZ信號(hào),并將空載開(kāi)始脈沖(SOI: Start of Idle)拆除。在發(fā)送端,NRZ數(shù)據(jù)被Manchester編碼,即數(shù)據(jù)和時(shí)鐘相異或。在接收端,數(shù)據(jù)再次和時(shí)鐘相異或,就可以恢復(fù)出原始數(shù)據(jù)。圖4、圖5即為ML2653型10Base-T物理接口芯片發(fā)收Manchester信號(hào)編譯碼的定時(shí)圖。

圖4 發(fā)送系統(tǒng)定時(shí)圖

圖5 接收系統(tǒng)定時(shí)圖

PCS子層提供CRS載波檢測(cè)信號(hào)(Carrier Sense Signal)和碰撞檢出信號(hào)(Collision Detection Signal),用這兩個(gè)控制信號(hào)實(shí)現(xiàn)對(duì)MII接口的控制與管理。

物理介質(zhì)連接子層(PMA)

PMA與PCS及PMD子層相連,因此必須有兩個(gè)接口:一個(gè)是到上邊PCS子層的接口,另一個(gè)是到下邊PMD子層的接口。PMA子層主要功能是:

(1) 鏈路監(jiān)測(cè)(Link Monitoring);

(2) 載波檢測(cè)(Carrier Detecting);

(3) NRZI編/譯碼(NRZI En-coding/Decoding);

(4) 發(fā)送時(shí)鐘合成(Transmit Clock Synthesis);

(5) 接收時(shí)鐘恢復(fù)(Receive Clock Recovery);

5.1 PMA發(fā)送子層

PMA發(fā)送子層(PMA Transmit Sublayer)從PCS子層接收串行比特流并且將其變換為NRZI格式(10Mbit/s不用),然后將其送入物理介質(zhì)相關(guān)子層(PMD)。

PMA使用數(shù)字鎖相環(huán)(PLL)合成技術(shù),從時(shí)鐘標(biāo)準(zhǔn)接口得到需要發(fā)送的時(shí)鐘脈沖,并根據(jù)標(biāo)準(zhǔn)時(shí)鐘接口的安排,得到不同的發(fā)送時(shí)鐘值。

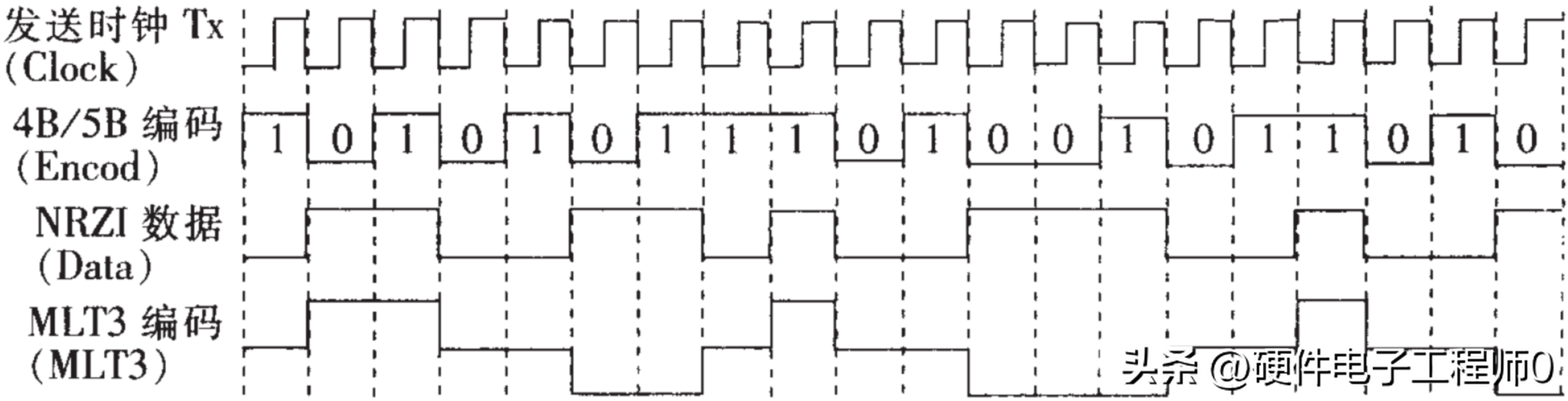

在PMA發(fā)送子層需進(jìn)行NRZI(Non Return to Zero Inverter)編碼,這是一種兩電平的單極性(O和V)編碼。用兩電平之間的躍變表示數(shù)據(jù)“1”,無(wú)躍變表示“0”。在這里NRZI編碼為將數(shù)據(jù)變換成MLT-3編碼作了準(zhǔn)備。具體實(shí)例如圖6所示。

圖6 NRZI和MLT-3編碼波形實(shí)例

5.2 PMA接收子層

PMA接收子層主要完成下面兩個(gè)功能:

(1) NRZI譯碼(NRZI Decoding/10Mbit/s不用): 即將從PMD子層接收的串行bit流進(jìn)行NRZI譯碼,并將其變換成單極性的二進(jìn)進(jìn)PCS子層。

(2)接收時(shí)鐘恢復(fù)(Receive Clock Recovery): 即接收時(shí)鐘恢復(fù)是由PLL完成的,此PLL鎖定于從PMD子層接收據(jù)串行數(shù)據(jù)流上。PLL自動(dòng)同步于串行數(shù)據(jù)流并從中提取時(shí)鐘,最后將恢復(fù)時(shí)鐘和NRZI譯碼后的數(shù)據(jù)流送到PCS子層。

當(dāng)PMA接收子層沒(méi)有檢出任何接收信號(hào)時(shí),PMA利用發(fā)送時(shí)鐘作為PLL的參考標(biāo)準(zhǔn)時(shí)鐘。在100Base-TX信號(hào)情況下,恢復(fù)出25MHz的時(shí)鐘。而在10Base-T信號(hào)時(shí)時(shí)鐘信號(hào)則是2.5MHz。

PMA接收子層的鏈路監(jiān)視功能(Link Monitoring Function)可以來(lái)監(jiān)視接收時(shí)鐘PLL。若接收時(shí)鐘PLL沒(méi)有捕獲鎖定的串行數(shù)據(jù)流,則產(chǎn)生一個(gè)差錯(cuò)信號(hào)。在一般情況下,PMA鏈路監(jiān)視功能塊是連續(xù)統(tǒng)計(jì)與其連接的鏈路狀態(tài)。若沒(méi)有檢出接收信號(hào)或者PLL誤幀,則宣告接收通道差錯(cuò)。

物理介質(zhì)相關(guān)子層(PMD)

這里主要介紹100Base-TX速率下的雙絞線對(duì)物理介質(zhì)相關(guān)天的子層(TP-PMD:Twisted-Pair Physical Media Dependent)。按照ISO/IEC IEEE的標(biāo)準(zhǔn),100Base-TX TP-PMD具有對(duì)數(shù)據(jù)流擾碼、解憂(yōu)碼、三電平、多躍變沿MLT-3編譯碼功能及對(duì)接收信號(hào)進(jìn)行直流恢復(fù)和自血壓計(jì)勻衡。

6.1 數(shù)據(jù)流的擾碼器/解擾器

在通常情況下,數(shù)字傳輸系統(tǒng)的魯棒性(Robustness)依賴(lài)于數(shù)字信號(hào)源的統(tǒng)計(jì)特性。例如,接收時(shí)鐘是從接收數(shù)據(jù)提取得來(lái)的,長(zhǎng)串“0”和“1”可能引起同步的丟失。為了使定時(shí)恢復(fù)電路處于同步狀態(tài),數(shù)據(jù)信號(hào)必須包含足夠的躍變沿。

IEEE 802.3u協(xié)議允許出現(xiàn)一些重復(fù)的數(shù)據(jù)圖形,這些重復(fù)的數(shù)據(jù)圖形在線路信號(hào)的功率頻譜密度分布中出現(xiàn)能量峰值,其不連續(xù)的頻譜分量是有害的,必須將其抑制掉。利用擾碼(Scrambling)技術(shù)擴(kuò)展這些圖形從而抑制掉這些不連續(xù)峰值分量達(dá)20dB~25dB。這是因?yàn)樵谝欢ㄖ芷跁r(shí)間內(nèi)信號(hào)數(shù)據(jù)的隨機(jī)性使得數(shù)據(jù)信號(hào)有均勻功率輸出。這樣,峰值能量被消除,從而改善了發(fā)送性能。

在發(fā)端TP-PMD子層對(duì)4B/5B編碼信號(hào)進(jìn)行擾碼。擾碼器(Scrambler)將普通的NRZ bit流利用鍵控、模2加的方法產(chǎn)生一個(gè)被擾碼的數(shù)據(jù)流。其工作過(guò)程是:一個(gè)11bit的線性反饋移位寄存器(LFSR: Linear Feedback Shift Register)的輸入是第11bit和第9bit的模2加(Exclusive-OR),移位寄存器中至少包含有一個(gè)非零bit,其產(chǎn)生的偽隨機(jī)序列可以與需要擾碼的信號(hào)相加,最后得到已擾碼的信號(hào)(10Mbit/s不用擾碼)。

解擾器(Descrambler)的作用是將被擾碼的數(shù)據(jù)進(jìn)行解擾,恢復(fù)成原NRZI數(shù)據(jù)信號(hào)。在數(shù)據(jù)解擾前,應(yīng)首先實(shí)現(xiàn)解擾器同步,一旦建立了解擾器同步,在給定的期間內(nèi),只要檢出足夠擾碼空載圖形“1”的個(gè)數(shù),即在1ms時(shí)間內(nèi)至少應(yīng)檢出25個(gè)連續(xù)解擾空信號(hào)“1”,就能保持同步狀態(tài)。若在1ms時(shí)間內(nèi)沒(méi)有檢出25個(gè)連續(xù)解擾空信號(hào)“1”,則解擾將失步,而需要重新建立同步過(guò)程。

6.2 100Base-TX MLT-3編碼器/譯碼器

MLT-3線路編碼(MLT-3 Line Code)用于使用電纜介質(zhì)的快速以太網(wǎng)。MLT-3是一種三電平雙極性編碼(+V、0和-V),用兩電平之間的躍變沿來(lái)表示“1”,而無(wú)躍變沿表示“0”。這里,MLT-3的最高基頻是NRZI的一半。使用MLT-3編碼可使高頻頻譜能量移向低于30MHz的邊緣區(qū)。與NRZI比較,MLT-3編碼90%以上的頻譜能量在40MHz以下,而NRZI則在70MHz以下。這樣,在相同數(shù)據(jù)率下,不要求有更高帶寬的傳輸介質(zhì)。

MLT-3編碼器將從擾碼器來(lái)的NRZI擾碼信號(hào)(NRZ)變換為三電平MLT-3編碼信號(hào);MLT-3譯碼器則作反變換恢復(fù)原NRZI擾碼信號(hào)。在這里從中提取了時(shí)鐘,并利用此時(shí)鐘進(jìn)行譯碼。

6.3 直流恢復(fù)(DC Restoration)

在100Base-TX數(shù)據(jù)流的擾碼和MLT-3的編碼中,可能存在一定長(zhǎng)度的連“1”或連“0”序列,使得數(shù)據(jù)流中產(chǎn)生直流分量,變壓器的隔直也會(huì)引起信號(hào)“基線”的漂移,即“基線”信號(hào)從其正常額定直流值移動(dòng)或漂移,而不利于接收機(jī)對(duì)于噪聲的抑制特性,因此需要恢復(fù)信號(hào)原直流分量。

6.4 自適應(yīng)均衡器(Adaptive Equalizer)

當(dāng)數(shù)據(jù)在電纜中傳輸時(shí),由于色散特性,將會(huì)導(dǎo)致信號(hào)失真和碼間干擾(ISI: Inter Symbol Interference),因此在接收機(jī)中必需采取措施將進(jìn)來(lái)的失真和碼間干擾信號(hào)恢復(fù)成原信號(hào)。失真的產(chǎn)生依賴(lài)于信號(hào)的頻譜和介質(zhì)環(huán)路的長(zhǎng)度。由于在多數(shù)情況下,雙絞線對(duì)(TP)端口的特性是未知的,并且每個(gè)端口要求均衡的特性也不相同,因此,在TP-PMD標(biāo)準(zhǔn)中,提出了使用自適應(yīng)均衡器恢復(fù)原信號(hào)的要求,以保證對(duì)接收信號(hào)進(jìn)行適當(dāng)?shù)难a(bǔ)償。自動(dòng)均衡的方法之一是監(jiān)視接收信號(hào)的能量,用以確定傳輸介質(zhì)的長(zhǎng)度,并據(jù)此調(diào)整均衡器的性能。因?yàn)椋邮招盘?hào)的幅度與傳輸?shù)睦|長(zhǎng)是成正比的,所以若信號(hào)電平降低,則會(huì)增加均衡的總量,而便于補(bǔ)償信號(hào)在線路中的損失。

6.5 雙絞線對(duì)發(fā)射機(jī)

一般的雙絞線對(duì)發(fā)射機(jī)(Twittered-Pair Transmitter)編碼器、波形發(fā)生器以及傳輸介質(zhì)線路驅(qū)動(dòng)器所組成。波形發(fā)生器接受MLT-3編碼波形,并使用一個(gè)電流源交換陣列來(lái)控制輸出信號(hào)上升/下降沿的時(shí)間和信號(hào)的幅度電平。為了平滑此電流型信號(hào)輸出和除去高頻分量,需通過(guò)一個(gè)低通濾波器,使發(fā)送的輸出波形滿(mǎn)足有關(guān)脈沖樣板的標(biāo)準(zhǔn)。電流驅(qū)動(dòng)型差動(dòng)驅(qū)動(dòng)器將平滑后符合要求的波形變換為可以驅(qū)動(dòng)10m、100歐姆的5類(lèi)非屏蔽雙絞線電纜或100m、150歐姆屏蔽雙絞線電纜的電流輸出。最后與傳輸介質(zhì)的接口是一個(gè)隔離變壓器。

6.6 雙絞線對(duì)接射機(jī)

一般雙絞線對(duì)接收機(jī)被制作成通用模塊,通過(guò)一個(gè)隔離變壓器與傳輸介質(zhì)連接。從雙絞線對(duì)(TP)輸入的信號(hào)首先進(jìn)入自適應(yīng)均衡器,在這里對(duì)于纜的低通特性進(jìn)行補(bǔ)償,接著進(jìn)入“基線漂移校正電路”恢復(fù)由變壓器隔去的波形直流分量。比較器將均衡后的信號(hào)變換回原數(shù)字電平供“鎮(zhèn)噪電路(Squelch Circuit)”使用。MLT-3譯碼器接收從比較器來(lái)的三電平MLT-3信號(hào)并且將其變換為常規(guī)數(shù)字?jǐn)?shù)據(jù),用來(lái)恢復(fù)時(shí)鐘和數(shù)據(jù)。其全過(guò)程如圖7 所示。

6.7 自動(dòng)極性校正與隔離變壓器

一般的100Base-TX沒(méi)有極性問(wèn)題,但是自動(dòng)協(xié)商(FLP)對(duì)于極性是比較靈敏的。自動(dòng)極性校正(Auto Polarity Correction)功能主要是應(yīng)用于10Base-T工作方式,通常利用規(guī)范鏈路脈沖(NLP: Normal Link Pulses)檢驗(yàn)信號(hào)極性,從而校正反向的信號(hào)極性。

ISO/IEC8802-3、IEEE802.3標(biāo)準(zhǔn)要求要通過(guò)隔離變壓器(Isolation Transformer)與電纜傳輸介質(zhì)連接。而典型的磁性器件模塊包含兩個(gè)隔離變壓器,一個(gè)用于雙絞線對(duì)發(fā)射機(jī),另一個(gè)用于接收機(jī)。通過(guò)這兩個(gè)隔離變壓器與傳輸介質(zhì)物理隔離和交流耦合。

7 自動(dòng)協(xié)商子層(AUTONEG)

7.1 自動(dòng)協(xié)商子層功能

自動(dòng)協(xié)商子層(AN: Auto-Negotiation Sublayer)通常有以下功能:

1、確定在鏈路段介質(zhì)或電纜連接的另一端設(shè)備所具有的能力;

2、宣布遠(yuǎn)端鏈路設(shè)備中上述能力;

3、與鏈路遠(yuǎn)端設(shè)備交換彼此表征技術(shù)能力的數(shù)據(jù)參數(shù),并且與遠(yuǎn)端鏈路設(shè)備建立協(xié)議,自動(dòng)選擇共有的最高性能工作模式。包括工作速率(10/100/1000Mbit/s)、傳輸介質(zhì)和半/全雙工模式。

自動(dòng)協(xié)商功能是在建立鏈路兩端設(shè)備中選擇共有的最高性能工作的模式,其算法和鏈路完整性算法的區(qū)別在于:標(biāo)準(zhǔn)鏈路完整性算法僅用于建立來(lái)往遠(yuǎn)端設(shè)備的活動(dòng)鏈路,而自動(dòng)協(xié)商算法則是在選擇兩端共有的最高性能后,還要建立來(lái)往遠(yuǎn)端設(shè)備的激活鏈路。

7.2 自動(dòng)協(xié)商子層的啟動(dòng)

在以下事件之一發(fā)生時(shí),需啟動(dòng)自動(dòng)協(xié)商功能算法:

1、設(shè)備選通自動(dòng)協(xié)商功能;

2、設(shè)備進(jìn)入鏈路故障(Fail)狀態(tài);

3、自動(dòng)協(xié)商復(fù)位。

在ISO/IEC 8802-3標(biāo)準(zhǔn)的附錄28B中,列出了各種技術(shù)的優(yōu)先權(quán)順序,如下所示:

100Base-TX全雙工(最高優(yōu)先權(quán));

100Base-T4;

100Base-TX半雙工;

10Baed-T全雙工;

10Base-T半雙工(最低優(yōu)先權(quán))。

一般地說(shuō),自動(dòng)協(xié)商執(zhí)行的過(guò)程要小于500ms,這與對(duì)端完成自動(dòng)協(xié)商鏈路的能力無(wú)關(guān)。自動(dòng)協(xié)商過(guò)程的監(jiān)視器可以監(jiān)視自動(dòng)協(xié)商過(guò)程和鏈路是否建立。

總結(jié)

PHY物理層器件應(yīng)滿(mǎn)足CSMA/CD以太網(wǎng)ISO/IEC 8802-3的標(biāo)準(zhǔn)要求。前面分別詳細(xì)描述了MII接口、物理編碼子層(PCS)、物理介質(zhì)連接子層(PMA)、物理介質(zhì)相關(guān)子層(PMD)以及自動(dòng)協(xié)商(Auto-Negotiation)功能和原理。現(xiàn)將各部分功能概括于表1之中,以進(jìn)行比較。

表4 以太網(wǎng)物理層PHY芯片功能表

| MII | PCS | PMA | TP-PMD | AUTONEG | MDI |

| 接MAC/PHY端口;接STA/PHY管理端口 |

4B/5B編譯碼 (100Mbit/s); 碰撞檢測(cè); 串并轉(zhuǎn)換; Manchester編譯碼(10Mbit/s); MAC/Repeater接口控制 |

鏈路監(jiān)測(cè); 載波監(jiān)測(cè); NRZI/NRZ編譯碼(100Mbit/s); 時(shí)鐘合成/恢復(fù) |

擾碼/解擾(100Mbit/s); NRZI/MLT-3編譯碼(100Mbit/s); 直流恢復(fù); 自動(dòng)極性校正; 發(fā)送/接收變壓器隔離 |

NLP鏈路完整性(主要用于10Mbit/s); FLP自動(dòng)協(xié)商 |

與傳輸介質(zhì)相 |

審核編輯:劉清

-

編碼器

+關(guān)注

關(guān)注

45文章

3780瀏覽量

137317 -

寄存器

+關(guān)注

關(guān)注

31文章

5425瀏覽量

123558 -

PHY

+關(guān)注

關(guān)注

2文章

315瀏覽量

52555 -

以太網(wǎng)技術(shù)

+關(guān)注

關(guān)注

0文章

17瀏覽量

8154 -

DLL函數(shù)

+關(guān)注

關(guān)注

0文章

5瀏覽量

1664

發(fā)布評(píng)論請(qǐng)先 登錄

一文詳解以太網(wǎng)MAC芯片與PHY芯片

以太網(wǎng)PHY市場(chǎng)快速增長(zhǎng),國(guó)產(chǎn)PHY芯片繼續(xù)突破

以太網(wǎng)MAC芯片與PHY芯片的關(guān)系是什么

以太網(wǎng)芯片MAC和PHY的關(guān)系 精選資料分享

請(qǐng)問(wèn)如何更換以太網(wǎng)PHY芯片?

如何對(duì)以太網(wǎng)PHY芯片的rmii pin腳進(jìn)行配置

車(chē)載以太網(wǎng)MAC和PHY的問(wèn)題詳解

裕太微電子推出兩款自主研發(fā)的國(guó)產(chǎn)以太網(wǎng)PHY芯片

車(chē)載以太網(wǎng)PHY標(biāo)準(zhǔn)分布

如何選擇適合的以太網(wǎng)PHY

一文詳解車(chē)載以太網(wǎng)PHY芯片

還在為以太網(wǎng)PHY缺芯改版煩惱嗎?

【科普】一文讀懂以太網(wǎng)PHY芯片

【科普】一文讀懂以太網(wǎng)PHY芯片

評(píng)論