Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

本文將詳細介紹如何在Vivado中配置一個FIFO IP核,以及如何調用這個FIFO IP核。

一、FIFO IP核的配置

1、新建FIFO IP

在Vivado的IP Catalog中找到FIFO Generator IP核,雙擊打開參數配置界面。

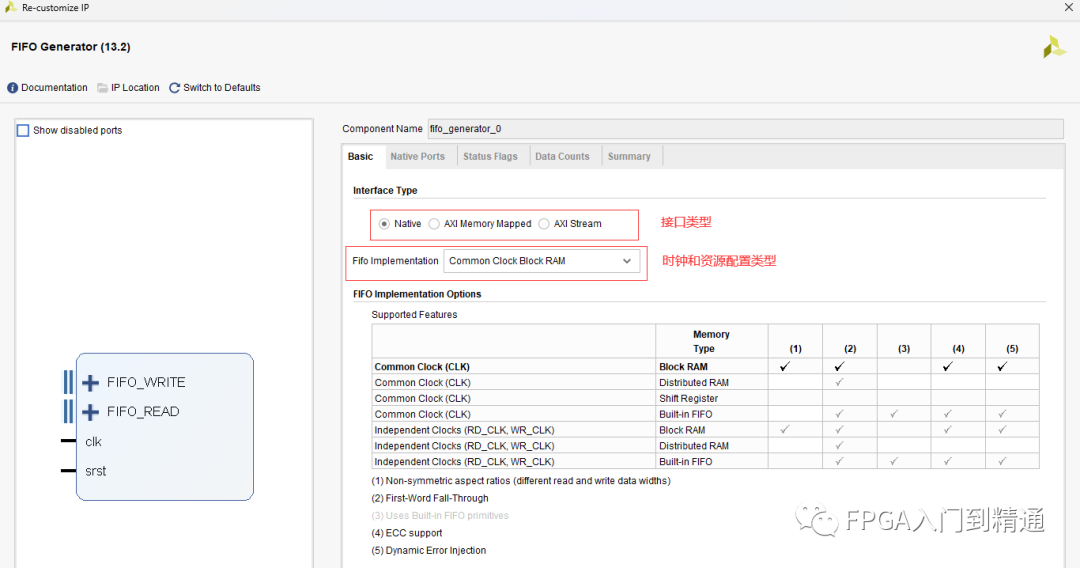

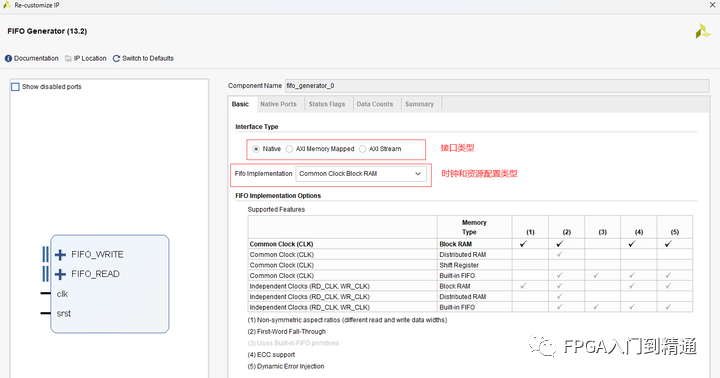

2、配置FIFO基本參數

編輯切換為居中

添加圖片注釋,不超過 140 字(可選)

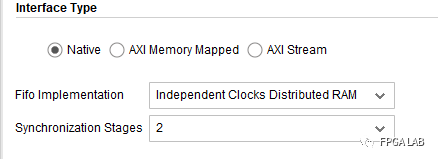

(1)接口類型

Native interface FIFOs:

這是最基本的FIFO接口,包括數據輸入、輸出端口、寫使能、讀使能等信號。

AXI Memory Mapped interface FIFOs:

這種接口將 FIFO 封裝為一個AXI內存映射的IP核,可以通過AXI總線進行訪問。

AXI4-Stream interface FIFOs:

這種接口兼容AXI4-Stream協議,適合在流式數據傳輸場景中使用。

(2)時鐘類型和資源類型

時鐘:

同步時鐘(common clock) 和 異步時鐘(Independent clock)

資源:

block RAM、Distributed RAM、Shift Register、Built-in FIFO

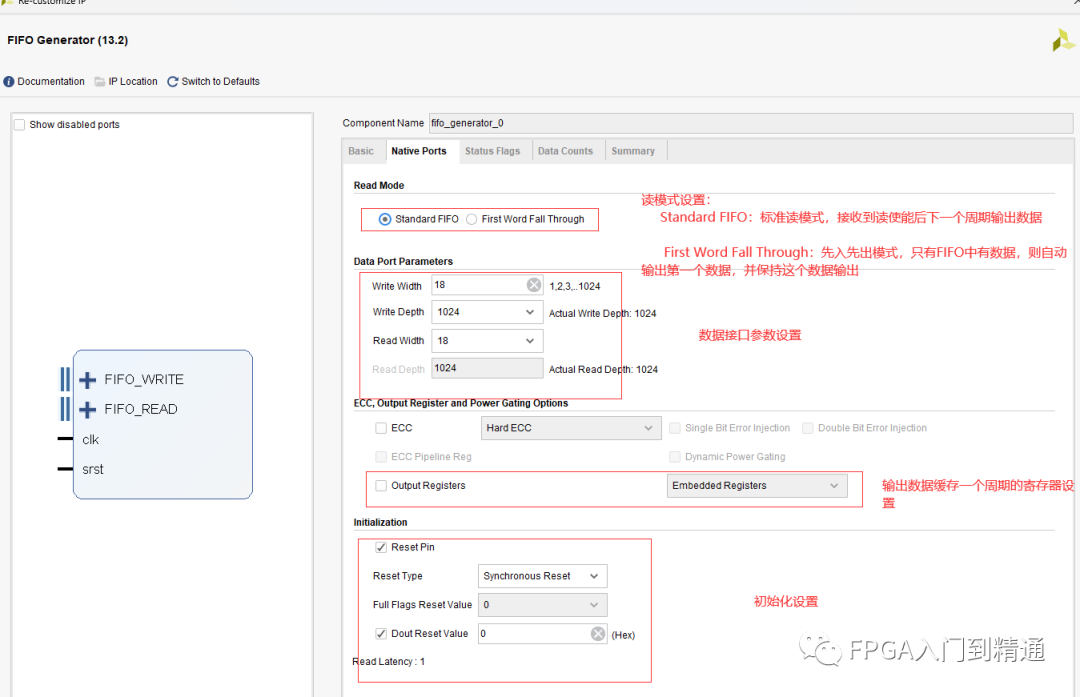

3、配置fifo接口參數

(1)讀模式設置

Standard FIFO:標誰讀模式,接收到讀使能后下一個周期輸出數據

First Word Fall Through:先入先出模式,只有FIFO中有數據,則自動輸出第一個數據,并保持這個數據輸出

(2)數據接口參數設置

FIFO讀數據接口的位寬和深度,FIFO寫數據接口的位寬和深度

(3)ECC和輸出寄存器設置

(4)初始化設置

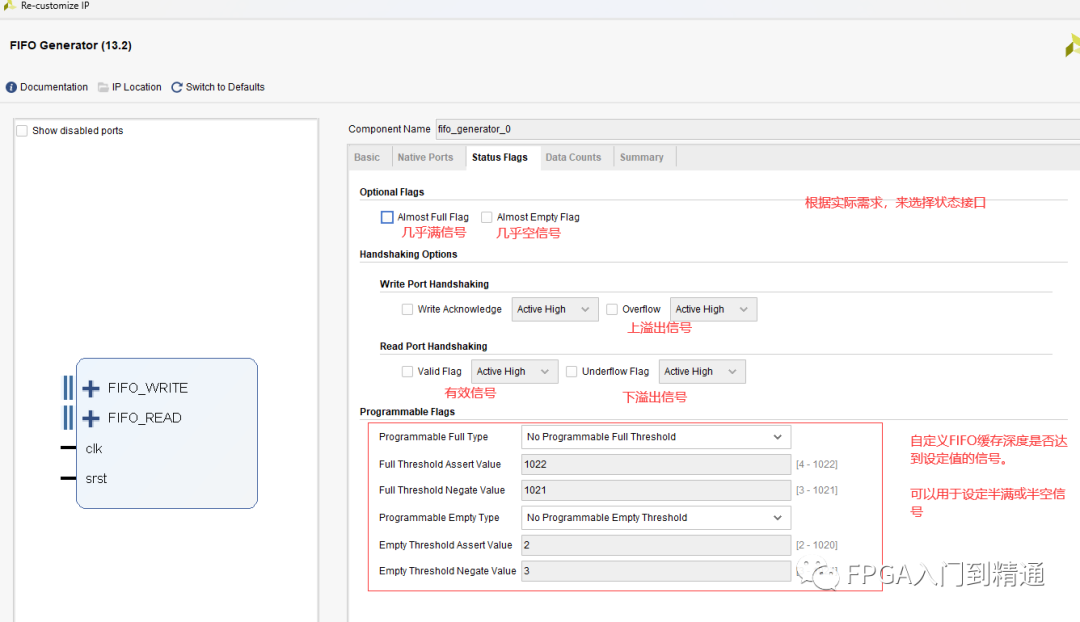

4、狀態信號接口設置

根據實際需求,選擇對應的狀態信號即可。

注意(Programmable Flags):自定義FIFO緩存深度是否達到設定值的信號,可以用于設定半滿或半空信號。

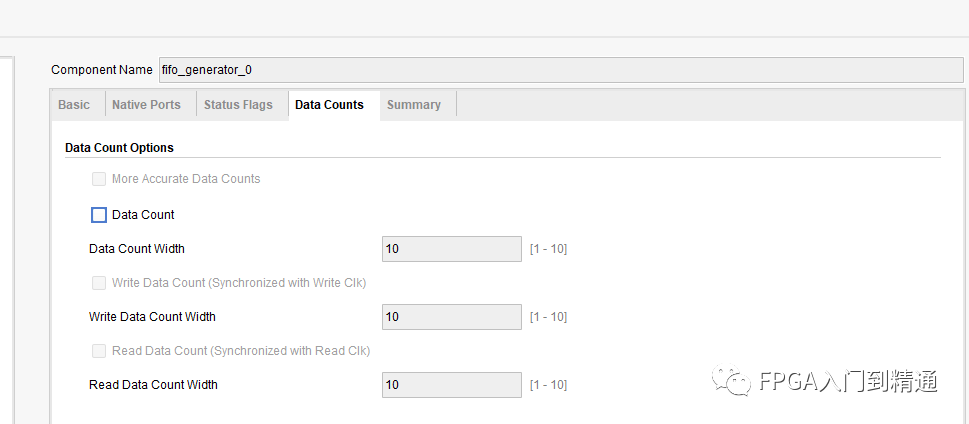

5、計數端口設置

fifo已緩存的數據深度計數,可選。

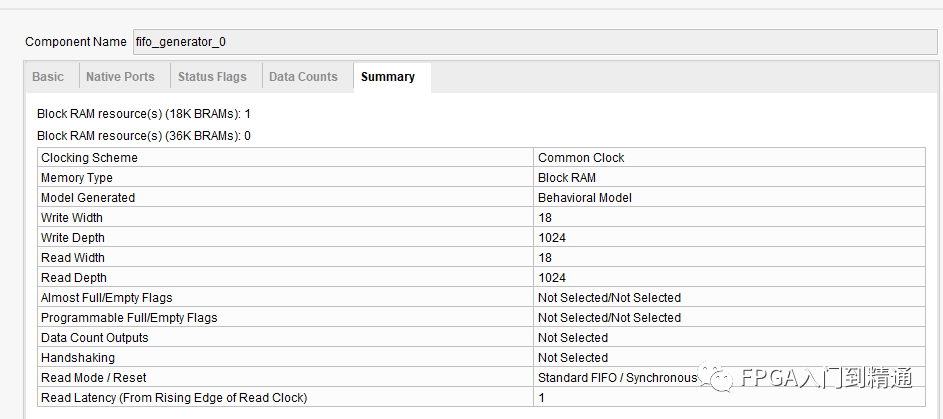

6、FIFO設置參數總覽

這是FIFO IP的設置參數總覽,可看到資源消耗、寬度、深度、讀延遲等信息。

7、點擊OK生成FIFO IP核。

二、FIFO IP核的接口

生成的FIFO IP核提供以下接口:

wr_clk 寫時鐘

rd_clk 讀時鐘

din 數據輸入端口,寬度為配置的Data Width;

wr_en 寫使能信號;

rd_en 讀使能信號;

dout 數據輸出端口;

full 滿標志,高電平表示FIFO滿;

empty 空標志,高電平表示FIFO空;

almost_full 幾乎滿標志;

almost_empty 幾乎空標志;

valid 有效數據標志

rd_data_count 讀計數

wr_data_count 寫計數

overflow 寫溢出標記

underflow 讀溢出標記

三、FIFO IP核的調用

FIFO IP核的調用很簡單,只需要對接口進行適當的連接,并根據Full和Empty標志控制讀寫使能信號。下面給出一個簡單的調用例子:

module fifo_test(

input clk,

input [17:0] din,

input wr_en, rd_en,

output valid,

output [17:0] dout,

output full, empty, overflow, underflow

);

fifo_generator_0 fifo_inst(

.clk(clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.overflow(overflow),

.valid(valid),

.underflow(underflow)

);

endmodule

在這個例子中,din和wr_en分別連接到FIFO的輸入端口,dout和empty連接到輸出端口。在寫入數據時需要檢查full信號,在讀出數據時需要檢查empty信號,以避免overflow和underflow的情況發生。

下面是FIFO IP核的一個簡單的testbench:

`timescale 1ns / 1ps

module fifo_testbench();

reg clk;

reg [17:0] din;

reg wr_en;

reg rd_en;

wire valid;

wire [17:0] dout;

wire full, empty, overflow, underflow;

fifo_test dut(

.clk(clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.overflow(overflow),

.valid(valid),

.underflow(underflow)

);

always #5 clk = ~clk;

initial begin

clk = 0;

wr_en = 0; rd_en = 0;

#10;

wr_en = 1; din = 18'd1;

#10;

wr_en = 1; din = 18'd2;

#10;

wr_en = 1; din = 18'd3;

#10;

wr_en = 0; rd_en = 1;

#10;

wr_en = 0; rd_en = 1;

#10;

wr_en = 1; din = 18'd4;

wr_en = 1; din = 18'd5;

#10;

wr_en = 0; rd_en = 1;

#10

wr_en = 0; rd_en = 1;

#10;

$finish;

end

endmodule

這個testbench通過 Applying 不同的讀寫使能信號來測試FIFO的寫入和讀取功能。

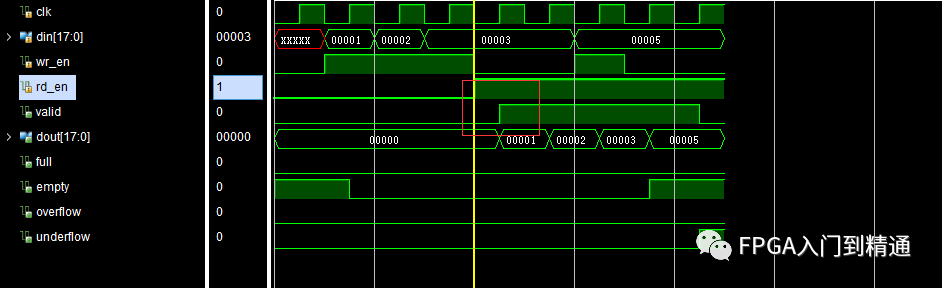

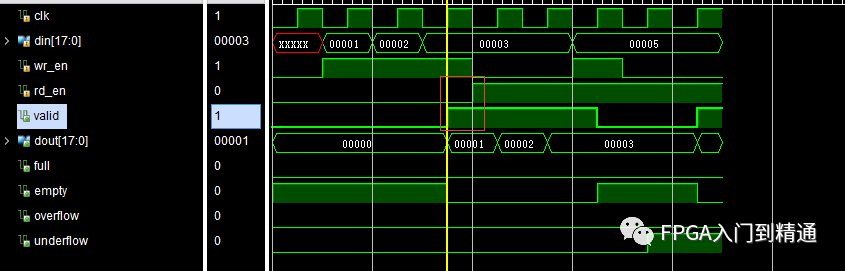

仿真測試圖:

(1)FIFO讀模式設置為“Standard FIFO”

valid信號完全由rd_en控制。

(2)FIFO讀模式設置為“First Word Fall Through”

緩存一定長度數據后,自動讀取第一個數據,并保持,直到下一個rd_en 信號到來。

四、總結

通過上面的描述,我們詳細介紹了如何在Vivado中配置FIFO IP核,FIFO的接口信號,以及如何調用FIFO IP核的一個簡單例子。FIFO是一種非常常用的IP核,通過Vivado的FIFO Generator可以大大簡化配置和使用FIFO的過程。

-

接口

+關注

關注

33文章

8961瀏覽量

153273 -

fifo

+關注

關注

3文章

400瀏覽量

44646 -

IP核

+關注

關注

4文章

338瀏覽量

50512 -

生成器

+關注

關注

7文章

322瀏覽量

21716 -

Vivado

+關注

關注

19文章

831瀏覽量

68308

發布評論請先 登錄

玩轉Zynq連載21——Vivado中IP核的移植

Vivado IP核鎖定的解決辦法分享

Xilinx Vivado的使用詳細介紹(3):使用IP核

了解Vivado中IP核的原理與應用

如何在Vivado Design Suite 中進行IP加密

FPGA實現基于Vivado的BRAM IP核的使用

講解幾點關于FIFO IP核使用時的注意事項

如何在Vivado中配置FIFO IP核

如何在Vivado中配置FIFO IP核

評論