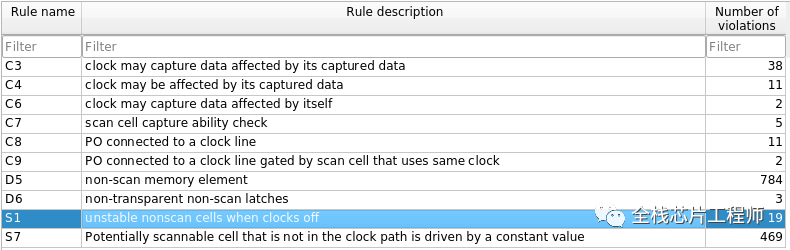

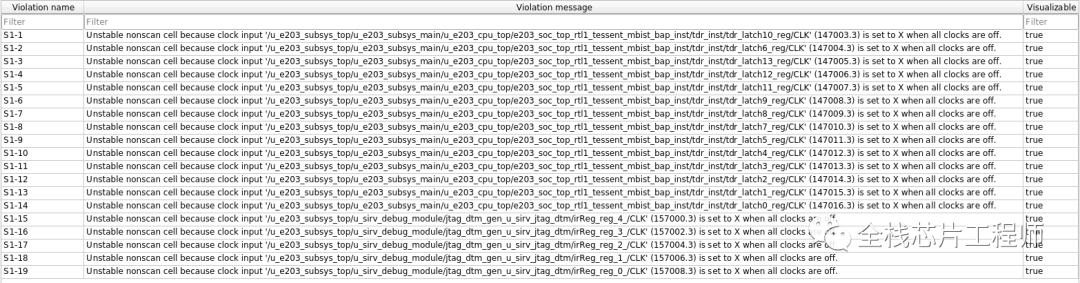

景芯SoC項目是個付費培訓(xùn)項目,項目數(shù)據(jù)在服務(wù)器上。景芯SoC在tessent完成edt occ插入并且仿真OK后,去綜合,然后做scan chain insertion就一堆error S1,首先是28個S1 violation報告出來,

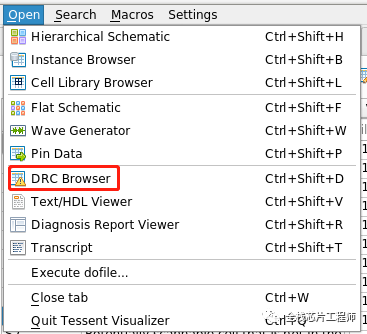

open vi 打開GUI,選Open -> DRC Browser

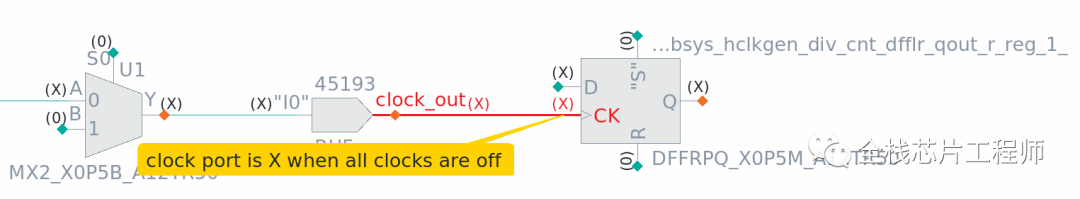

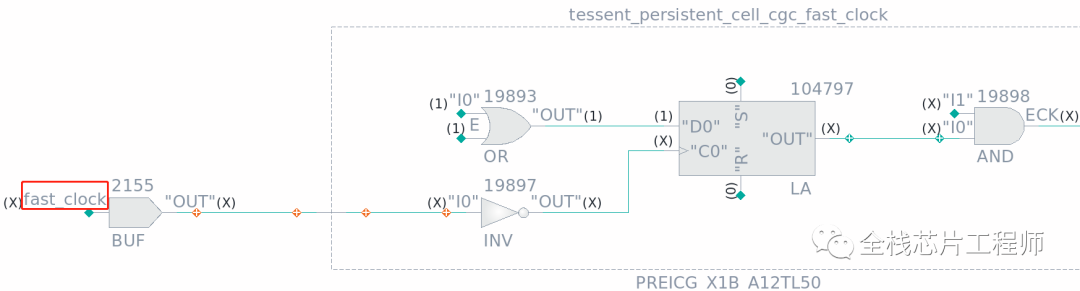

繼續(xù)往前追蹤,發(fā)現(xiàn)是PLL的高頻時鐘輸出x

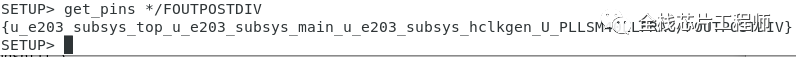

在網(wǎng)表get_pins找到PLL的輸出CLK pin:

# get_pins */FOUTPOSTDIV

add_clocks 0 u_e203_subsys_top_u_e203_subsys_main_u_e203_subsys_hclkgen_U_PLLSM40LLFRAC/FOUTPOSTDIV

然就解決了9個S1 violation,剩下19個怎么解決呢?具體參見知識星球。

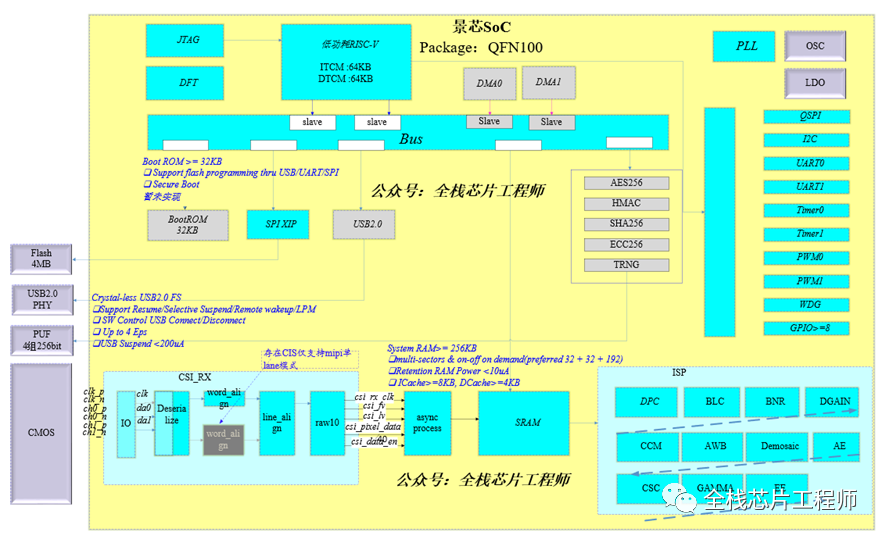

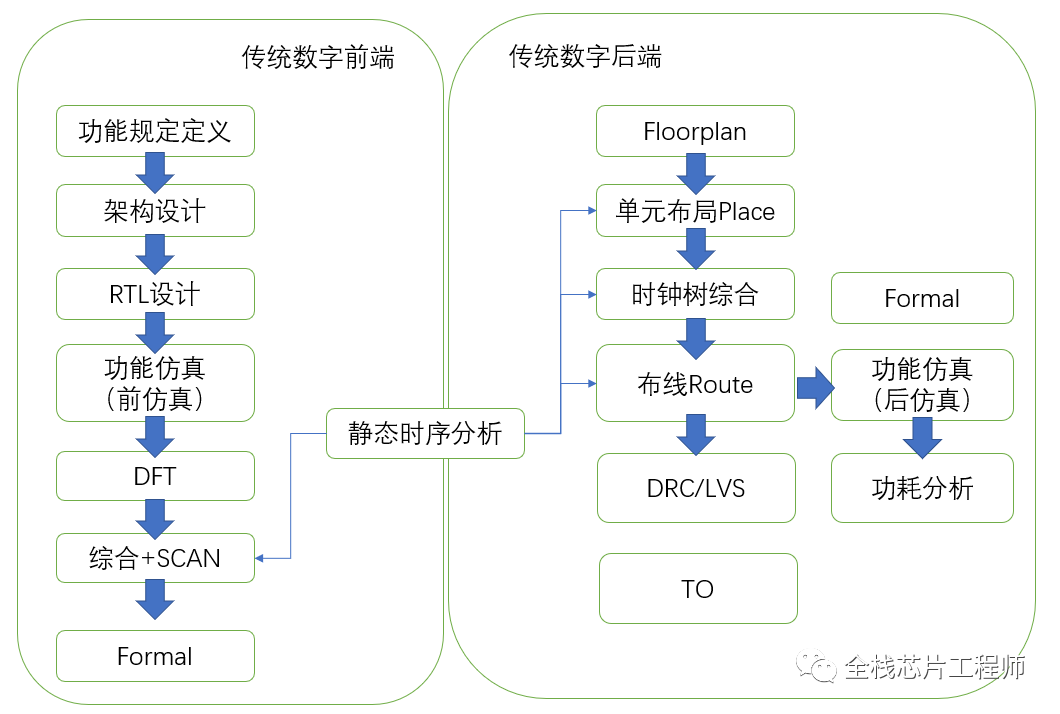

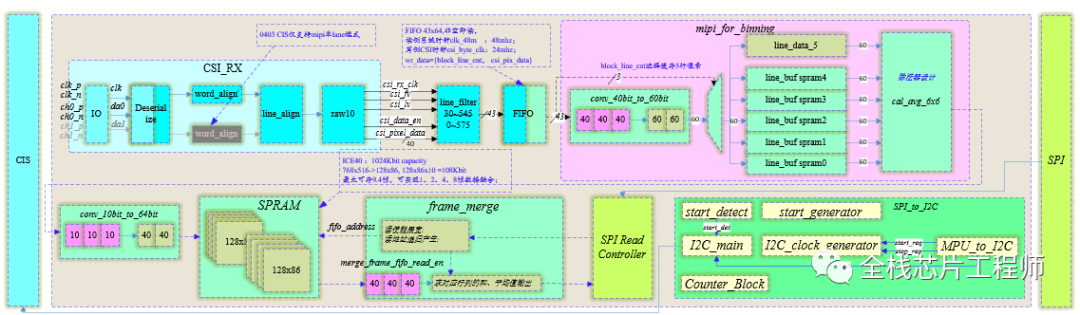

【全網(wǎng)唯一】景芯SoC是一款低功耗ISP圖像處理SoC,采用低功耗RISC-V處理器,內(nèi)置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、CNN、QSPI、UART、I2C、GPIO、百兆以太網(wǎng)等IP,采用SMIC40工藝設(shè)計流片。

培訓(xùn)數(shù)據(jù)包括SoC前端設(shè)計、DFT設(shè)計、低功耗UPF設(shè)計、布局布線,提供服務(wù)器供大家實踐!帶你從算法、前端、DFT到后端全流程參與SoC項目設(shè)計。更多內(nèi)容參見知識星球!

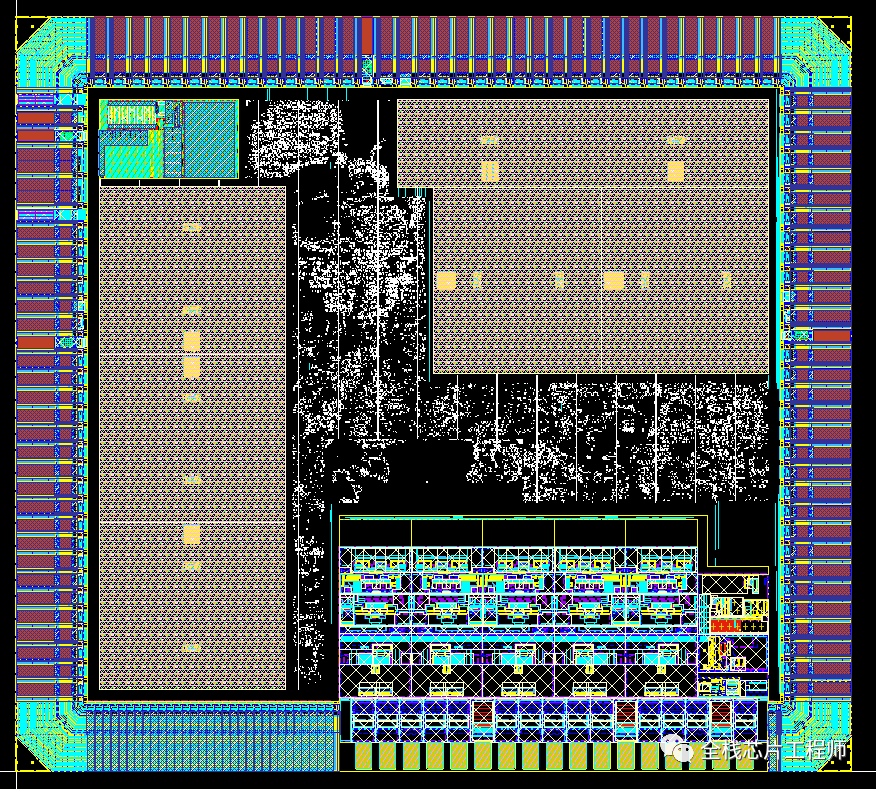

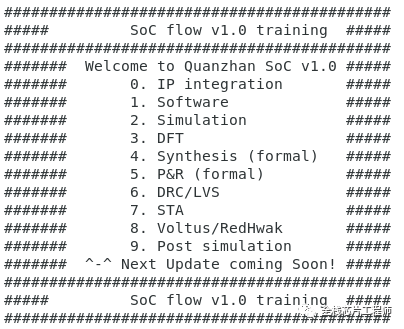

一鍵式完成C代碼編譯、仿真、綜合、DFT插入、形式驗證、布局布線、寄生參數(shù)抽取、PT分析、DRC/LVS、后仿真、形式驗證、功耗分析等全流程。V1.0工程仿真如下,部分流程仍在開發(fā)中。

SoC一鍵式執(zhí)行flow

MIPI設(shè)計

ISP圖像處理

isp_blc - 黑電平校正

isp_bnr - 拜耳降噪

isp_dgain - 數(shù)字增益

isp_demosaic - 去馬賽克

isp_wb - 白平衡增益

isp_ccm - 色彩校正矩陣

isp_csc - 色彩空間轉(zhuǎn)換 (基于整數(shù)優(yōu)化的RGB2YUV轉(zhuǎn)換公式)

isp_gamma - Gamma校正 (對亮度基于查表的Gamma校正)

isp_ee - 邊緣增強

isp_stat_ae - 自動曝光統(tǒng)計

isp_stat_awb - 自動白平衡統(tǒng)計

仿真結(jié)果:

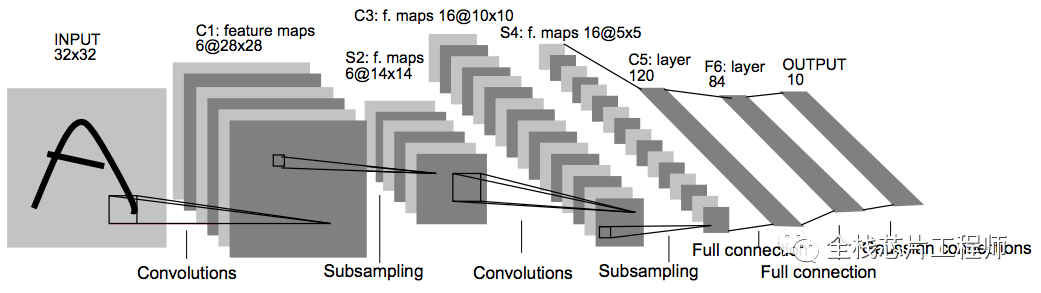

CNN圖像識別

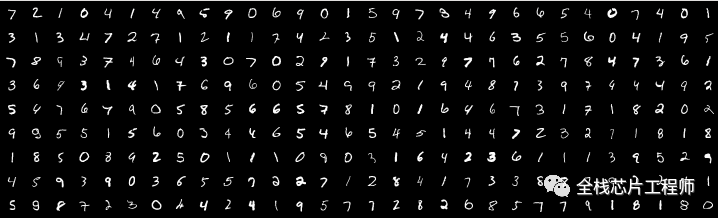

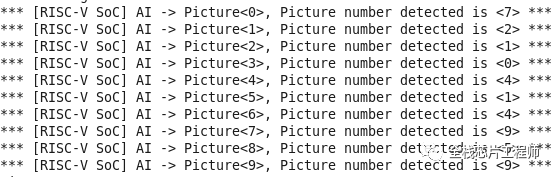

支持手寫數(shù)字的AI識別:

仿真結(jié)果:仿真識別上圖7、2、1、0、4、1、4、9

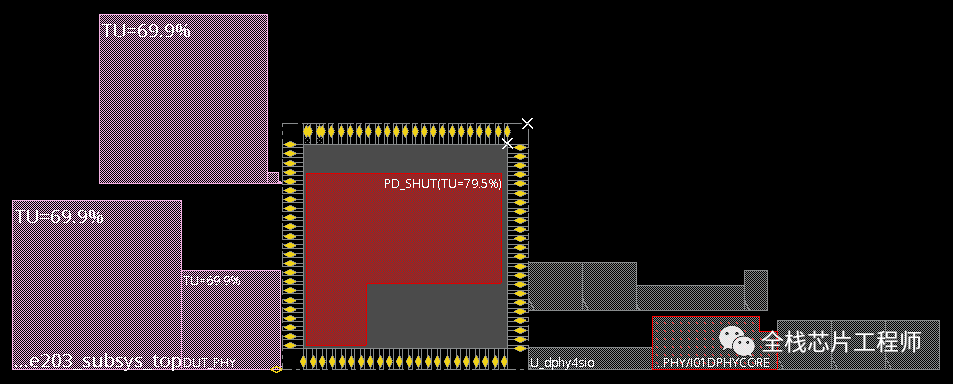

UPF低功耗設(shè)計

支持UPF低功耗設(shè)計(含DFT設(shè)計):

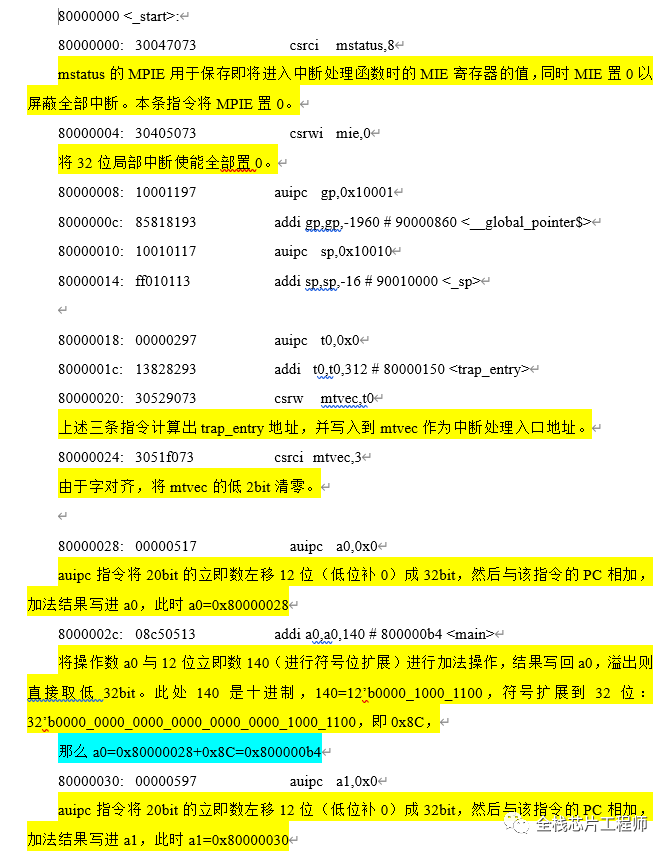

CPU啟動指令分析

審核編輯:湯梓紅

-

soc

+關(guān)注

關(guān)注

38文章

4358瀏覽量

221972 -

仿真

+關(guān)注

關(guān)注

51文章

4250瀏覽量

135437 -

服務(wù)器

+關(guān)注

關(guān)注

13文章

9728瀏覽量

87439 -

pll

+關(guān)注

關(guān)注

6文章

887瀏覽量

136161 -

DFT

+關(guān)注

關(guān)注

2文章

233瀏覽量

23281

原文標題:景芯SoC培訓(xùn)之DFT debug

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

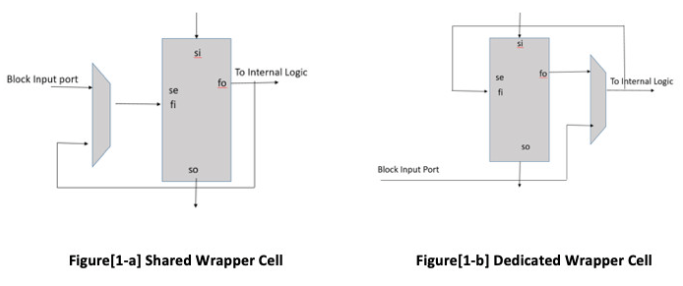

DFT和BIST在SoC設(shè)計中的應(yīng)用

急招DFT工程師(base地上海\西安)

重慶電感供應(yīng)/錳芯共模電感-谷景電子

重慶電感器廠家/錳芯共模電感器-谷景電子

什么是DFT,DFT是什么意思

分層DFT技術(shù)如何實現(xiàn)在最大化SoC

一個典型設(shè)計的DFT組件

處芯積律自研SOC項目

景芯SoC/MCU v2.0重磅升級!9.1號漲價了

SoC芯片設(shè)計中的可測試性設(shè)計(DFT)

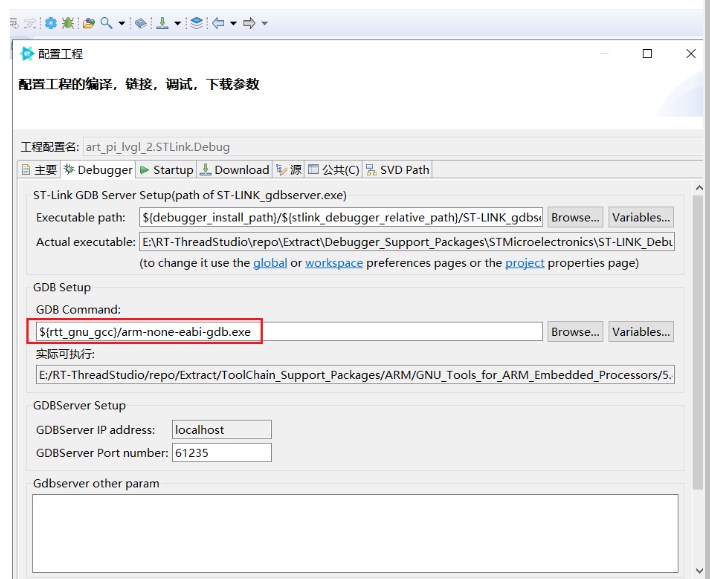

記錄一次解決RT-Thread創(chuàng)建基于ART-PI的示例項目可以下載但卻無法debug的問題

DFT如何產(chǎn)生PLL 測試pattern

一文了解SOC的DFT策略及全芯片測試的內(nèi)容

景芯SoC項目之DFT debug

景芯SoC項目之DFT debug

評論