OSC-9---晶振的Layout

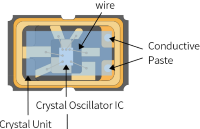

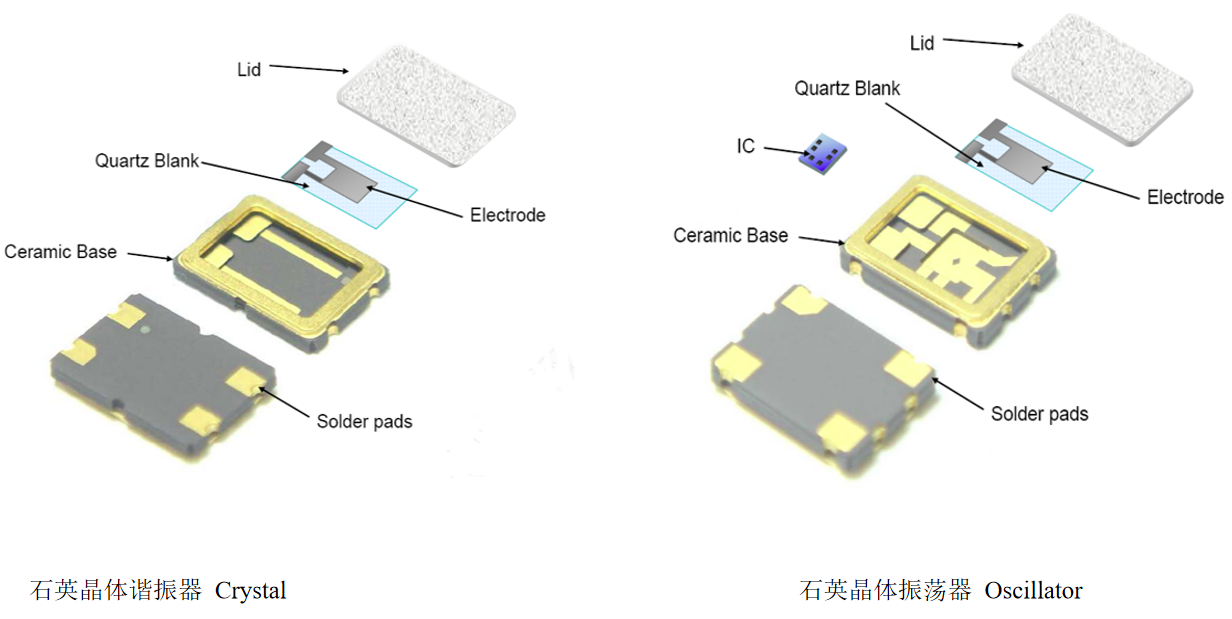

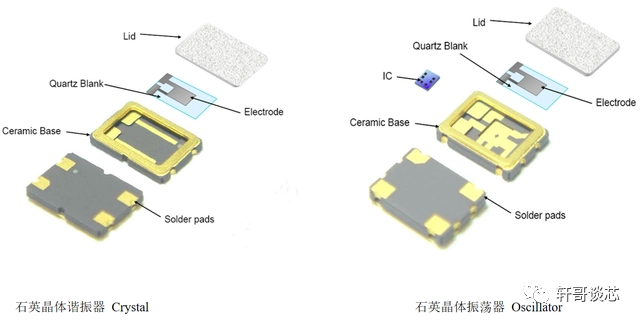

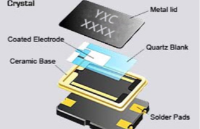

引言:晶振內部結構比較復雜,如果連接不妥當或者布線錯誤,就會影響晶振不起振或者EMC測試fail,從而導致產品不能使用。因此晶振電路的PCB設計非常重要,本節主要簡述無源/有源晶振的布局布線要點。

1.布局

1#:主體位置

晶振內部是石英晶體,如果不慎掉落或受不明撞擊,石英晶體易斷裂破損,所以晶振的放置遠離板邊,靠近MCU/SOC的位置布局。為了安全考慮,板卡的地和金屬外殼或者機械結構常常是連在一起的,如果晶振布在板卡的邊緣,晶振與參考接地板會形成電場分布,而板卡的邊緣常常是有很多線纜,當線纜穿過晶振和參考接地板的電場,線纜會被干擾。而晶振布在離邊緣遠的地方,晶振與參考接地板的電場分布被PCB板的GND分割,分布到參考接地板電場大大減小了。

2#:電容位置

有源晶振的去耦電容應盡量靠近晶振的電源管腳,如果多個耦合電容,按照電源流入方向,依次容值從大到小擺放。無源晶振的負載電容靠近晶振本體,減少寄生電容的影響。

3#:獨立性

盡可能保證晶振周圍的沒有其他元件,建議這個距離為300mil,約為7.6mm,實際4-5mm左右也可以接受,防止器件之間的互相干擾,影響時鐘和其他信號的質量,

2.布線

1#:走線短

在電路系統中,高速時鐘信號線優先級最高,一般在布線時,需要優先考慮系統的主時鐘信號線。時鐘線是敏感信號,頻率越高,要求走線盡量短,保證信號的失真度最小,與其它信號需20mil間距,最好使用Ground trace與其他信號隔離,避免時鐘線干擾其他信號。

2#:外殼接地

晶振的外殼必須要接地,除了防止晶振向外輻射,也可以屏蔽外來的干擾。

3#:晶振底下鋪地

晶振鋪地可以防止干擾其他層,不滿足鋪地也需要粗走線包裹。

4#:晶振底下不要布線

晶振周圍5mm的范圍內不要布線和其他元器件,主要是防止晶振干擾其他布線和器件。底下盡量不要走線,一定要走線的話,不能走線進晶振pin腳周圍50mil之內,尤其避免高速信號。

5#:有源晶振輸出不能接長線

時鐘源通常是系統中最嚴重的EMI輻射源,頻率高,是高速電路,時鐘上升沿陡高速頻譜含量越多,如果接長線,其結果是長線就成了天線,這在很多應用中是不允許的,所有時鐘源都必須盡量靠近相關器件,必要時用多個時鐘源,不得以下可以采用多層PCB將時鐘連線屏蔽。有源晶振的輸出一般是標準TTL規格,至于能驅動多少芯片要看這些芯片的特性。關于晶振的選擇,如果你的系統能工作在25M,就盡量不要選50M的晶振。

6#:過孔

晶振信號線盡可能不穿孔,因為一個過孔會有大約0.5pF的寄生電容,走線粗細要一致。

3.保護器件

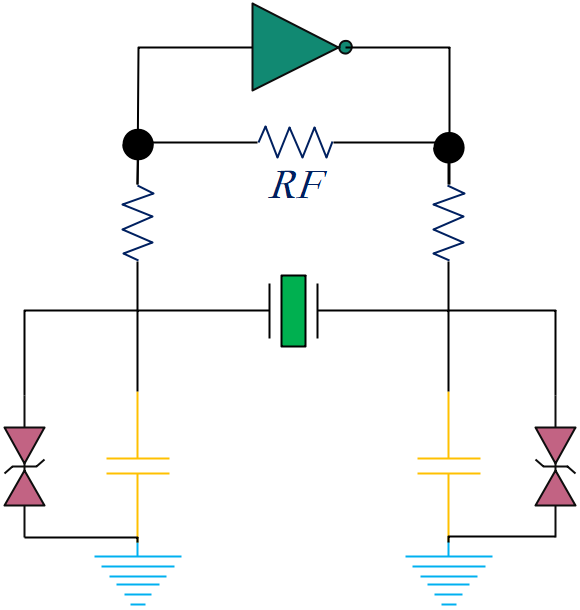

圖9-1:晶振增加ESD保護器件

當使用ESD保護器件時,需要器件的寄生電容考慮在內合并計算CL,以最大限度地降低更高頻帶信號的衰減和頻率偏移。

4.無源晶振Layout示例

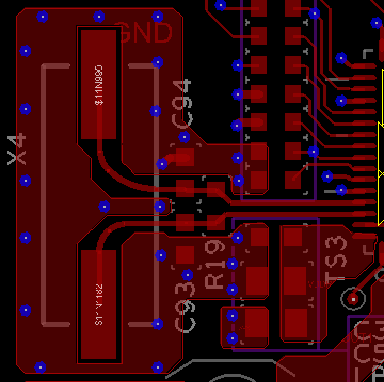

頂層:圖9-2所示,晶振頂層的最好策略是鋪銅包地(如果有的話也可以連接其他大面積GND銅皮,也可以獨立GND銅皮),效果比走線包地效果更佳。鋪銅之后,打上過孔陣列,與其它層的銅皮進行良好連接,形成一個密集的GND三維多層法拉第籠。

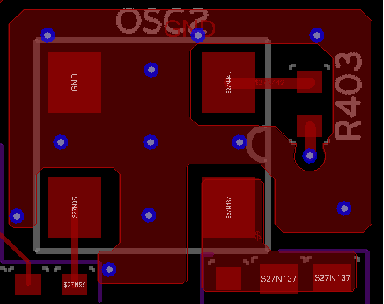

圖9-2:無源晶振頂層走線范例

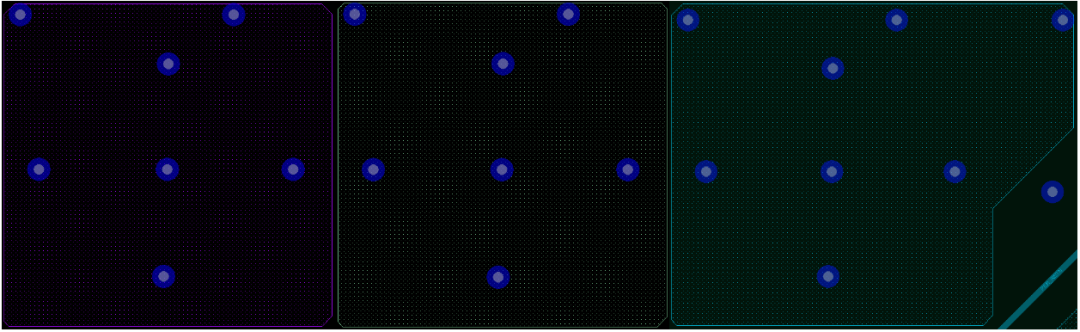

中間層和底層:因為晶振底下的投射區域不能走線,不包括GND層和POWER層(GND層完整覆蓋,POWER層也完整覆蓋,不用挖空),所以就將投射區域的GND過孔用銅皮連接成shape,其他層也類似如圖9-3處理。

圖9-3:無源晶振中間層/底層范例

5.有源晶振Layout示例

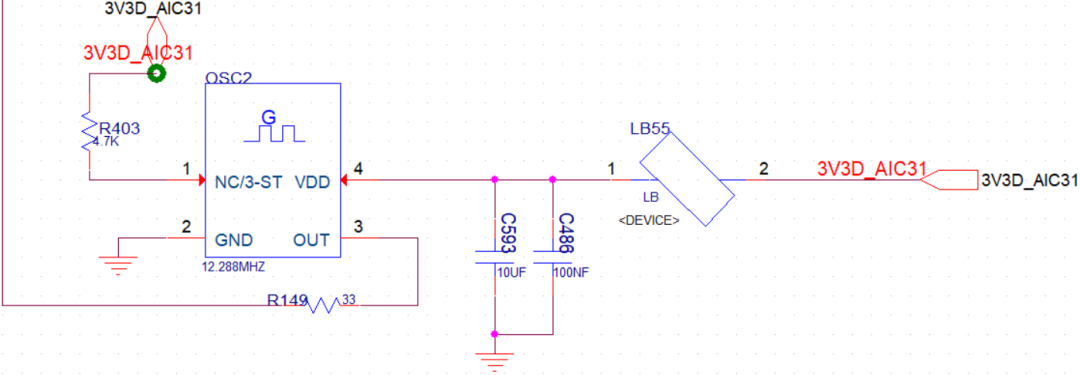

圖9-4:有源晶振電路

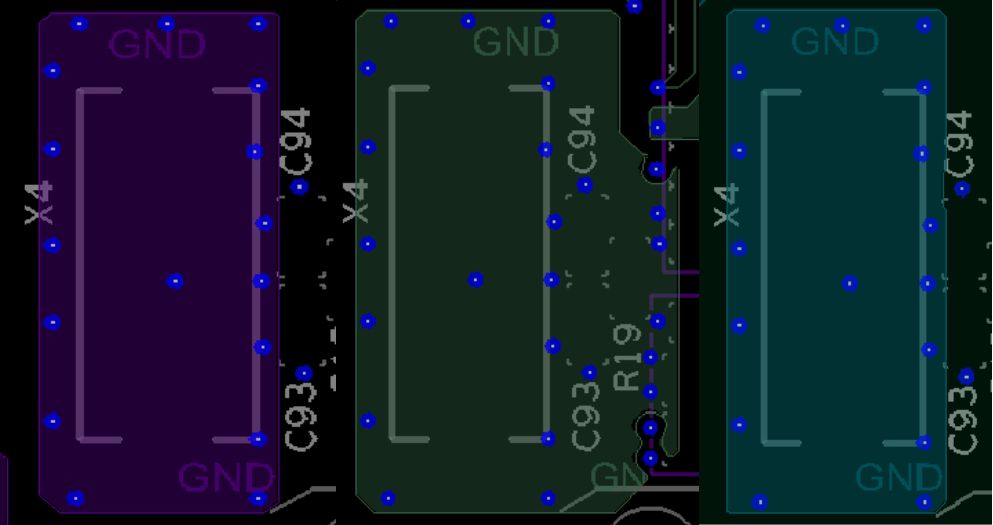

頂層:如圖9-5,去耦電容靠近晶振的電源管腳,有源晶振同樣建議使用銅皮GND包裹策略,時鐘信號直連,盡量不要過孔換層。

圖9-5:有源晶振頂層走線范例

中間層和底層:GND銅皮覆蓋投射區域,過孔立體連通。

圖9-6:有源晶振中間層/底層范例

-

有源晶振

+關注

關注

1文章

926瀏覽量

21185 -

無源晶振

+關注

關注

1文章

853瀏覽量

16661 -

晶振

+關注

關注

35文章

3202瀏覽量

69587 -

布局布線

+關注

關注

1文章

89瀏覽量

15332 -

PCB

+關注

關注

1文章

2021瀏覽量

13204

發布評論請先 登錄

簡述無源/有源晶振的布局布線要點

簡述無源/有源晶振的布局布線要點

評論