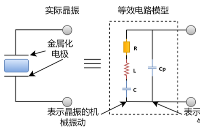

時鐘(Clock)在一般SoC電路上是必不可少的,精準的時鐘通常由晶振提供,晶振很難集成到芯片中去,而是作為分立元件設計在PCB上。它就像是人的心臟,晶科鑫人的使命便是為電子硬件裝上一顆安心的心臟,如果時鐘出錯了,整個電路或者通信就會發生問題。

比如,16MHz晶振給一個2.4G藍牙芯片提供參考時鐘,如果16MHz的晶振出現頻偏,比如偏-48ppm(頻率為15.999223MHz),由于射頻是參考時鐘倍頻上去的,也會出現-48ppm的頻偏(藍牙頻點變成2,399,883,450Hz,約100KHz的頻偏),造成藍牙與標準頻率的對端無法通信。因此一個好的時鐘電路,一顆高精度的晶振是非常必要的,晶科鑫30余年來一直為廣大客戶提供高品質高精度晶振,并會幫助客戶上板調試晶振電路使時鐘至最佳最精準狀態,力求幫助客戶的方案得到最好的穩定性。此篇文章對時鐘電路中的晶振電路layout簡單做一下闡述。

對于晶振電路,我們需要從幾個方面考慮設計:

1、降低寄生電容的不確定性

2、降低溫度的不確定性

3、減少對其他電路的干擾

設計注意點:

1. 晶振盡量靠近芯片,保證線路盡量短,防止線路過長導致串擾以及寄生電容。

2. 晶振周圍打地孔做包地處理。

3. 晶振底部不要走信號線,尤其是其他高頻時鐘線。

4. 負載電容的回流地要短。

5. 走線時先經過電容再進入晶振。

6. 封裝較大,可從晶振中間出線。

7. 如果有測試點,使stub盡量短。

8. 走線可以走成假差分形式。盡量走在同一層。

9. 部分晶振底下需要做掏空處理,以防電容效應以及熱效應造成頻偏。

10. 如果是鐵殼晶振,外殼做接地處理,提高抗干擾能力。

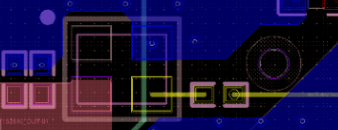

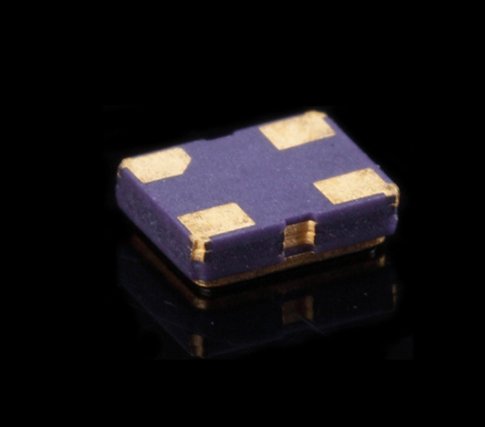

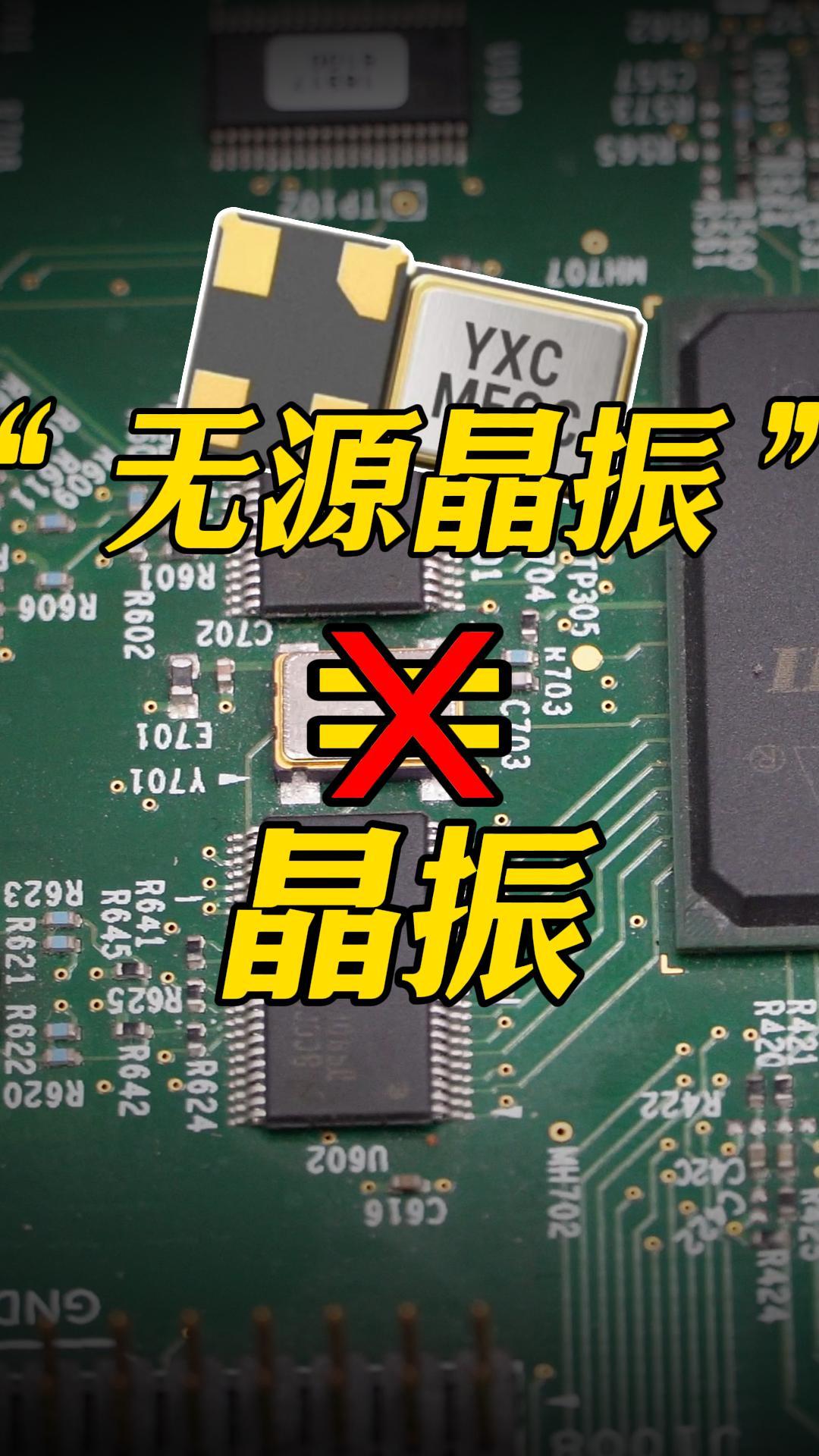

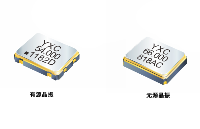

下面分別舉例貼片無源晶振及有源晶振的走線方式:

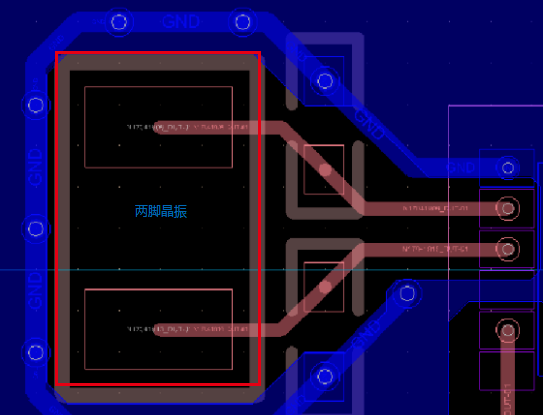

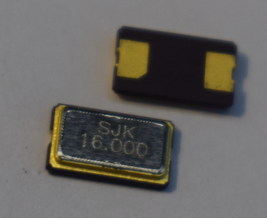

兩腳貼片無源晶振

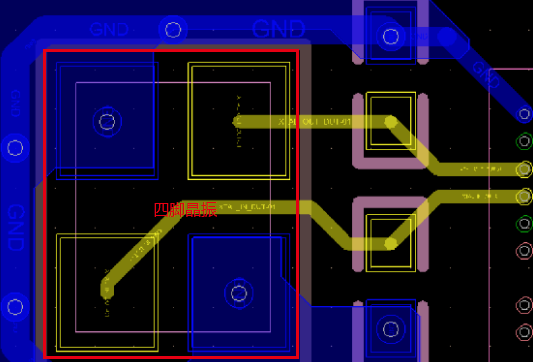

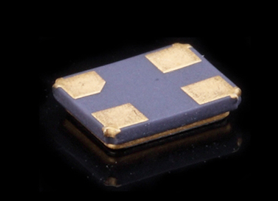

四腳貼片無源晶振

HTOL測試板上有源晶振的布局:

由于老化測試中一般芯片都在socket中測試,所以晶振不能與Socket放置在同一面,否則晶振會距離芯片較遠。

晶振放在反面則需要打孔后連接至芯片管腳,此時需要在打孔附近增加回流地孔。

有源晶振需額外注意電源濾波電路處的電容,從大到小依次靠近晶振放置。

貼片有源晶振

-

pcb

+關注

關注

4356文章

23438瀏覽量

407147 -

有源晶振

+關注

關注

1文章

926瀏覽量

21201 -

晶振

+關注

關注

35文章

3216瀏覽量

69649 -

晶振電路

+關注

關注

7文章

96瀏覽量

25743

發布評論請先 登錄

PCB板上晶振電路的設計

PCB板上晶振電路的設計

評論