作品概述

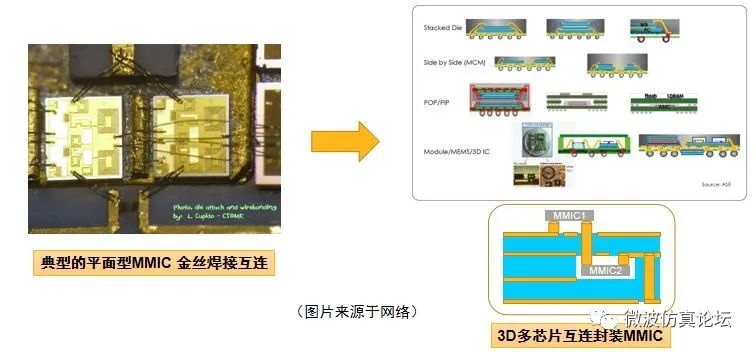

相對于傳統平面型的金絲鍵合焊接的MMIC應用,三維(3D)多芯片互連封裝MMIC以其高集成度、低損耗、高可靠性等性能優勢,正逐步在先進電路與系統中得到應用。而3D封裝引入的復雜電磁耦合效應,在傳統MMIC仿真設計上并未包含。本設計基于HFSS,充分考慮實際封裝寄生效應,建立了完整的3D多芯片互連精準模型,并給出了封裝前后仿真結果對比分析。

仿真應用背景

平面型互連向3D集成互連發展

仿真結果分析、展示

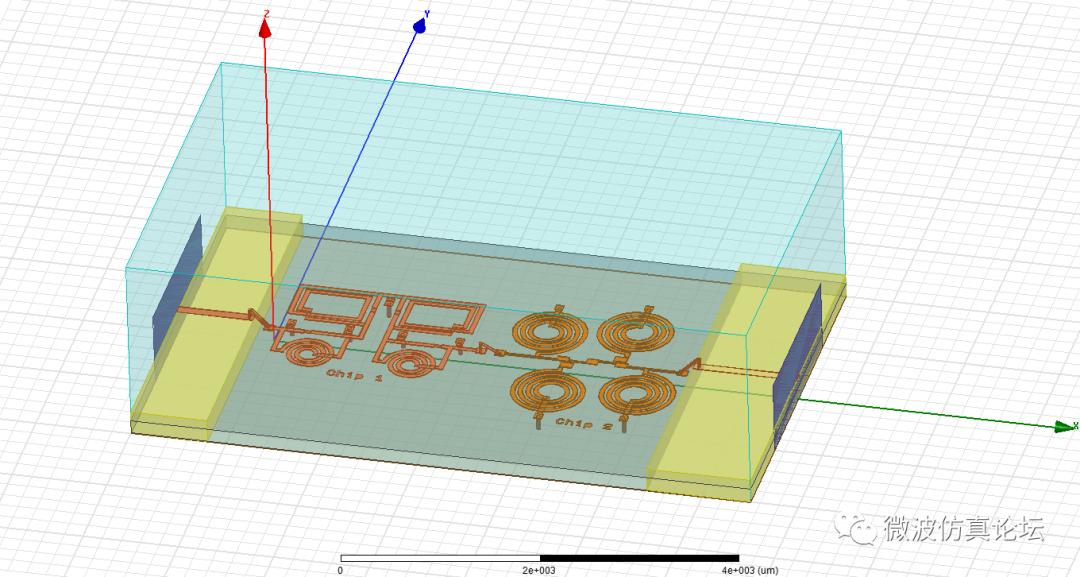

本設計用兩個MMIC 互連展示

考慮兩種連接情形分別建模與仿真

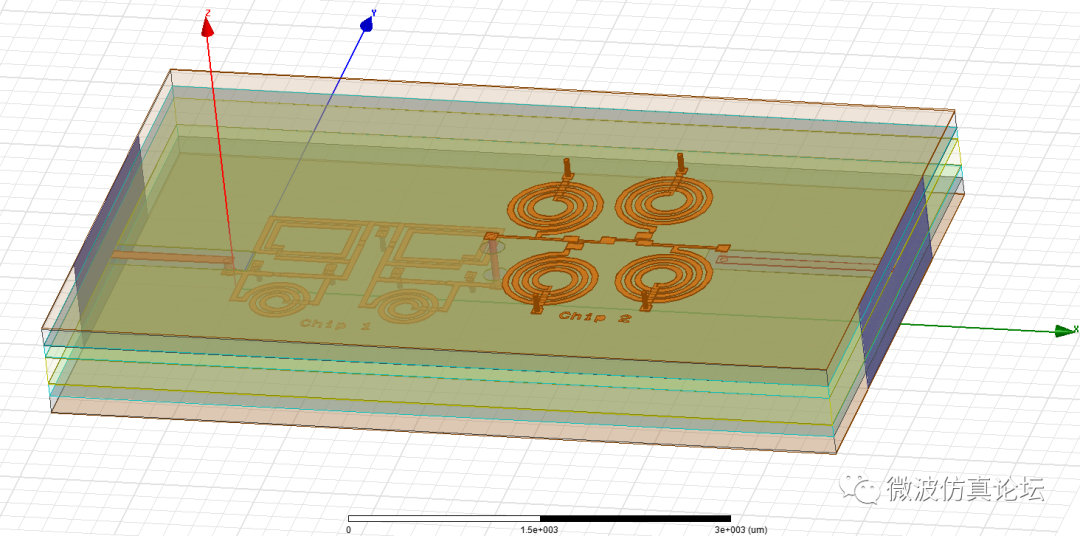

Case1:平面型金絲鍵合仿真模型

Chip1和Chip2為兩個濾波器芯片;

Chip1和Chip2通過金絲鍵合;

輸入和輸出微帶線采用陶瓷基板。

平面型金絲互連仿真模型

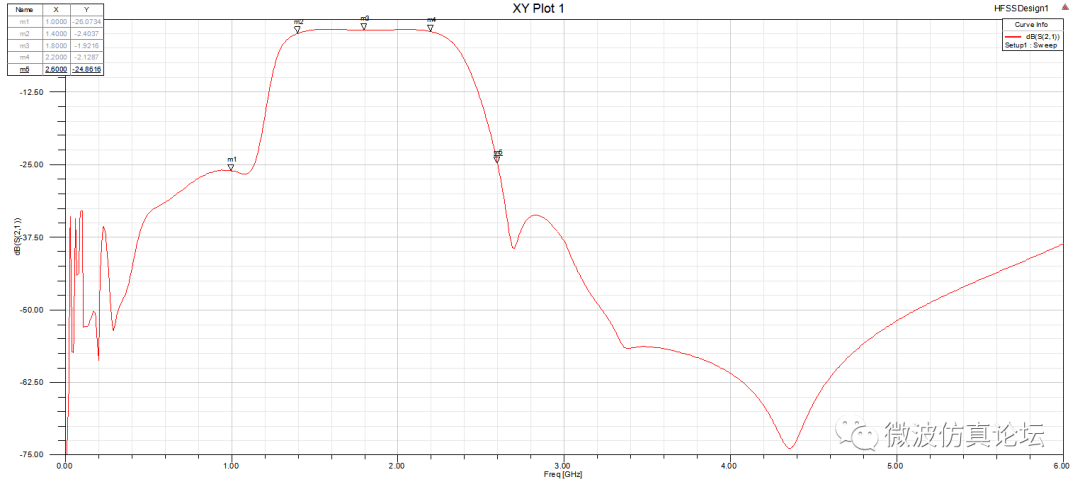

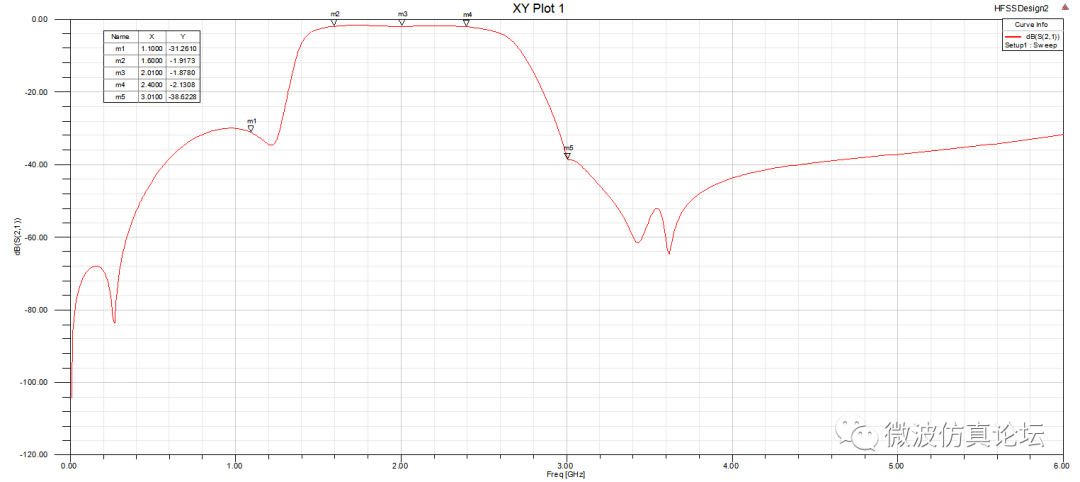

平面型金絲互連仿真結果

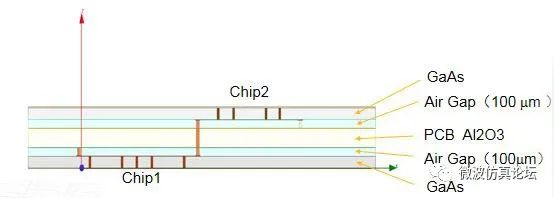

Case2:3D集成互連仿真模型

Chip1和Chip2,與Case1相同的兩個濾波器芯片;

Chip1和Chip2通過通孔、銅柱或金球實現信號互連;

采用同樣的陶瓷基板作為芯片的載體。

此處的空氣腔高度設為100 μm。

截面圖

3D集成互連仿真模型

3D集成互連仿真結果

通帶變為:1.6GHz~2.4GHz

原設計通帶(Case1):1.4GHz~2.2GHz

頻段偏移約10%。

小結

1,相較于平面型金絲互連,兩個MMIC芯片3D集成互連之后,發生一定頻偏,頻帶向高偏移約10%。

2,引起頻偏可能的原因:

1) 3D集成的互連結構(通孔、銅柱、金球等)的寄生效應引起頻偏,但相較于芯片中元器件如電感電容而言,該寄生參數相對較小,與金絲的寄生參數量級相當,故影響作用微小。

2) 3D集成引入了較小的空氣腔,本設計空氣腔高度為100μm(工程實踐中會比這高度更低),帶來了新的寄生效應,經分析,當空氣腔高度為芯片基板3倍左右時,頻偏現象可忽略。

3,通過本設計可以看出,應用于3D集成封裝的芯片電路,若單純采用傳統平面型MMIC設計,3D封裝后會造成一定的性能偏差。因此,需有針對性的做完整的3D集成封裝MMIC優化設計,確保3D封裝后滿足電路指標要求。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52192瀏覽量

436253 -

封裝

+關注

關注

128文章

8509瀏覽量

144799 -

仿真設計

+關注

關注

3文章

97瀏覽量

17048 -

MMIC

+關注

關注

3文章

733瀏覽量

25084

原文標題:【案例分享】基于HFSS的3D多芯片互連封裝MMIC仿真設計

文章出處:【微信號:微波仿真論壇,微信公眾號:微波仿真論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

HFSS高頻電磁場仿真應用

芯片的3D化歷程

3D封裝技術及其發展

英特爾邏輯芯片3D堆疊技術“Foveros” 將實現世界一流性能

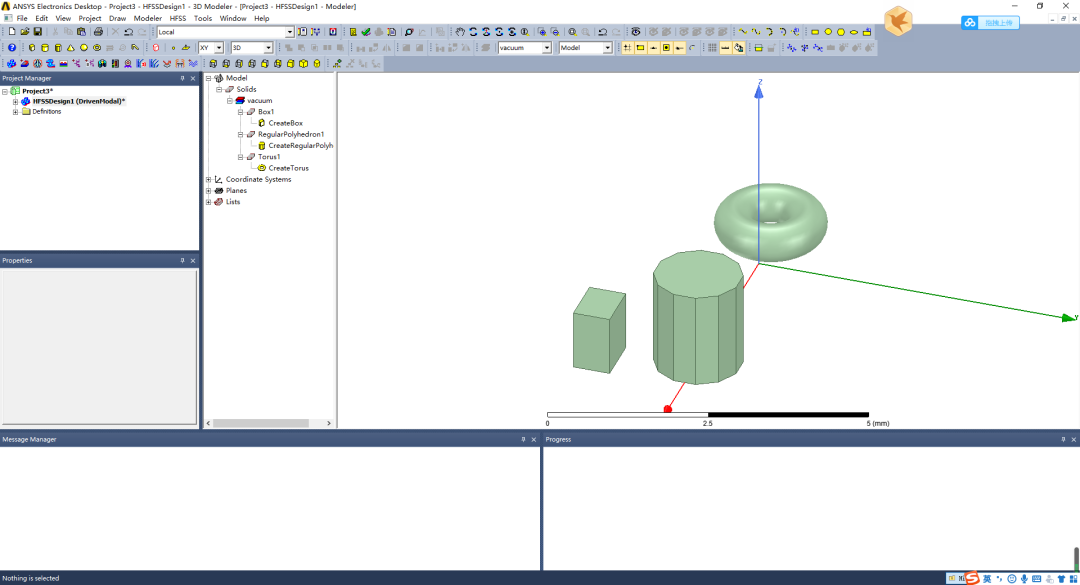

利用HFSS軟件進行3D可視化建模

2.5D/3D芯片-封裝-系統協同仿真技術研究

分享一下小芯片集成的2.5D/3D IC封裝技術

3D封裝結構與2.5D封裝有何不同?3D IC封裝主流產品介紹

基于HFSS的3D多芯片互連封裝MMIC仿真設計

基于HFSS的3D多芯片互連封裝MMIC仿真設計

評論