概要

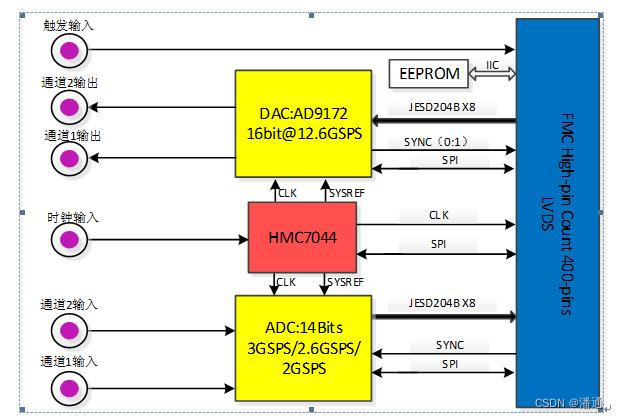

QT7331是一款高分辨率、高采樣率的ADC+DAC FMC子板。它同時支持2路14位3.0/2.6/2.0GS/s的A/D通道輸入和2路16位12.6GS/s的D/A通道輸出,全功率模擬-3dB輸入帶寬可達9GHz。QT7331A為3GSPS采樣率,QT7331B為2.6GSPS采樣率,QT7331C為2GSPS采樣率。本板卡支持觸發(fā)輸入或者輸出;內(nèi)參考、外參考、外時鐘三種時鐘方式,可通過SPI總線實現(xiàn)時鐘源選擇。通過參考時鐘可實現(xiàn)多個板卡的同步。

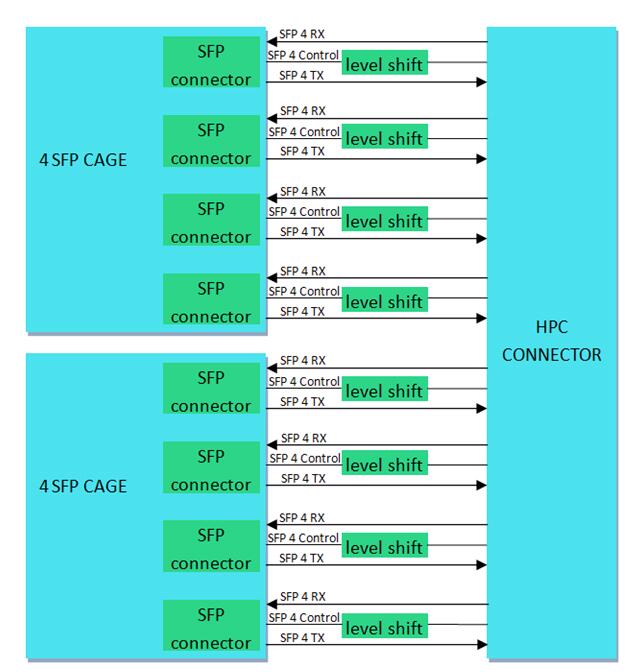

QT7331板卡的電氣與機械設(shè)計依據(jù)FMC標準(ANSI/VITA 57.1),通過一個高密度連接器(HPC)連接至FPGA載板。前面板I/O裝配6個SSMC同軸連接器。QT7331設(shè)計了風冷和導冷版本,可適應(yīng)于多種FPGA載板,如 Xilinx和Altera等通用載板,以進行高性能的算法計算。

整體架構(gòu)流程

更多信息請加weixin-pt890111獲取

技術(shù)指標

? 6個SSMC的連接器,其中2個分別為模擬信號輸入1(AD0)和模擬信號輸入2(AD1);2個分別為模擬信號輸出1(DA0)和模擬信號輸出2(DA1);一個為外部時鐘輸入(CLK);一個為觸發(fā)輸入或者輸出(TRG)

? 采樣頻率:2通道16bits 12.6GS/s DA和

QT7331A:2通道 14bit 3GS/s AD;

QT7331B:2通道 14bit 2.6GS/s AD;

QT7331C:2通道 14bit 2GS/s AD;

? 輸入帶寬:全功率模擬輸入帶寬(-3 dB):9GHz

? ADC輸出和DAC輸入均為JESD204B標準數(shù)字接口

? 適應(yīng)范圍:完全符合Vita57.1規(guī)范,包括結(jié)構(gòu)件,子卡尺寸,面板連接器,正反面器件的限高等,大大提供了子卡的通用性和適配性

? 多種散熱方式:風冷或?qū)Ю?br />

? 模擬輸入和輸出均為AC耦合

? 板載溫度監(jiān)控電路

? 時鐘選擇靈活:內(nèi)部時鐘、外部時鐘選擇可由載板控制

? HPC高引腳數(shù)連接器

? 工作溫度:商業(yè)級0℃~ +70℃ ,工業(yè)級 -40℃~ +85℃

其他支持

提供Verilog bit文件

JESD204B Core,可包括BSP

性能與指標

模擬輸入:

(1)輸入耦合方式:交流耦合;

(2)ADC芯片數(shù)量:1片;

(3)全功率帶寬 (-3 dB):9.0GHz;

(4)滿量程輸入電壓:

QT7331A、1.13Vpp ~2.04Vpp,典型值1.7Vpp ;

QT7331B/C、1.1Vpp ~2.0Vpp,典型值1.7Vpp ;

(5)輸入阻抗:50 Ohm;

(6)連接器: SSMC;

模擬輸出:

(1)輸出耦合方式:交流耦合;

(2)DAC芯片數(shù)量:1片;

(3)全功率輸出帶寬:6GHz ;

(4)滿量程輸出電流:16~26mA可調(diào);

(5)輸出阻抗:50 Ohm;

(6)連接器: SSMC ;

時鐘:

(1) 支持內(nèi)參考或外部參考:

10MHz,功率-5~10dBm

(2) 支持外部采樣時鐘最高:

3 GHz; 功率-5~10dBm

(3) 輸入阻抗:50 Ohm;

(4) 耦合方式:交流耦合;

(5) 連接器: SSMC ;

觸發(fā):

(1)觸發(fā)輸入:3.3V CMOS/TTL;

(2)觸發(fā)輸出:3.3V CMOS/TTL;

(3)最大頻率:200MHz;

(4)連接器: SSMC ;

審核編輯 黃宇

-

連接器

+關(guān)注

關(guān)注

99文章

15315瀏覽量

139904 -

FMC

+關(guān)注

關(guān)注

0文章

99瀏覽量

20060

發(fā)布評論請先 登錄

EEPROM芯片內(nèi)部的1路14bit ADC, ADC精度受使用通道數(shù)和采樣率是怎么樣的?

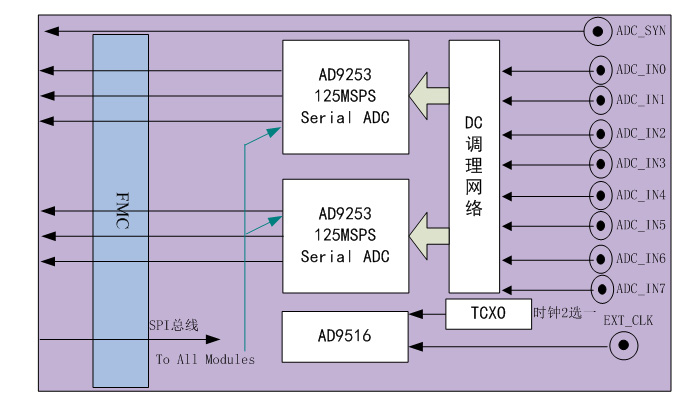

FMC子卡設(shè)計原理圖:FMC209-基于FMC的4路125MAD輸入、2路1GDA輸出子卡 中低頻信號采集

FMC子卡設(shè)計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數(shù)據(jù)處理核心板

ADS62P49輸出是7bit怎么變?yōu)?b class='flag-5'>14bit呢?

FMC子卡設(shè)計原理圖:FMC181-八路125Msps 14bit 直流耦合脈沖采集AD FMC子卡

子卡設(shè)計原理圖:232-基于FMC的2收2發(fā)TLK2711子卡

一個DAC的最高采樣率是125MSPS,該DAC是14bit的,那么如果輸出2Mhz的正弦波信號,每個周期10個點,可以實現(xiàn)嗎?

AIC3256采用I2S模式時,6通道音頻采集的傳輸時序?qū)⑹窃趺礃拥哪兀?/a>

FMC子卡原理圖設(shè)計:四通道1.25G/14bit數(shù)據(jù)采集

FMC子卡原理圖設(shè)計: 4路 16bit 250M ADC+4路 16bit 2.8G DAC

ADS8578S 14位、高速8通道同步采樣ADC數(shù)據(jù)表

高速AD9172 AD9689 2通道 14bit 2GS/s FMC子卡

高速AD9172 AD9689 2通道 14bit 2GS/s FMC子卡

評論