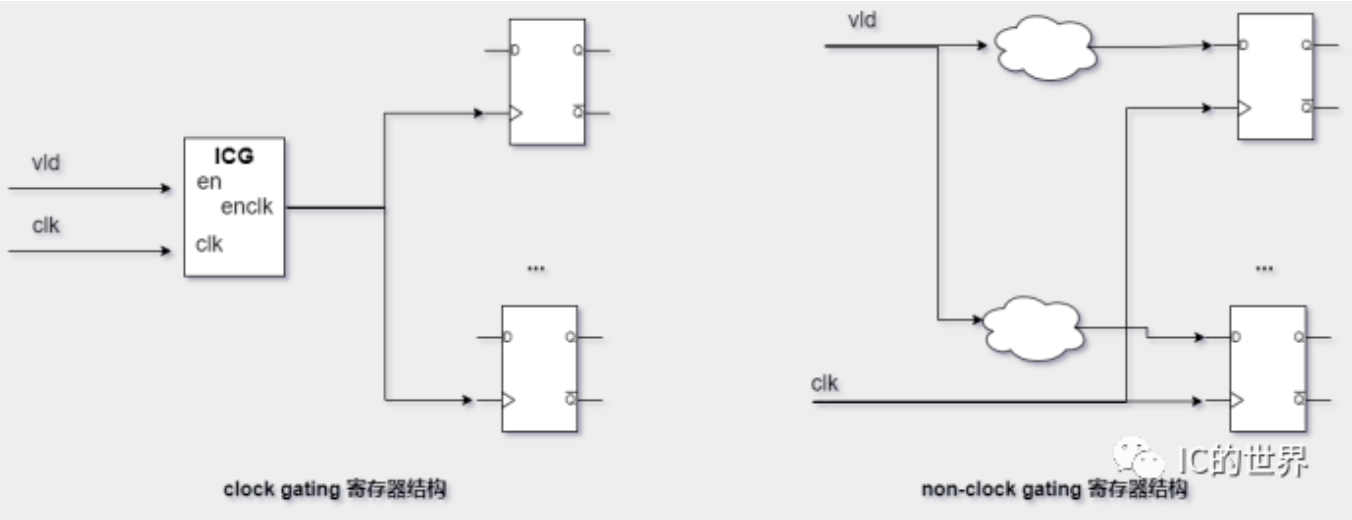

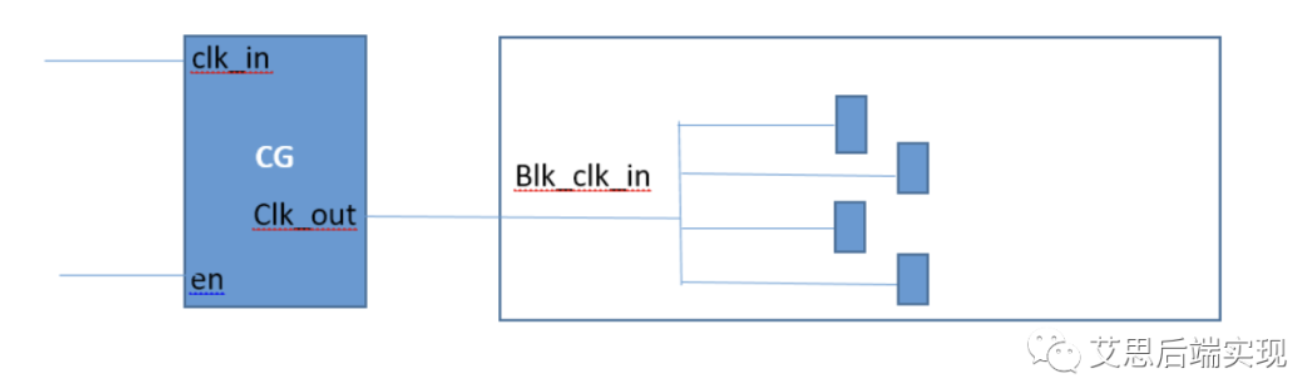

ICG(integrated latch clock gate)就是一個(gè)gating時(shí)鐘的模塊,通過使能信號(hào)能夠關(guān)閉時(shí)鐘。常用場(chǎng)景:低功耗狀態(tài)下,關(guān)閉部分時(shí)鐘源;無毛刺時(shí)鐘動(dòng)態(tài)切換等。

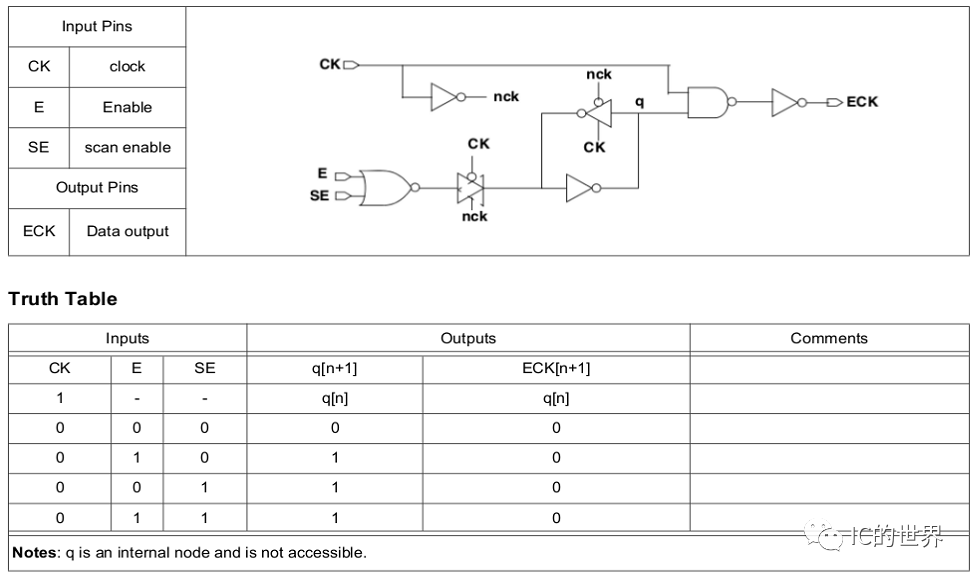

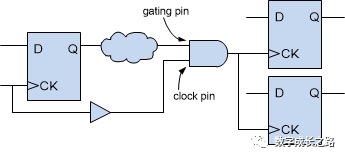

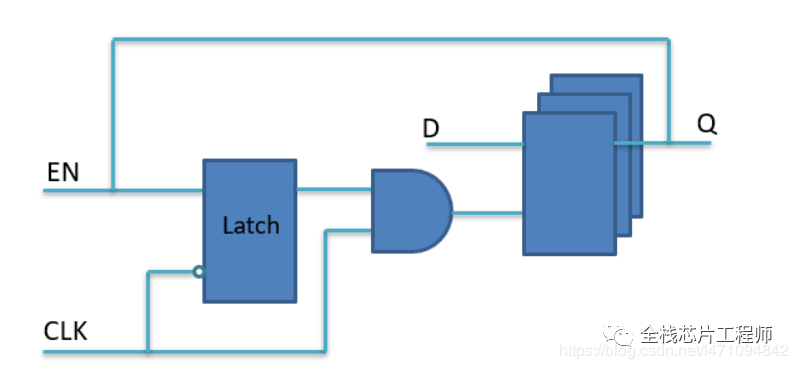

如圖所示為一款I(lǐng)CG電路結(jié)構(gòu)圖,輸入時(shí)鐘為CK,輸出時(shí)鐘為ECK,E為使能信號(hào),E為0表示關(guān)閉時(shí)鐘,ECK輸出為0。

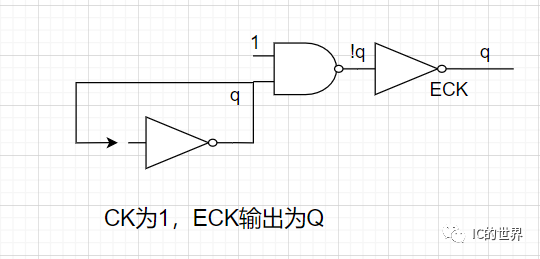

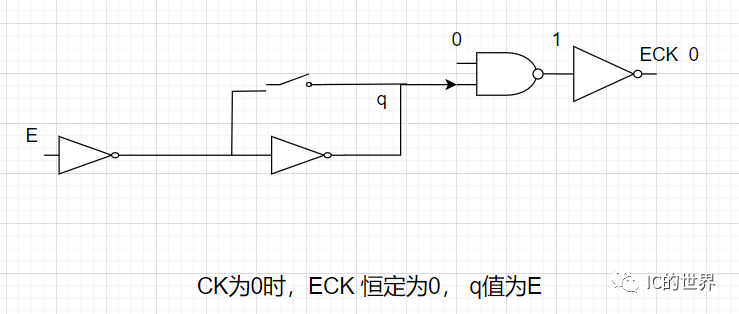

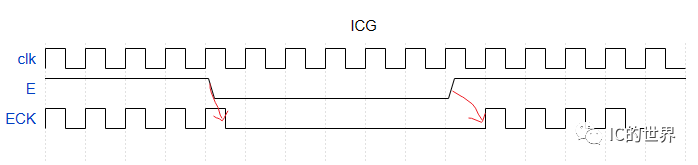

結(jié)合波形圖和電路結(jié)構(gòu)圖,可以看到:

當(dāng)CK為0時(shí),ECK 恒定為0, q值為E:如果E為1,則q為1,如果E為0,則q為0。

當(dāng)CK為1時(shí),ECK 恒定為q(n),即對(duì)應(yīng)的上一次CK為0時(shí),鎖存的E值。 因此最終的效果就是,只要E配置成了0,那么ECK會(huì)在CK的下降沿跳變成0,隨后只要E保持為0,那么ECK一直為0。 當(dāng)E從0跳變成1時(shí),ECK會(huì)在CK的下一個(gè)上升沿跳變成1.

NOTE: 建議先將E輸入信號(hào)同步到CK時(shí)鐘域,這樣E的跳變會(huì)發(fā)生在CK上升沿附近,因此在CK處于低電平時(shí),E已穩(wěn)定,有足夠的時(shí)間驅(qū)動(dòng)q值,使q達(dá)到標(biāo)準(zhǔn)電壓閾值,而不是介于0/1之間的電壓,從而保證了ECK的驅(qū)動(dòng)能力。

審核編輯:劉清

-

鎖存器

+關(guān)注

關(guān)注

8文章

925瀏覽量

42333 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

468瀏覽量

29214 -

標(biāo)準(zhǔn)電壓

+關(guān)注

關(guān)注

0文章

2瀏覽量

1354

原文標(biāo)題:clock gating 模塊電路結(jié)構(gòu)

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

降低電路漏電功耗的低功耗設(shè)計(jì)方法

clock-gating的綜合實(shí)現(xiàn)

淺析TVS管的結(jié)構(gòu)特性

淺析交流發(fā)電機(jī)轉(zhuǎn)子繞組端部結(jié)構(gòu)

基于SCM算法為CPU電壓調(diào)節(jié)設(shè)計(jì)研究

淺析LLC諧振電路的拓?fù)?b class='flag-5'>結(jié)構(gòu)與電路仿真

AND GATE的clock gating check簡(jiǎn)析

低功耗之門控時(shí)鐘設(shè)計(jì)

ASIC的clock gating在FPGA里面實(shí)現(xiàn)是什么結(jié)果呢?

淺析clock gating模塊電路結(jié)構(gòu)

淺析clock gating模塊電路結(jié)構(gòu)

評(píng)論