FIFO在設計是一個非常常見并且非常重要的模塊,很多公司有成熟的IP,所以一部分人并沒有人真正研究寫過FIFO,本文僅簡述FIFO中部分值得保留的設計思路。

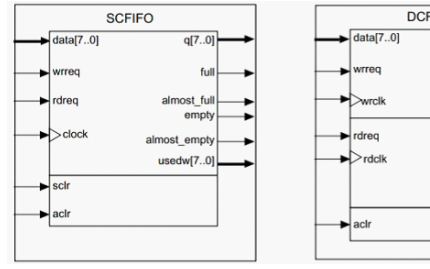

FIFO可以分為2大類:有直接使用寄存器搭的FIFO(多用于小型FIFO、和異步FIFO),也有使用SRAM搭的FIFO(多用于大型存儲)。

因為SRAM比寄存器面積小。其他更細劃分如單口,雙口等等不做詳細介紹。

本文將簡述以下兩個方向:

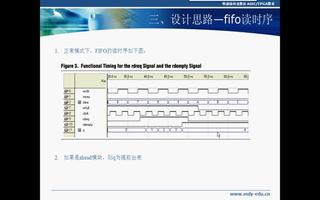

lSRAM出口通常不是當拍可以讀出數據,因此需要邏輯對這部分做邏輯,實現和寄存器相同時序。

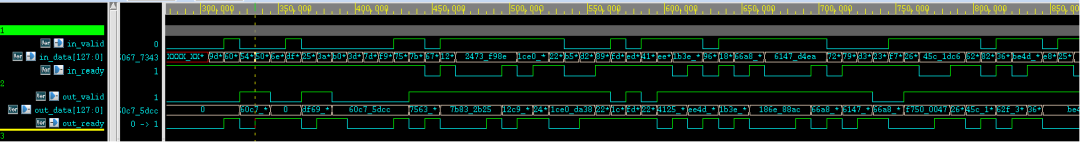

l由于第一條邏輯造成,當用戶讀取SRAM數據時會有幾拍延遲,因此為消除延遲將會增加數據輸出開關功能(見本公眾號文章模塊端口握手設計模塊多對多端口握手設計-總結)以及數據輸入切換功能。

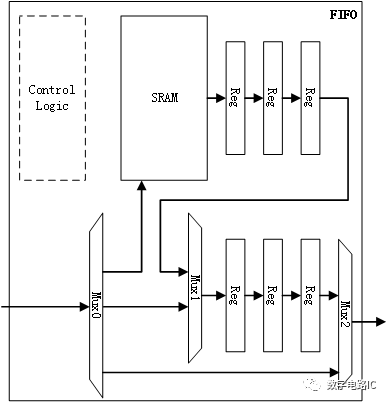

本文設計FIFO如下圖所示:

第一條中SRAM出口無法做到當怕出數的原因是由SRAM的知道工藝造成(可以在存儲器芯片手冊里看到),例如在TSMC 5nm工藝下,讀使能有效到數據穩定輸出大概需要500ps,而且如果位寬過大,在ECC時又需要幾百ps延遲,因此可能一拍數據無法收斂,因此需要幾級寄存器緩存,一般是3拍(控制信號緩存+讀數據延遲+ECC延遲)。

第二條中輸出開關功能,參見本文相應文章,功能主要保證當FIFO有數據時會傳遞至最后一級輸出寄存器中。

第二條中的輸入切換功能,是指2個mux模塊,功能主要保證輸出reg優先被填滿,當輸出reg被填滿之后,新數據才會被存入SRAM中。輸出寄存器數量和SRAM延時寄存器數量相同,保證當輸出寄存器中數據在3拍讀出之后SRAM數據經過延時之后恰好可以繼續被讀出,而不會中間出現間隔。

對于mux2的功能是在FIFO數據為空,且同時又讀寫使能,可以直接把輸入數據輸出。

上述內容僅用于同步FIFO設計,而異步大型FIFO經常采用同步SRAM緩存+異步寄存器FIFO的設計模式,有時間待續異步FIFO設計。

-

寄存器

+關注

關注

31文章

5430瀏覽量

123970 -

sram

+關注

關注

6文章

783瀏覽量

115786 -

fifo

+關注

關注

3文章

400瀏覽量

44724 -

FIFO設計

+關注

關注

0文章

7瀏覽量

5038

發布評論請先 登錄

求助verilog編寫實現AXIStream-FIFO功能思路

高速異步FIFO的設計與實現

一種異步FIFO的設計方法

什么是fifo fifo什么意思 GPIF和FIFO的區別

如何配置自己需要的FIFO?FIFO配置全攻略

FPGA之FIFO練習1:設計思路

FPGA之FIFO練習3:設計思路

FPGA之FIFO練習2:設計思路

FIFO設計—同步FIFO

淺談FIFO設計思路

淺談FIFO設計思路

評論