全文約2000字,閱讀全文需要7分鐘

簡單講,一旦擁有了開放的接口,那你擁有的就不僅僅是一款調試工具,而是一個開放的、支持DIY的客制化調試平臺,因為它將可以兼容不同家公司EDA工具、透過接口調用底層數據庫,實現想看哪就看哪的自定義功能,簡直不能更治愈!

眾人皆知,驗證離不開調試工具。在整個設計驗證流程中,驗證占了70%的工作量,調試debug就占了其中的40%。

幾乎所有驗證工具,無論是邏輯仿真、硬件仿真還是形式化驗證、原型驗證等等,本質上都是通過不同的方式去對設計進行各種重新編譯、解析,這之后產生的各種類型的數據,都離不開后面調試工具去分析、去解讀。

調試工具的本質是生產力工具,它像一個“數據處理中心”,也像一個“指揮中樞”,通過讀取、解析以及分析設計驗證的結果,讓你可以很快地看見問題、解決問題。

但是,這里說的問題映射到日常項目當中,可能是多種多樣,仿佛無窮無盡的。

本篇重點和大家分享:

一、開放接口解決什么問題

二、統一、可兼容的接口和標準

01

開放接口解決什么問題

第一個是個性化的需求

調試工具幾乎吃下了設計和驗證所有的信息。但,其實每家芯片設計的信號組合不一樣,我們通過Debug調試系統要檢查的內容就不一樣。

如果我們不能夠對于這樣的需求進行處理的話,比如說當設計的波形有兩三百個,是不是我要把兩三百個每一個批量的全部內容,都肉眼看一遍呢?因此能夠直接訪問底層數據這方面的需求,其實非常的廣。

尤其是,針對不同類型的項目,往往有自己獨有的、個性化的調試需求。

在實際應用中,各個芯片的產品調試特征不同,對調試就會產生非常多樣化的細分需求。用戶因此特別希望能夠在國產EDA工具里面看到一些開放的接口,便于自己進行二次開發。

舉個例子,比如當我們想快速對某個特定范圍下的信號變化做一些統計 (比如變化次數,X/Z的個數,均值統計等等),這些需求太多太零碎了,可能Debug產品使用界面沒有直接提供。

但這些數據信息在工具的底層數據庫里其實都有,只要提供接口讓用戶可以自己訪問底層數據庫,就可以通過寫一些小程序來實現希望的功能。真正的“想看哪里就看哪里”。

第二個是兼容性的問題

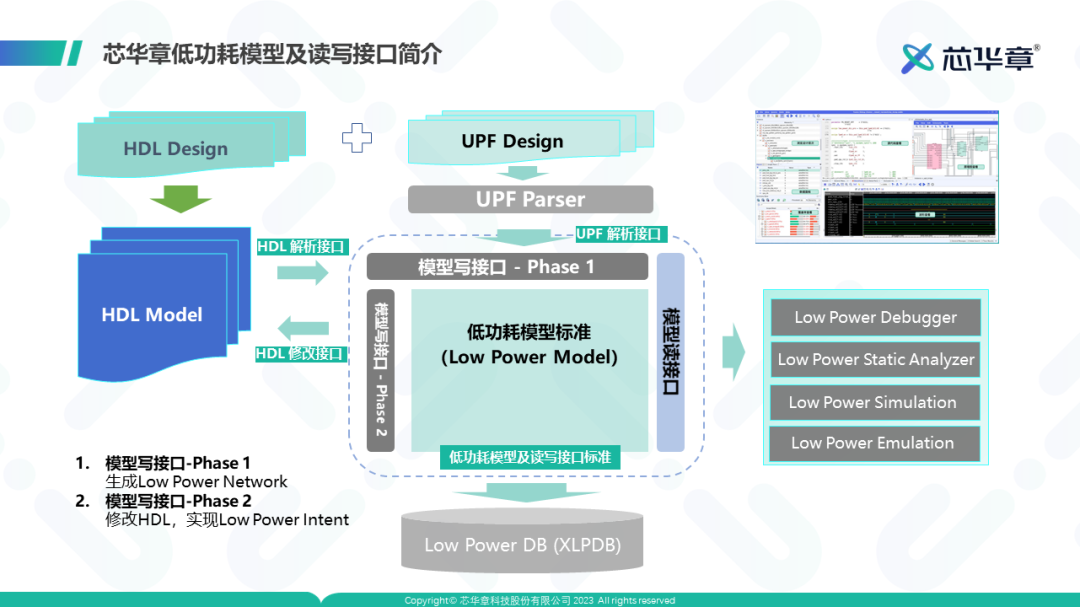

比如說,在數字驗證階段,EDA工具往往需要解析UPF/CPF文件內容,轉換為內部模型并存儲到低功耗數據庫。然而,因為各家EDA單位底層UPF/CPF的Parser的接口差異性,導致EDA工具需要針對不同的Parser做定制化。而且,不同Parser對UPF/CPF的理解可能是不同的,這會導致EDA工具一旦換了底層UPF/CPF Parser后,可能低功耗的行為就發生了變化。

開放的接口和行為級模型,能夠為行業產品的合作提供更好的兼容性和擴展性,提高數據的使用效率,也就能提高我們的生產力。

02

統一、可兼容的新一代接口和標準

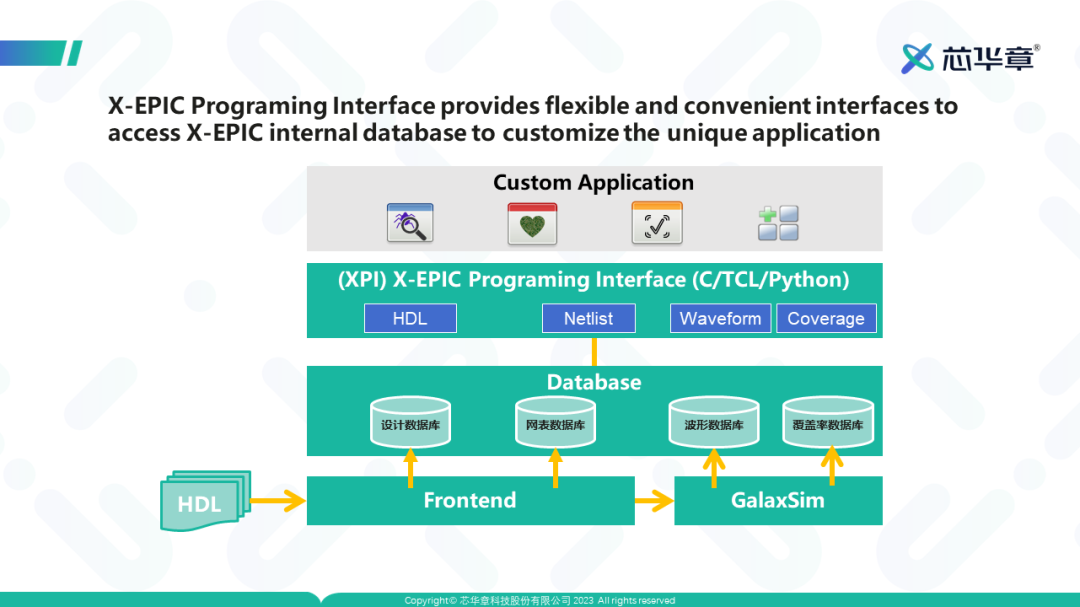

從這一具備龐大群眾基礎的需求出發,芯華章Fusion Debug提供開放的XPI接口讓用戶可以直接訪問、定制自己的小程序,調用存儲了包括靜態數據和動態數據的底層數據庫,讓設計和驗證更加有效,進行更有針對性的調試。

世上本沒有路,走的人多了,也便成了路。

XPI集成了HDL、Netlist、Waveform和Coverage 4種數據模型,并提供了簡單統一的API來訪問它們

基于芯華章統一的技術底座智V驗證平臺,HDL設計通過前端編譯生成代碼數據庫XCDB和網表數據庫XNDB

各種驗證工具如仿真器(Simulation)、硬件仿真器(Emulation), 原型系統(Prototyping)和形式化驗證(Formal Verification),則生成波形數據庫XEDB和覆蓋率數據庫XCovDB

XPI提供三種類型的接口來訪問底層數據庫模型,包括:TCL命令接口、Python接口、C/C++接口,用戶可以將這些接口集成到自己的應用程序中

這就好像以前的圖書館可能擁有數億級別的藏書,但是你找不到自己需要的書。芯華章FusionDebug則像一個用戶體驗導向的電子圖書館,不僅對龐大數據做了多種分類,并且提供清晰的檢索目錄、導覽、查閱,你甚至可以自己添加標簽和偏好,定義你想要的界面,讓你直呼“好用”的同時,大大節約你的時間。

這種統一的接口和標準,甚至不局限于芯華章自家產品之間,還可以兼容其他家EDA公司產品。以芯華章低功耗模型以及讀寫接口標準為例,它具有以下特點:

1

支持IEEE 所有UPF版本標準,并屏蔽底層UPF Parser的差異

2

支持低功耗模型創建

3

支持低功耗模型讀寫

4

支持豐富的上層應用,如低功耗靜態分析能力、Root Cause追蹤能力

Fusion Debug的通用低功耗模型,集成了對象化的低功耗網絡拓撲結構,給行業低功耗產品提供了統一、高效的追蹤行為和接口,屏蔽了各個EDA廠商HDL設計數據模型的差異性。

這也是國產EDA生態建設非常重要的一環,只有讓不同的國產EDA工具之間能夠實現低功耗數據的共享,提高數據的使用效率,才能形成完善的國產EDA生態,讓用戶擁有更高效、更省心的選擇。

實在地說一句,芯華章的Debug開發團隊有非常熱切、希望將產業現在及未來需求落實到位的工作態度和技術能力,自發布以來,Fusion Debug也已經在數十個客戶項目中得到部署和打磨。

后續我們將一一與大家分享更多功能與應用,也非常期待聽到更多來自debug用戶群體(也就是你)的反饋和聲音,給予我們繼續前進的方向和動力。

關于Fusion Debug,如有你還有更多想了解的,請關注我們這個系列。如果實在等不及了,點擊“閱讀原文”,申請下載產品單頁,里面有我們的聯系方式。

9月20日DVCon China上,我們也會攜帶包括Fusion Debug在內的芯華章數字驗證全流程工具亮相,屆時歡迎在現場與你進行更深入的交流!

-

芯華章

+關注

關注

0文章

180瀏覽量

11605

原文標題:困擾你80%時間的那20%調試問題,可以通過它來解決

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

最新 HUAWEI DevEco Studio 調試技巧

如何確定HSADC DMA的80MHZ采集速率是否正確?

DLPC3005是通過什么來響應這個曝光時間的指令的?

連接頭老是出問題?BNC 型射頻連接頭的卓越特性解決你的困擾

Wine開發系列——如何使用Wine日志調試問題

DAC7750IPWP的輸出Iout在使能輸出4--20mA時,Iout是否可以長時間懸空,對芯片是否有影響?

如何調試時間繼電器 時間繼電器的工作時間設置方法

關于峰岹的調試問題

【AI技術支持】ESP32-S3 JTAG調試問題處理

困擾你80%時間的那20%調試問題,可以通過它來解決

困擾你80%時間的那20%調試問題,可以通過它來解決

評論