1.1

什么是信號完整性

信號完整性是指在規定的時間內,信號從源端傳輸到接收端,信號不失真(能判斷出信號的高低電平)。

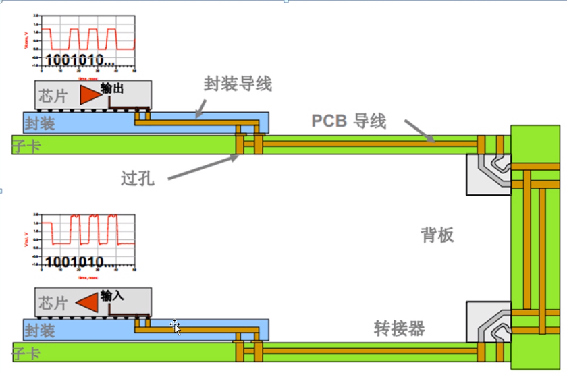

信號從源端發出以后,會經過傳輸線輸送到接收端,期間必定會受到傳輸鏈路中各種因素的影響,例如電阻、電容、連接器、芯片封裝等,這些因素會導致某些信號發生不同程度的形變,從而使接收端收到錯誤的信號電平,這些失真的信號就是所謂的信號完整性問題。

1.2

什么情況下要考慮信號完整性

早期時鐘頻率只有10MHz,對PCB的設計只需考慮如何把互連線拉通,因為對于低速信號,傳輸線本身的性能并不會影響系統的性能,所以不需要考慮信號完整性的問題,系統也能夠穩定地工作。

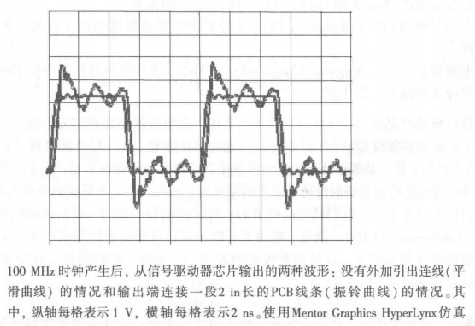

但隨著科技的進步,現在的時鐘頻率越來越高,信號的上升邊也變得越來越短。對于大多數電子產品而言,當時鐘頻率超過100MHz或信號的上升邊小于1ns時,信號完整性就變得很重要了。通常將這種領域叫做高頻/高速領域。

高速/高頻信號:當信號的上升沿小于6倍的信號傳輸延時時,則被認為是高速信號。

考慮設計周期、成本、初版成功率等因素。

1.3

信號完整性需要研究的內容

信號完整性問題通常從這幾個領域分析:

- 單一網絡的信號失真;

- 損耗引起的上升邊退化

- 相鄰網絡之間的串擾

- 地彈和電源彈

- 軌道塌陷

- 電磁干擾

過沖、下沖、回溝、振鈴、反射、衰減、串擾、阻抗突變、延時、損耗、地彈、抖動、誤碼率等等。

1.4

如何解決信號完整性問題

?經驗法則

工程師通過大量實驗數據總結出來的經驗,可以在設計之初作為參考,在進行問題查找的過程中也可作為一種判斷標準。

例:

① 信號上升時間約是時鐘周期的10%,即1/10x1/Fclock。例如100MHz時鐘的上升時間大約是1ns。

② 直徑為1MIL 的圓導線的局部電感約是25NH/IN 或1NH/MM。

?仿真

利用電氣仿真工具可用來預估互連線對信號行為造成的模擬效應。通過仿真,我們可以提前發現設計中存在的問題并提前規避。

?測量

在制造產品之前,計算對于產品性能的預估起著關鍵作用,而測量技術則對減少風險起著關鍵作用。對任何計算結果的最終測試就是測量。

-

連接器

+關注

關注

99文章

15283瀏覽量

139654 -

PCB設計

+關注

關注

396文章

4791瀏覽量

89571 -

信號完整性

+關注

關注

68文章

1438瀏覽量

96536 -

電磁干擾

+關注

關注

36文章

2385瀏覽量

106365 -

芯片封裝

+關注

關注

11文章

576瀏覽量

31316

發布評論請先 登錄

速率不高的PCB是否需要考慮信號完整性

怎樣學好“信號完整性”?

pcb信號完整性詳解

聽懂什么是信號完整性

什么是信號完整性?什么情況下要考慮信號完整性?

什么是信號完整性?什么情況下要考慮信號完整性?

評論