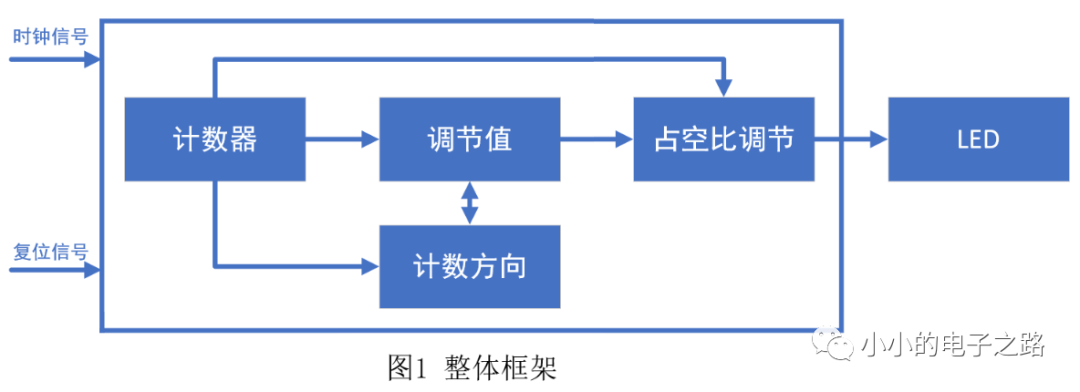

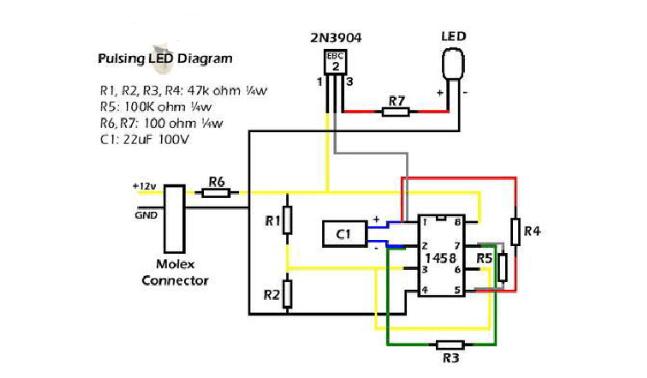

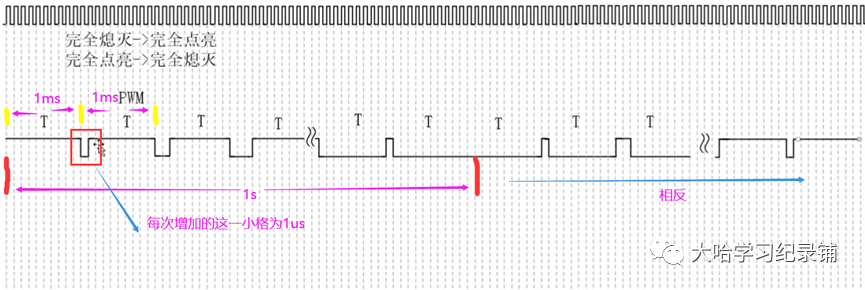

呼吸燈主要是利用PWM的方式,在固定的頻率下,通過調(diào)整占空比的方式來控制LED燈的亮度的變化,從而實現(xiàn)由暗漸亮再由亮漸暗的過程。

呼吸燈的整個FPGA實現(xiàn)流程主要由四個模塊組成,分別是計數(shù)器模塊,調(diào)節(jié)值產(chǎn)生模塊,計數(shù)方向模塊以及占空比調(diào)節(jié)模塊組成。

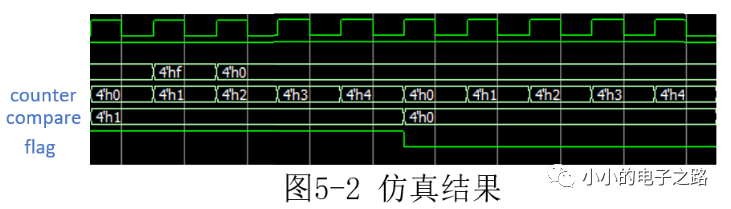

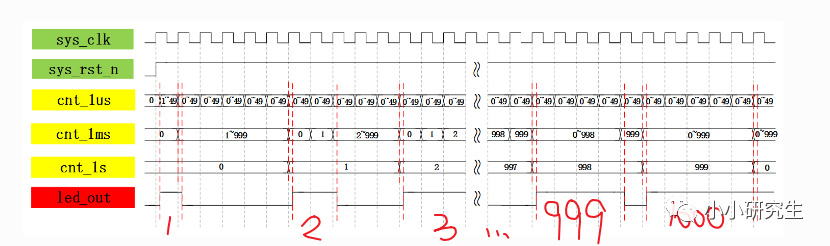

計數(shù)器模塊:計數(shù)器設(shè)置為五進(jìn)制計數(shù)器,其輸出記為counter;

調(diào)節(jié)值產(chǎn)生模塊:為五進(jìn)制加減計數(shù)器,用以產(chǎn)生占空比調(diào)節(jié)的比較值,其輸出記為compare;

計數(shù)方向模塊:通過高低電平控制調(diào)節(jié)值產(chǎn)生模塊的計數(shù)方向,其輸出記為flag;

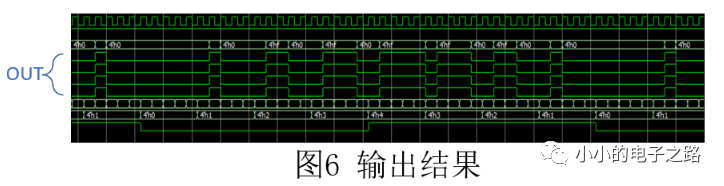

占空比調(diào)節(jié)模塊:通過比較counter和compare的值來輸出不同電平控制LED燈。

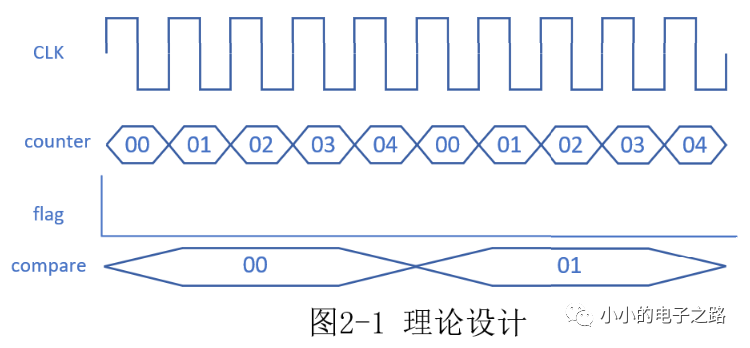

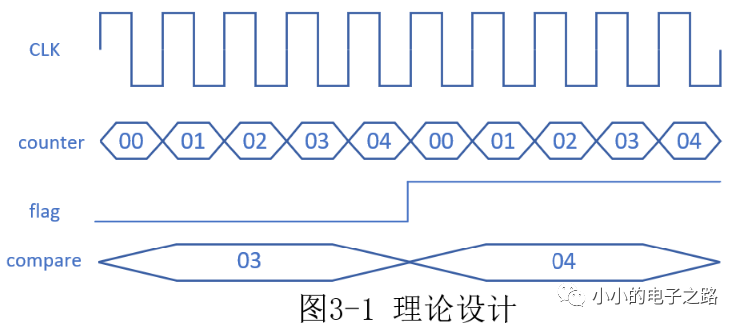

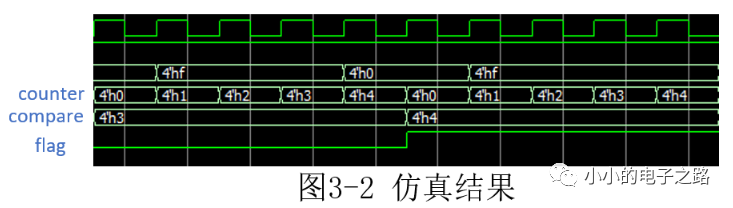

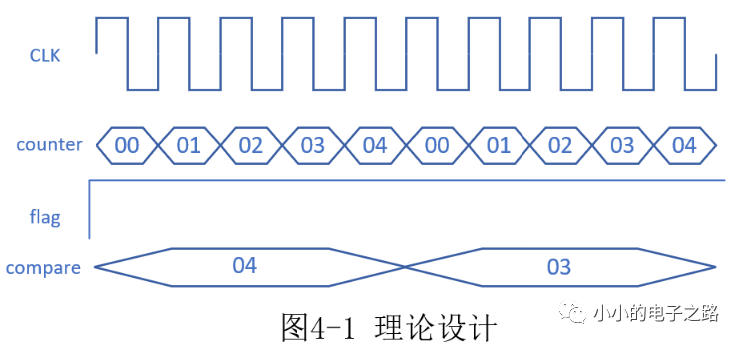

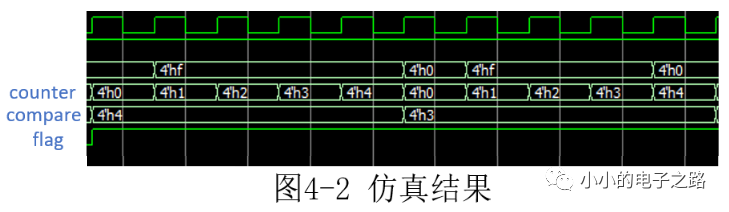

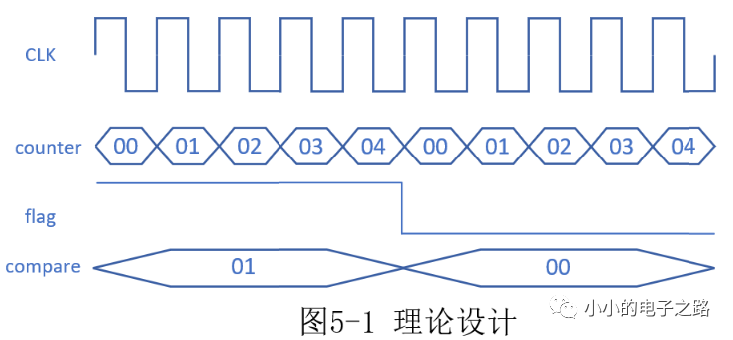

counter通過與compare相比較來產(chǎn)生不同的電平,為實現(xiàn)占空比不斷變化,即高電平持續(xù)時間不斷變化,compare需不斷變化,但是在一個周期內(nèi),compare需固定不變,因此,每當(dāng)計數(shù)器模塊溢出一次,compare需隨之改變(加1或減1),其方向由flag控制。

(1)若flag=0,counter=4,compare!=3,則加計數(shù);

(2)若flag=0,counter=4,compare=3,則flag置1;

(3)若flag=1,counter=4,compare!=1,則減計數(shù);

(4)若flag=1,counter=4,compare=1,則flag置0.

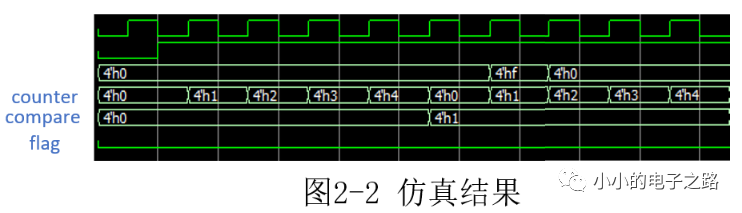

從最終的實現(xiàn)結(jié)果可以看出,輸出信號的占空比在不斷變化,實現(xiàn)了設(shè)計要求。需要注意的是,為了使呼吸燈的實驗現(xiàn)象便于觀察,需要適當(dāng)延長計數(shù)器的計數(shù)周期。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614672 -

led燈

+關(guān)注

關(guān)注

22文章

1595瀏覽量

109405 -

PWM

+關(guān)注

關(guān)注

116文章

5409瀏覽量

218306 -

計數(shù)器

+關(guān)注

關(guān)注

32文章

2287瀏覽量

96091 -

呼吸燈

+關(guān)注

關(guān)注

10文章

112瀏覽量

43131

發(fā)布評論請先 登錄

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計原理與應(yīng)用52_1_PWM呼吸燈(PPT講解)-3

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計原理與應(yīng)用52_2_PWM呼吸燈(實操案例)-1

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計原理與應(yīng)用52_2_PWM呼吸燈(實操案例)-2

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計原理與應(yīng)用52_2_PWM呼吸燈(實操案例)-3

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計原理與應(yīng)用52_2_PWM呼吸燈(實操案例)-4

基于CPLD/FPGA的呼吸燈效果實現(xiàn)(附全部verilog源碼)(by 大飛)

xilinx ISE 中異步FIFO ip的使用、仿真及各信號的討論(圖文教程)

霧盈FPGA筆記之(一):基于FPGA的呼吸燈簡單實驗程序(Verilog)

FPGA之呼吸燈

基于CPLD/FPGA的呼吸燈效果實現(xiàn)_呼吸燈源碼_明德?lián)P資料

基于FPGA的呼吸燈設(shè)計

基于FPGA的呼吸燈設(shè)計(附源工程)

紫光同創(chuàng)FPGA教程:呼吸燈——盤古系列PGX-Nano開發(fā)板實驗例程

基于FPGA的呼吸燈設(shè)計

基于FPGA的呼吸燈設(shè)計

評論