Vivado2019.1/win10

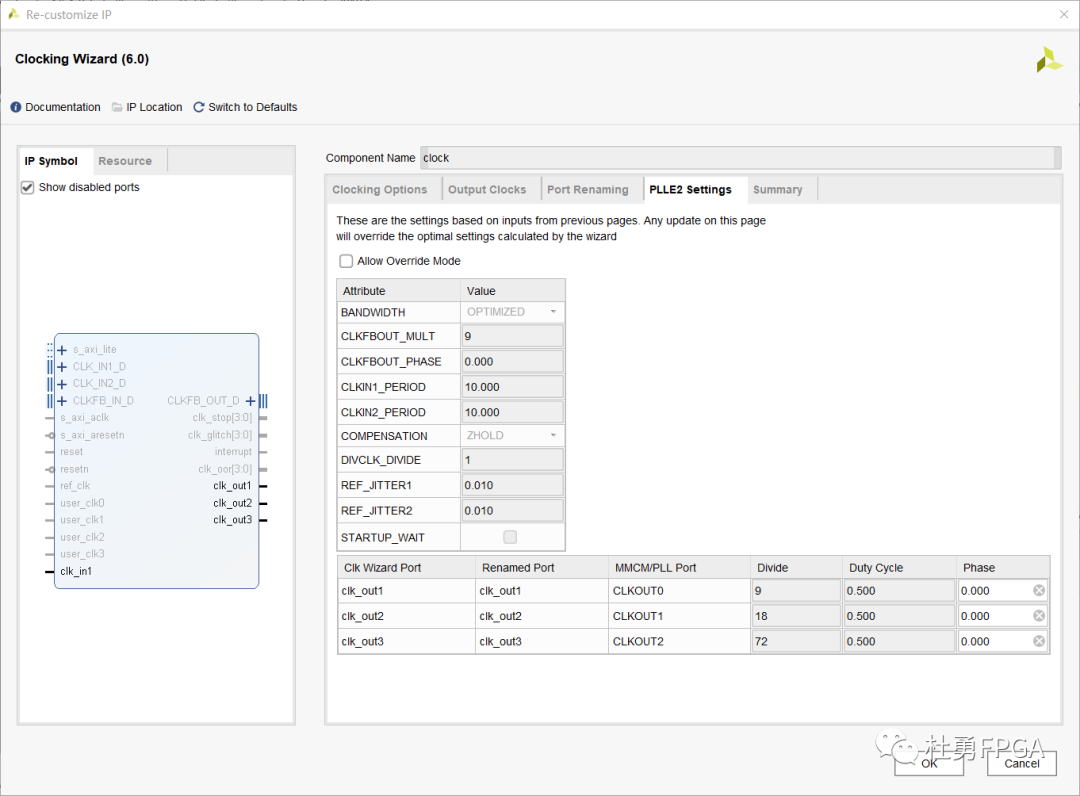

調用MMCU產生時鐘,輸入時鐘頻率為100M,產生100M、50M、12.5M時鐘輸出,MMCU核自動生成的時鐘倍頻數為9,即主時鐘為900M,分別分頻9得100M,18得50M,72得12.5M。

在約束文件中,設置了輸入時鐘的頻率為50M。

create_clock -period 20 [get_ports gclk]。

實現程序時報錯:

[DRC PDRC-43] PLL_adv_ClkFrequency_div_no_dclk: The computed value 450.000 MHz (CLKIN1_PERIOD, net gclk_IBUF) for the VCO operating frequency of the PLLE2_ADV site PLLE2_ADV_X0Y0 (cell u0/inst/plle2_adv_inst) falls outside the operating range of the PLL VCO frequency for this device (800.000 - 1866.000 MHz). The computed value is (CLKFBOUT_MULT_F * 1000 / (CLKINx_PERIOD * DIVCLK_DIVIDE)). Please adjust either the input period CLKINx_PERIOD (20.000000), multiplication factor CLKFBOUT_MULT_F (9) or the division factor DIVCLK_DIVIDE (1), in order to achieve a VCO frequency within the rated operating range for this device.

錯誤信息提示,主時鐘根據計算為450M,不在VCO的工作范圍內(800-1866M),需要調整倍頻因子。

原因:

IP核設置的參數中輸入時鐘為100M,主時鐘為900M(倍頻因子為9),但約束文件中設置的輸入時鐘為50M。程序實現時,IP核的輸入時鐘頻率竟然會按約束文件中的參數運算。

解決方案:

修改約束文件

create_clock -period10 [get_ports gclk]。

IP核設置多少,時序約束就設置多少,可避免此類問題。

審核編輯:劉清

-

時鐘約束

+關注

關注

0文章

15瀏覽量

6104 -

PLL電路

+關注

關注

0文章

92瀏覽量

6735

原文標題:Vivado調試筆記-MMCU/PLL時鐘約束導致的問題

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IIC總線調試筆記

PSFB調試筆記分享!

調試筆記--keil 測量周期小技巧 相關資料分享

ARM調試 AT91SAM7S64調試筆記

MMCU/PLL時鐘約束導致的問題調試筆記

MMCU/PLL時鐘約束導致的問題調試筆記

評論