單口 RAM

module BRAM_PORTA(

input clka,

input ena,

input wea,

input [3:0] addra,

input [15:0] dina,

output reg [15:0] douta

);

reg [15:0] mem [15:0];

always @(posedge clka)begin

if(ena)begin

if(wea)begin//寫數(shù)據(jù)

mem[addra] <= dina;

douta <= 16'bzzzzzzzzzzzzzzzz;

end

else begin //讀數(shù)據(jù)

douta <= mem[addra];

mem[addra] <= mem[addra];

end

end

else

douta <= 16'bzzzzzzzzzzzzzzzz;

end

endmodule

同步 FIFO

`define INDEX 6

`define WIDTH 16

`define DEPTH 64

module Sync_FIFO(

input clk,

input rst_n,

input re,

input we,

input [`WIDTH-1:0] din,

output empty,

output full,

output reg [`INDEX-1:0] fifo_cnt,

output reg [`WIDTH-1:0] dout

);

reg [`WIDTH-1:0] mem [`DEPTH-1:0];

reg [`INDEX-1:0] raddr;

reg [`INDEX-1:0] waddr;

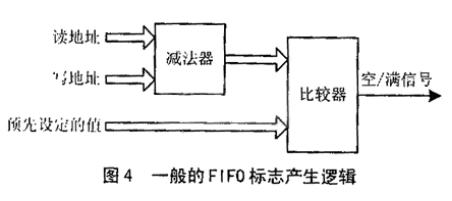

// 1、空滿標志;

assign empty = (fifo_cnt == 0) ? 1:0;

assign full = (fifo_cnt == `DEPTH-1) ? 1:0;

// 2、讀寫計數(shù);

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

fifo_cnt <= 0;

else begin

if((!empty && re)&&(!full && we))// 同時讀寫,計數(shù)不變;

fifo_cnt <= fifo_cnt;

else if(!empty && re)// 讀數(shù)據(jù),計數(shù)減一;

fifo_cnt <= fifo_cnt - 1'b1;

else if(!full && we)// 寫數(shù)據(jù),計數(shù)加一;

fifo_cnt <= fifo_cnt + 1'b1;

else

fifo_cnt <= fifo_cnt;

end

end

// 3、讀寫數(shù)據(jù);

always @(posedge clk or negedge rst_n)begin// 讀數(shù)據(jù);

if(!rst_n)

dout <= 0;

else begin

if(!empty && re)

dout <= mem[raddr];

else

dout <= dout;

end

end

always @(posedge clk)begin// 寫數(shù)據(jù);

if(!full && we)

mem[raddr] <= din;

else

mem[raddr] <= mem[waddr];

end

// 4、讀寫地址;

always @(posedge clk or negedge rst_n)begin// 寫地址;

if(!rst_n)

waddr <= 0;

else begin

if(!full && we)

waddr <= waddr + 1'b1;

else

waddr <= waddr;

end

end

always @(posedge clk or negedge rst_n)begin// 讀地址;

if(!rst_n)

raddr <= 0;

else begin

if(!empty && re)

raddr <= raddr + 1'b1;

else

raddr <= raddr;

end

end

endmodule

異步 FIFO

`define INDEX 6 // FIFO 索引;

`define WIDTH 16 // FIFO 寬度;

`define DEPTH 64 // FIFO 深度;

module Async_FIFO(

input rd_clk,

input wr_clk,

input rst_n,

input re,

input we,

input [`WIDTH-1:0] din,

output empty,

output full,

output [`WIDTH-1:0] dout

);

reg [`WIDTH-1:0] mem [`DEPTH-1:0];

wire [`INDEX-1:0] raddr;

wire [`INDEX-1:0] waddr;

reg [`INDEX:0] wbin,rbin;

wire [`INDEX:0] wbin_next,rbin_next,wgray_next,rgray_next;

reg [`INDEX:0] rp,wr1_rp,wr2_rp,wp,rd1_wp,rd2_wp;

// 1、空滿標志;

// 可能需要延時;

assign empty = (rd2_wp == rgray_next) ? 1:0;

assign full = ({~wr2_rp[`INDEX:`INDEX-1],wr2_rp[`INDEX-2:0]} == wgray_next) ? 1:0;// 高兩位不同,取反;

// 2、讀計數(shù);

// 產(chǎn)生讀地址 raddr + 讀地址自增 + 將普通二進制碼轉(zhuǎn)化為格雷碼,并賦給讀指針 rp;

// 將讀指針 rp 同步到寫時鐘域;

always @(posedge rd_clk or negedge rst_n)begin

if(!rst_n)

{rbin,rp} <= 0;

else

{rbin,rp} <= {rbin_next,rgray_next};

end

assign raddr = rbin[`INDEX-1:0];// 拋棄高位;

assign rbin_next = rbin + (!empty && re);// 地址加一;

assign rgray_next = rbin_next ^ (rbin_next > > 1);// 轉(zhuǎn)為格雷碼,右移 + 異或;

always @(posedge wr_clk or negedge rst_n)begin

if(!rst_n)

{wr2_rp,wr1_rp} <= 0;

else

{wr2_rp,wr1_rp} <= {wr1_rp,rp};

end

// 3、寫計數(shù);

// 產(chǎn)生寫地址 waddr + 寫地址自增 + 將普通二進制碼轉(zhuǎn)化為格雷碼,并賦給寫指針 wp;

// 將寫指針 wp 同步到讀時鐘域;

always @(posedge wr_clk or negedge rst_n)begin

if(!rst_n)

{wbin,wp} <= 0;

else

{wbin,wp} <= {wbin_next,wgray_next};

end

assign waddr = wbin[`INDEX-1:0];// 拋棄高位;

assign wbin_next = wbin + (!full && we);// 地址加一;

assign wgray_next = wbin_next ^ (wbin_next > > 1);// 轉(zhuǎn)為格雷碼,右移 + 異或;

always @(posedge rd_clk or negedge rst_n)begin

if(!rst_n)

{rd2_wp,rd1_wp} <= 0;

else

{rd2_wp,rd1_wp} <= {rd1_wp,wp}; // 多比特的,但是只有單比特發(fā)生變化,屬于單比特處理領(lǐng)域;

end

// 4、異步讀數(shù)據(jù);

assign dout = mem[raddr];

// 5、同步寫數(shù)據(jù);

always @(posedge wr_clk)begin

if(!full && we)

mem[waddr] <= din;

else

mem[waddr] <= mem[waddr];

end

endmodule

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

RAM

+關(guān)注

關(guān)注

8文章

1392瀏覽量

117393 -

二進制

+關(guān)注

關(guān)注

2文章

807瀏覽量

42307 -

FIFO芯片

+關(guān)注

關(guān)注

0文章

10瀏覽量

9004 -

FIFO存儲

+關(guān)注

關(guān)注

0文章

103瀏覽量

6184 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17604

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

同步FIFO設計詳解及代碼分享

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數(shù)字 IC 設計中非常常用。 根據(jù)接入的時鐘信號,可以分為同步 FIFO 和異步

發(fā)表于 06-27 10:24

?2727次閱讀

異步FIFO結(jié)構(gòu)及FPGA設計

首先介紹異步FIFO 的概念、應用及其結(jié)構(gòu),然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法; 在傳統(tǒng)設計的基礎上提出一種新穎的電路結(jié)構(gòu)并對其進行綜合仿真和FPGA 實現(xiàn)。

發(fā)表于 04-16 09:25

?46次下載

Camera Link接口的異步FIFO設計與實現(xiàn)

介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計

發(fā)表于 07-28 16:08

?32次下載

異步FIFO結(jié)構(gòu)及FPGA設計

摘要:首先介紹異步FIFO的概念、應用及其結(jié)構(gòu),然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法;在傳統(tǒng)設計的基礎上提出一種新穎的電路結(jié)構(gòu)并對其進行

發(fā)表于 06-20 12:46

?3997次閱讀

異步FIFO的設計分析及詳細代碼

本文首先對異步 FIFO 設計的重點難點進行分析,最后給出詳細代碼。 一、FIFO簡單講解 FIFO的本質(zhì)是RAM, 先進先出 重要參數(shù):

發(fā)表于 11-15 12:52

?8948次閱讀

基于FPGA的異步FIFO設計方法詳解

在現(xiàn)代電路設計中,一個系統(tǒng)往往包含了多個時鐘,如何在異步時鐘間傳遞數(shù)據(jù)成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO

發(fā)表于 07-17 08:33

?8639次閱讀

基于異步FIFO結(jié)構(gòu)原理

在現(xiàn)代的集成電路芯片中,隨著設計規(guī)模的不斷擴大,一個系統(tǒng)中往往含有數(shù)個時鐘。多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個

發(fā)表于 02-07 14:22

?0次下載

異步fifo詳解

和寫入數(shù)據(jù)(對于大型數(shù)據(jù)存儲,在性能上必然緩慢),其數(shù)據(jù)地址是由內(nèi)部讀寫指針自動加一完成的,不能像普通的存儲器一樣,由地址線決定讀取或者寫入某個特定地址的數(shù)據(jù),按讀寫是否為相同時鐘域分為同步和異步FIFO,這里主要介紹

FIFO設計—同步FIFO

FIFO是異步數(shù)據(jù)傳輸時常用的存儲器,多bit數(shù)據(jù)異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

發(fā)表于 05-26 16:12

?1866次閱讀

同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO各在什么情況下應用

同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步

同步FIFO和異步FIFO區(qū)別介紹

,并且間隔時間長,也就是突發(fā)寫入。那么通過設置一定深度的FIFO,可以起到數(shù)據(jù)暫存的功能,且使得后續(xù)處理流程平滑。 時鐘域的隔離:主要用異步FIFO。對于不同時鐘域的數(shù)據(jù)傳輸,可以通過FIFO

單口RAM、同步FIFO、異步FIFO的設計

單口RAM、同步FIFO、異步FIFO的設計

評論