異步fifo詳解

一. 什么是異步FIFO

FIFO即First in First out的英文簡稱,是一種先進先出的數(shù)據(jù)緩存器,與普通存儲器的區(qū)別在于沒有外部讀寫的地址線,缺點是只能順序的讀取和寫入數(shù)據(jù)(對于大型數(shù)據(jù)存儲,在性能上必然緩慢),其數(shù)據(jù)地址是由內(nèi)部讀寫指針自動加一完成的,不能像普通的存儲器一樣,由地址線決定讀取或者寫入某個特定地址的數(shù)據(jù),按讀寫是否為相同時鐘域分為同步和異步FIFO,這里主要介紹異步FIFO,主要用于跨時鐘域傳輸數(shù)據(jù)。

FIFO是一種數(shù)據(jù)緩沖器,用來實現(xiàn)數(shù)據(jù)先入先出的讀/寫方式。FIFO有一個寫端口和一個讀端口,外部無需使用者控制地址,使用方便。FIFO與普通的Block RAM有一個很明顯的區(qū)別就是使用Block RAM來做數(shù)據(jù)緩存處理,使用者必須自己控制讀和寫地址的管理,必須保證寫的數(shù)據(jù)不把Block RAM中未被讀出的內(nèi)容覆蓋掉從而造成數(shù)據(jù)錯誤,同時保證讀的時候要讀出未被寫入的地址。而采用FIFO時,只需要關(guān)注FIFO控制器給出的空滿狀態(tài)信號即可知道當前有沒有錯誤的操作了FIFO,使FIFO的數(shù)據(jù)寫溢出或讀空。

異步FIFO讀寫分別采用相互異步的不同時鐘,使用異步FIFO可以在兩個不同時鐘系統(tǒng)之間快速而方便地傳輸實時數(shù)據(jù)

FIFO的常見參數(shù)

FIFO的寬度:即FIFO一次讀寫操作的數(shù)據(jù)位;

FIFO的深度:指的是FIFO可以存儲多少個N位的數(shù)據(jù)(如果寬度為N)。

滿標志:FIFO已滿或?qū)⒁獫M時由FIFO的狀態(tài)電路送出的一個信號,以阻止FIFO的寫操作繼續(xù)向FIFO中寫數(shù)據(jù)而造成溢出(overflow)。

空標志:FIFO已空或?qū)⒁諘r由FIFO的狀態(tài)電路送出的一個信號,以阻止FIFO的讀操作繼續(xù)從FIFO中讀出數(shù)據(jù)而造成無效數(shù)據(jù)的讀出(underflow)。

讀時鐘:讀操作所遵循的時鐘,在每個時鐘沿來臨時讀數(shù)據(jù)。

寫時鐘:寫操作所遵循的時鐘,在每個時鐘沿來臨時寫數(shù)據(jù)。

二、設(shè)計原理

2.1結(jié)構(gòu)框圖

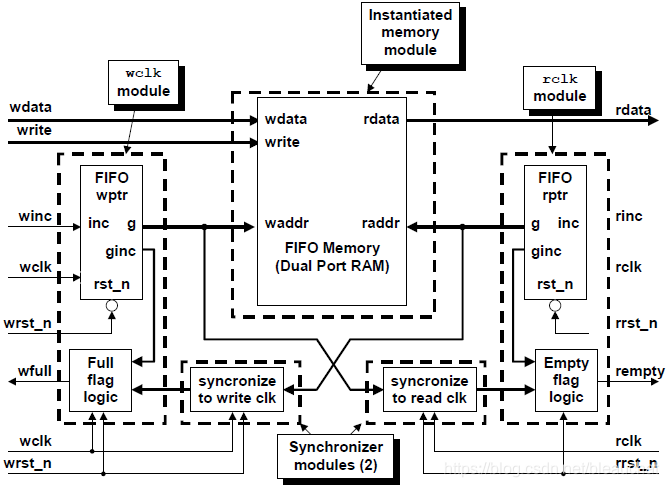

如上圖所示的同步模塊synchronize to write clk,其作用是把讀時鐘域的讀指針rd_ptr采集到寫時鐘(wr_clk)域,然后和寫指針wr_ptr進行比較從而產(chǎn)生或撤消寫滿標志位wr_full;類似地,同步模塊synchronize to read clk的作用是把寫時鐘域的寫指針wr_ptr采集到讀時鐘域,然后和讀指針rd_ptr進行比較從而產(chǎn)生或撤消讀空標志位rd_empty。

另外還有寫指針wr_ptr和寫滿標志位wr_full產(chǎn)生模塊,讀指針rd_ptr和讀空標志位rd_empty產(chǎn)生模塊,以及雙端口存儲RAM模塊。

2.2 二進制計數(shù)器存在的問題

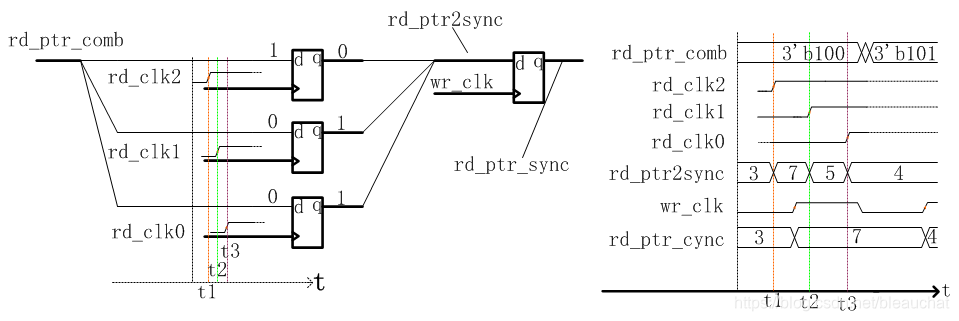

異步FIFO讀寫指針需要在數(shù)學上的操作和比較才能產(chǎn)生準確的空滿標志位,但由于讀寫指針屬于不同的時鐘域及讀寫時鐘相位關(guān)系的不確定性,同步模塊采集另一時鐘域的指針時,此指針有可能正處在跳變的過程中,如下圖所示,那么采集到的值很有可能是不期望的值,當然,不期望的錯誤結(jié)果也會隨之發(fā)生。

上圖中,rd_ptr2sync 3和4以及4和5之間的中間態(tài)是由于到各寄存器的時鐘rd_clk存在偏差而引起的。二進制的遞增操作,在大多數(shù)情況下都會有兩位或者兩以上的bit位在同一個遞增操作內(nèi)發(fā)生變化,但由于實際電路中會存在時鐘偏差和不同的路徑延時,二進制計數(shù)器在自增時會不可避免地產(chǎn)生錯誤的中間結(jié)果,如下圖。

由于rd_clk上升沿到達三寄存器的時間各不相同,這就導致了rd_ptr2sync的值從3’b011跳變3’b100的過程中經(jīng)歷了3’b111和3’b101,直到最后一個時鐘(rd_clk0)沿的到來后rd_ptr2sync才跳變到正確結(jié)果3’b100。中間結(jié)果的持續(xù)的時間雖然相對短暫,但是這些不正確的中間結(jié)果完全有可能被其它時鐘域的同步模塊采集到而產(chǎn)生錯誤的動作,見上圖。

由此可見,要避免中間結(jié)果的產(chǎn)生,其中一個可行的方案就是使被同步模塊采集的數(shù)據(jù)遞變時,每次只有一個bit位發(fā)生改變。格雷碼計數(shù)器就是一個不錯的選擇。

-

fifo

+關(guān)注

關(guān)注

3文章

400瀏覽量

44698

發(fā)布評論請先 登錄

cy7c68013a異步slave fifo模式,外部mcu無法讀寫fifo怎么解決?

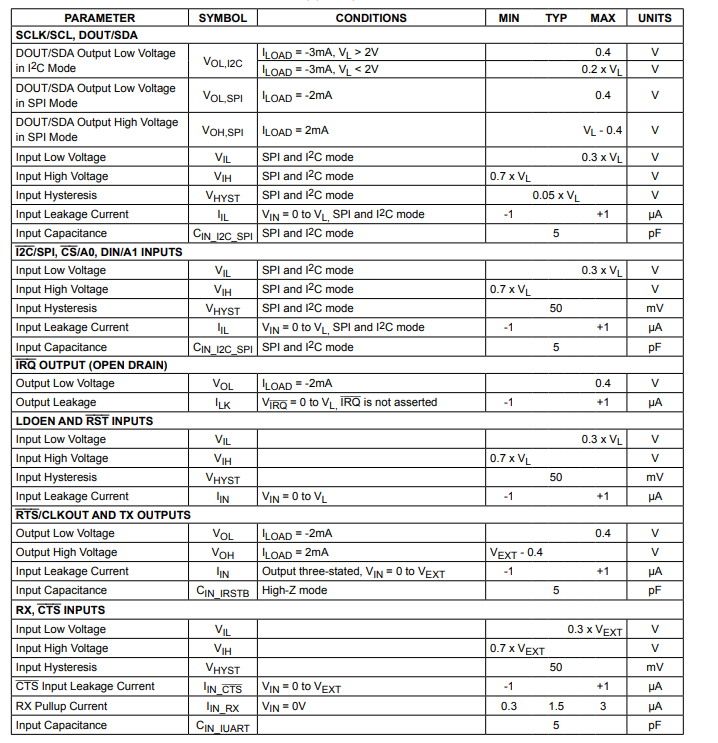

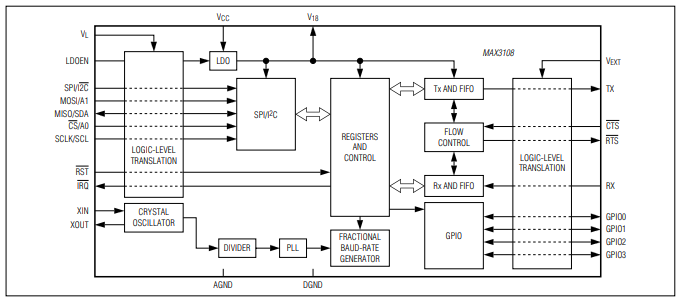

MAX3107SPI/I2C UART,具有128字FIFO技術(shù)手冊

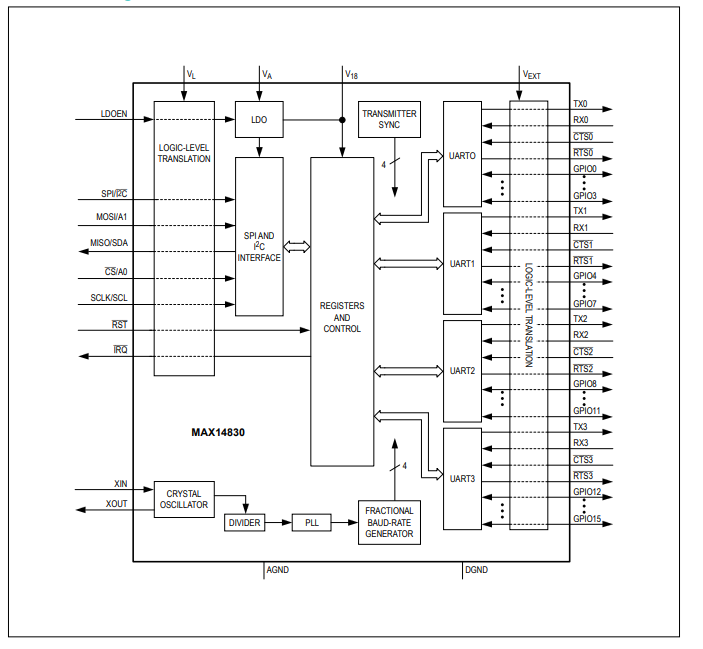

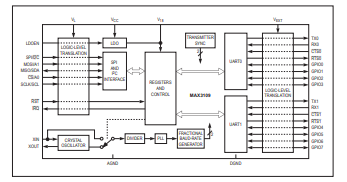

MAX14830四通道串行UART,具有128字FIFO技術(shù)手冊

MAX3108 SPI/I2C UART,具有128字FIFO,WLP封裝技術(shù)手冊

MAX3109雙通道串行UART,帶有128字FIFO技術(shù)手冊

智多晶FIFO_Generator IP介紹

基于FPGA的FIFO實現(xiàn)

AXI接口FIFO簡介

解鎖TSMaster fifo函數(shù):報文讀取的高效方法

SDRAM控制器的設(shè)計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

FIFO IP核的使用教程

FIFO Generator的Xilinx官方手冊

FIFO的深度應(yīng)該怎么計算

Efinity FIFO IP仿真問題 -v1

具有FIFO的雙異步通信元件TL16C552A數(shù)據(jù)表

異步fifo詳解

異步fifo詳解

評論