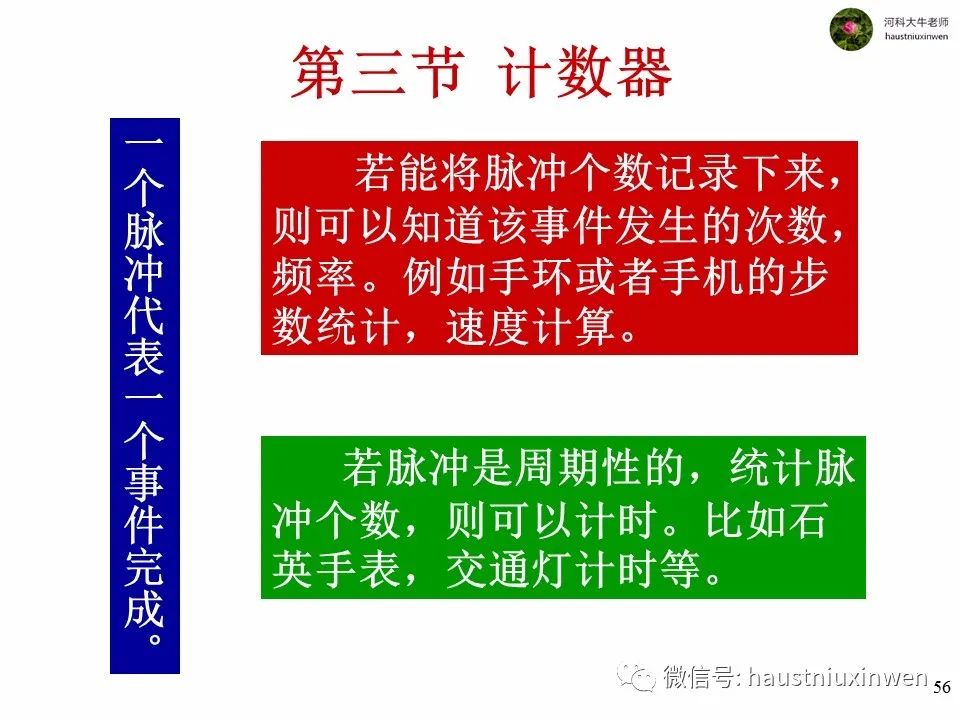

在數(shù)字系統(tǒng)中,使用得最多的時序電路差不多就是計數(shù)器了。計數(shù)器不僅能夠用于對時鐘脈沖計數(shù),還可以用于分頻、定時、產(chǎn)生節(jié)拍脈沖、產(chǎn)生脈沖序列以及進行數(shù)字運算等等。

其實,計數(shù)也是一種最簡單最基本的運算,就像我們心里默念的計數(shù)一樣。不過不同的是,計數(shù)器是有一定頻率的計數(shù),具有一定的時間間隔,而我們心里默念的計數(shù)的時間間隔不一樣罷了(也就是不夠準確的啦),而計數(shù)器就是實現(xiàn)這種運算的邏輯電路,主要是通過對時鐘(上升)脈沖的個數(shù)進行計數(shù)的。

計數(shù)器在我們身邊也很普遍,比如手機中自帶的跑步的計時器、電腦定時關(guān)機等等;所以,熟悉掌握計數(shù)器,不僅對于學(xué)習(xí) Verilog 非常有用,而且,還能鍛煉我們的邏輯能力和更深刻地理解數(shù)字電路的工作原理,從而對科技更加感興趣!

一、計數(shù)器的 Verilog 代碼實現(xiàn)和 RTL 電路實現(xiàn)

下面是計數(shù)器的 Verilog 代碼實現(xiàn):

module Counters(

input Clk,

input Up, // 可增可減(可逆)計數(shù)器

output reg [7:0] Cout = 8'b0000_0000 // 8 位計數(shù)器

);

always @(posedge Clk)

if (Up)

Cout <= Cout + 1'b1;

else

Cout <= Cout - 1'b1;

endmodule

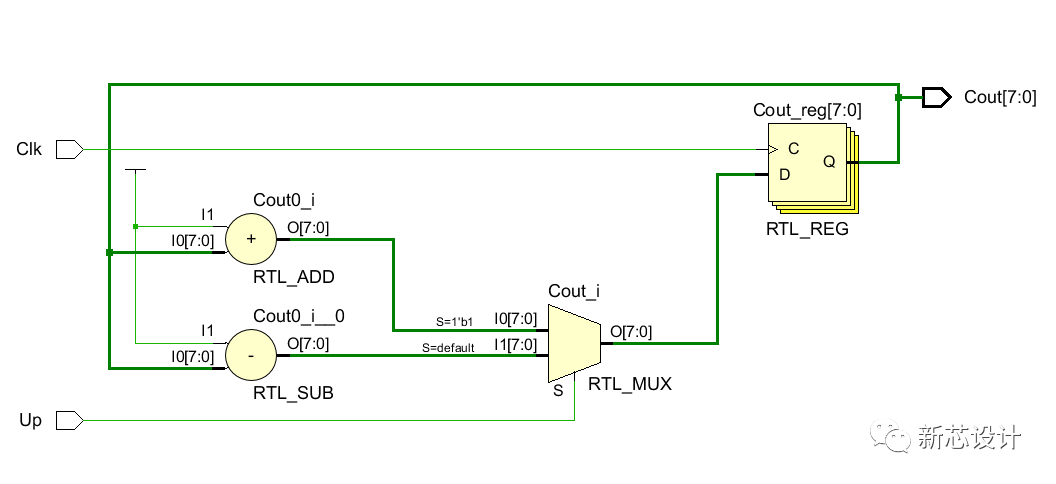

下面是計數(shù)器的 RTL 電路實現(xiàn):

計數(shù)器的 RTL 電路圖

時鐘信號:Clk(時鐘信號,就是電路的“心臟”,不可或缺);

復(fù)位信號:rst_n(復(fù)位信號,也是一個合格的電路不應(yīng)該缺少的一個輸入信號,當(dāng)復(fù)位信號為低電平時,輸出全部置零,這就是所謂的低電平有效)當(dāng)復(fù)位信號為高電平時,開始計數(shù),每一個時鐘信號的上升沿到來就計一次數(shù),每計數(shù)滿 256 個時鐘周期為一個輸出循環(huán),輸出置零,然后重新計數(shù);當(dāng)然,這里為了更好地讀懂代碼,并沒有加入復(fù)位信號啊哈哈哈嗝。

計數(shù)值信號:Cout(顯示計數(shù)值,根據(jù)自己設(shè)計的需要,可以對位數(shù)進行設(shè)置,比如最大計數(shù)值為 6,那么位數(shù)就可以設(shè)置為 3 bits)

其實,這個既是計數(shù)器,又能當(dāng)分頻器,而且還能當(dāng)計時器喲(再者還可以當(dāng)鬧鐘功能)這三者其實都是息息相關(guān)的,但是博主并沒有把分頻器和定時器的功能加上去,其實只需要增加一兩個信號即可,小伙伴們能否想到怎么添加,從而使得這個程序既有計數(shù)器的功能,也有分頻器的功能和定時器的功能呢?

-

計數(shù)器

+關(guān)注

關(guān)注

32文章

2291瀏覽量

96438 -

時序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21950 -

RTL

+關(guān)注

關(guān)注

1文章

389瀏覽量

61148 -

計時器

+關(guān)注

關(guān)注

1文章

432瀏覽量

33763 -

Verilog設(shè)計

+關(guān)注

關(guān)注

0文章

20瀏覽量

6640

發(fā)布評論請先 登錄

招聘:數(shù)字電路設(shè)計師

數(shù)字電路設(shè)計的基本方法有哪些

數(shù)字電路設(shè)計

計數(shù)器的定義和分類

基于計數(shù)器的數(shù)字電子鐘的設(shè)計

數(shù)字電路組成的計數(shù)器原理電路

基于Verilog的經(jīng)典數(shù)字電路設(shè)計—計數(shù)器

基于Verilog的經(jīng)典數(shù)字電路設(shè)計—計數(shù)器

評論