偶分頻

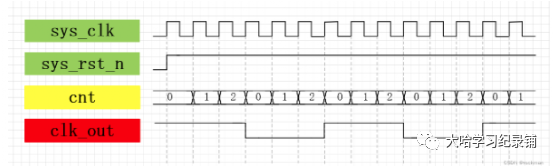

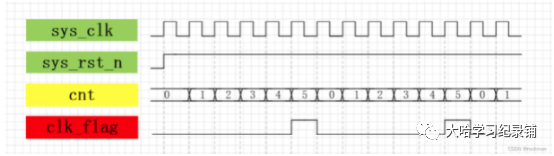

5.1計數實現偶12分頻(占空比50%)

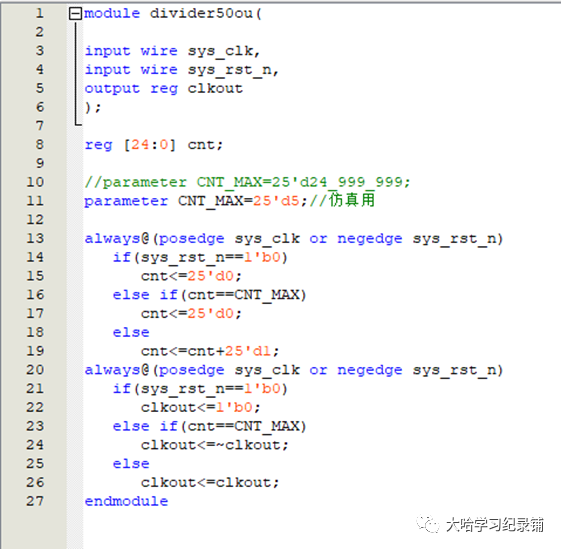

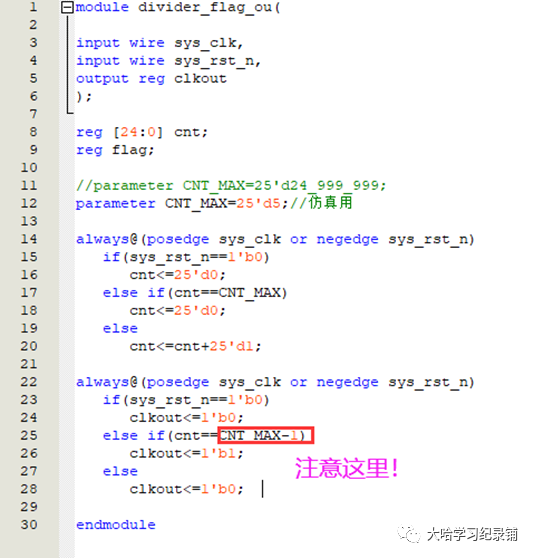

5.1.1源碼

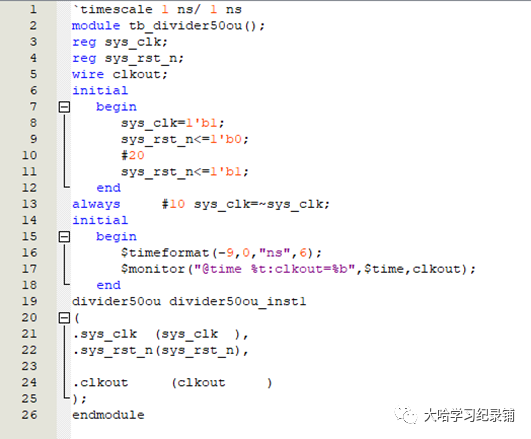

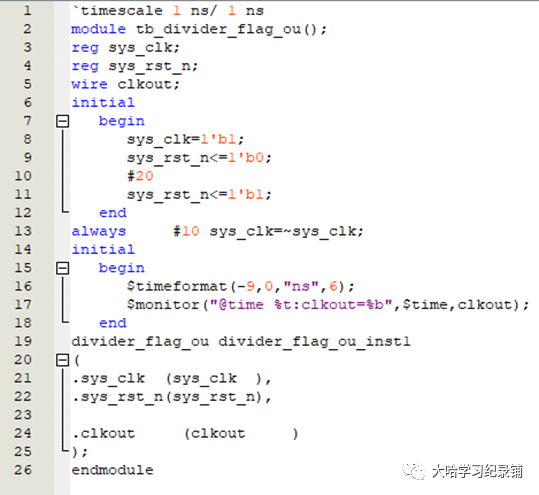

5.1.2測試源碼

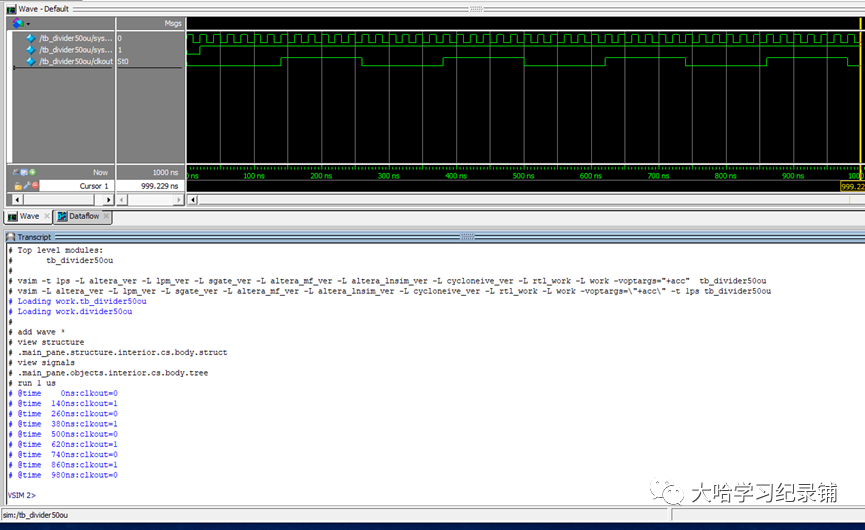

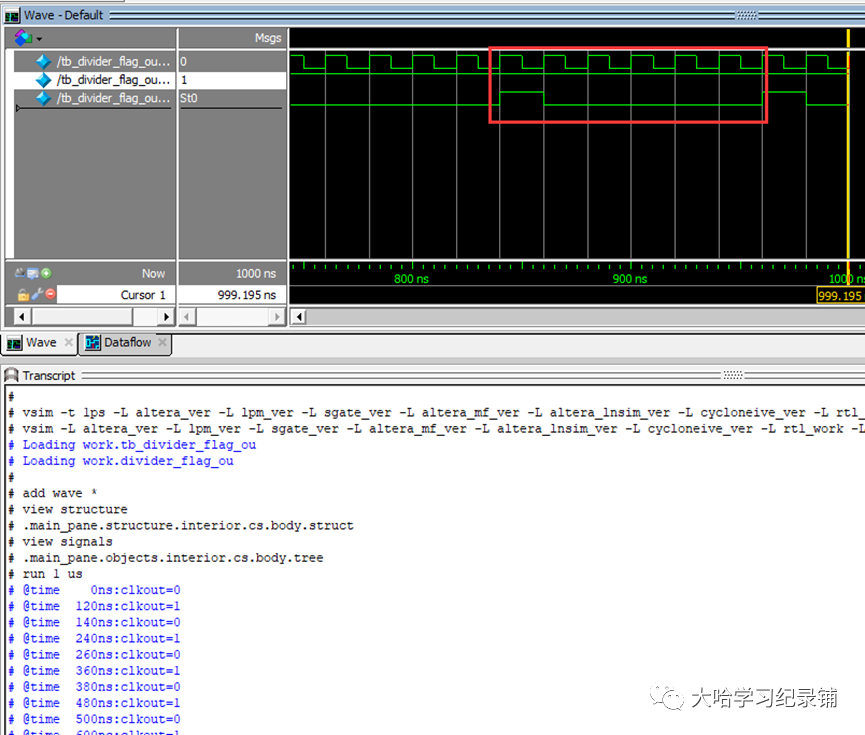

5.1.3仿真圖

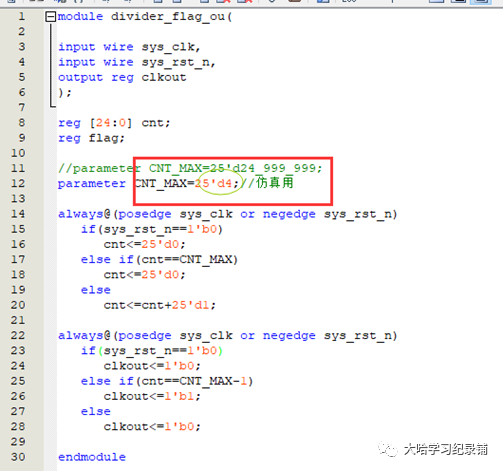

5.2.1源碼

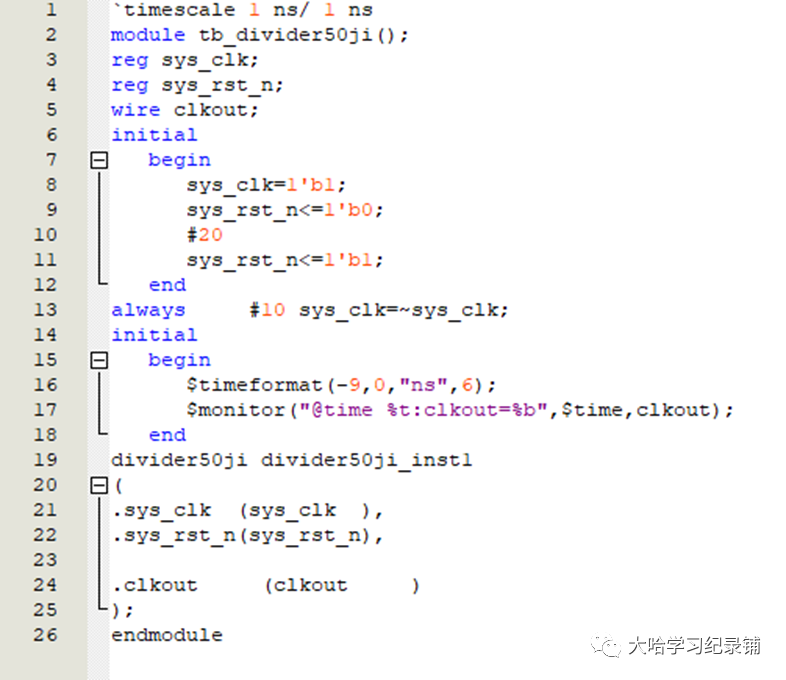

5.2.2測試源碼

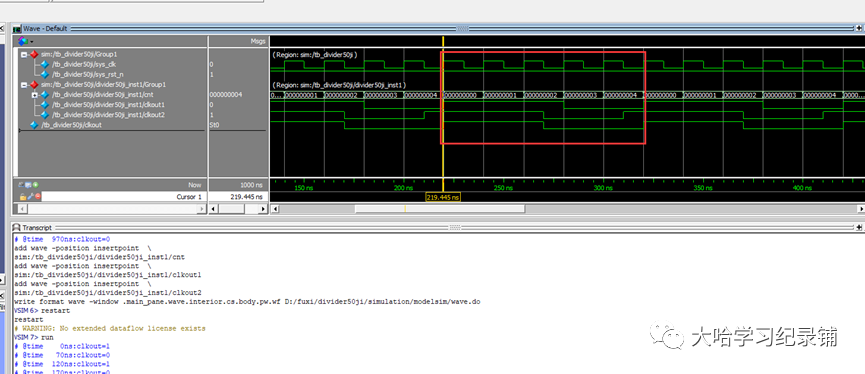

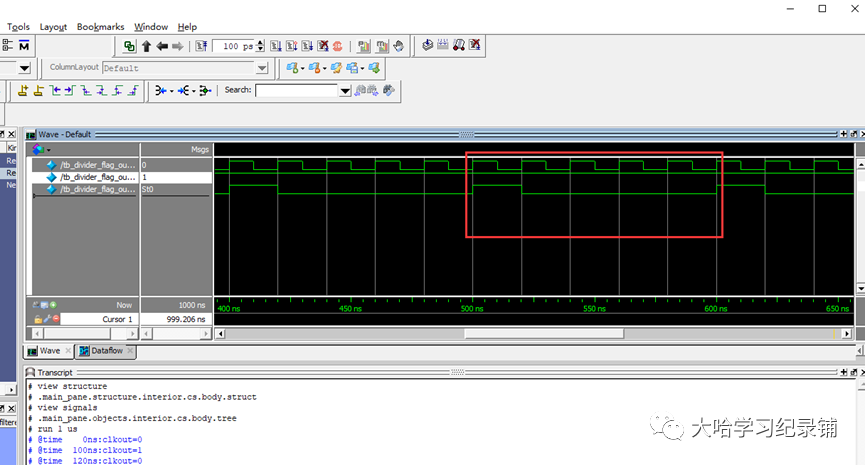

5.2.3仿真圖

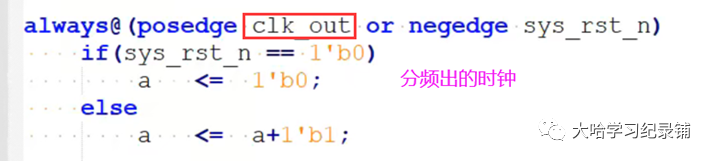

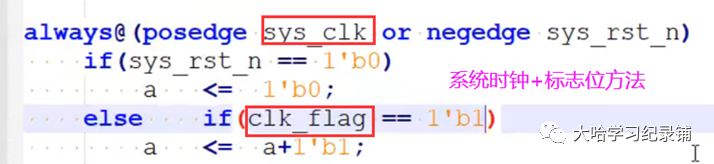

這里為什么要說明這兩種方式呢?

這里就要說到FPGA中的全局時鐘網絡,因為在 FPGA 中凡是時鐘信號都要連接到全局時鐘網絡上,全局時鐘網絡也稱為全局時鐘樹,是 FPGA 廠商專為時鐘路徑而特殊設計的,它能夠使時鐘信號到達每個寄存器的時間都盡可能相同,以保證更低的時鐘偏斜(Skew)和抖動(Jitter)。

然而我們采用第一種方式產生的時鐘clk_out信號并沒有連接到全局時鐘網絡上,這種做法所衍生的潛在問題在低速系統中不易察覺,而在高速系統中就很容易出現問題,但 sys_clk 則是由外部晶振直接通過管腳連接到了 FPGA 的專用時鐘管腳上,自然就會連接到全局時鐘網絡上,所以在 sys_clk 時鐘工作下的信號要比在 clk_out 時鐘工作下的信號更容易在高速系統中保持穩定。所以第二種方式相對來說更加安全。

應用時候:

第一種:

奇分頻

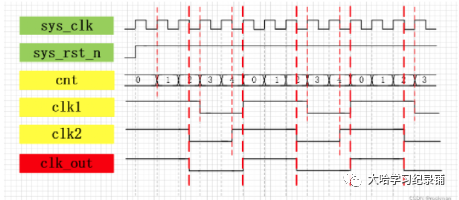

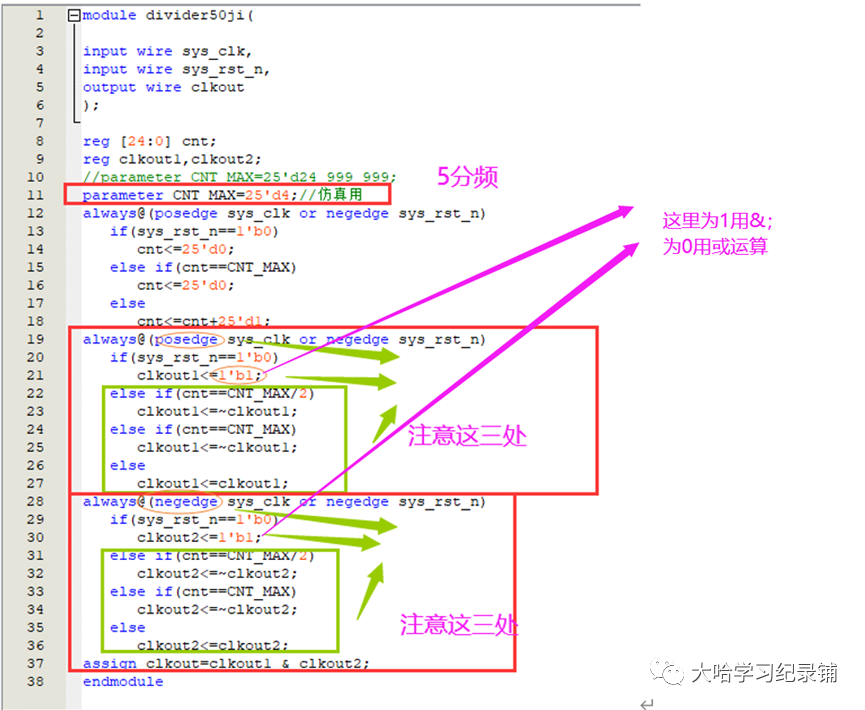

5.3占空比50%實現5分頻方法(即5.1方法)

通過always語句,做一個上升沿的分頻,與一個下降沿的分頻,將分頻后的結果取與運算。例如5分頻:先做一個上升沿觸發的5分頻,三個周期低電平,兩個周期高電平。在做一個下降沿觸發的5分頻,三個周期低電平,兩個周期高電平。最后將兩個分頻后的結果取與運算,就是常規的5分頻。

5.3.1源碼

5.3.2測試源碼

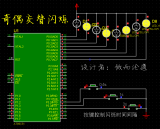

5.3.3仿真圖

5.4標志位方法與5.2一致(不再贅述)在高速系統中,仍采用flag信號的方法進行分頻。

-

FPGA

+關注

關注

1645文章

22015瀏覽量

616846 -

寄存器

+關注

關注

31文章

5432瀏覽量

124008 -

晶振

+關注

關注

35文章

3245瀏覽量

69867 -

仿真器

+關注

關注

14文章

1035瀏覽量

85215 -

CLK

+關注

關注

0文章

127瀏覽量

17578

發布評論請先 登錄

奇數分頻如何得到呢? 解讀奇數分頻和邏輯分析儀(ILA)的使用

請問AD9518 VCO偶數分頻失鎖是什么原因

利用Verilog實現奇數倍分頻

如何利用Verilog實現奇數倍分頻

基于Verilog的FPGA分頻設計

分頻器的作用是什么 半整數分頻器原理圖分析

基于復雜可編程邏輯器件和VHDL語言實現半整數分頻器的設計

PCB多層板為什么都是偶數層?奇數有何風險?

偶數分頻、奇數分頻、半整數分頻和小數分頻詳解

仿真測試3:分頻、奇數、偶數

仿真測試3:分頻、奇數、偶數

評論