編 者 按

前段時(shí)間和幾個(gè)人閑談,看看在FPGA里面實(shí)現(xiàn)一個(gè)Mem加法器怎么玩兒

加法器

看一個(gè)很簡(jiǎn)單的代碼:

val memContext=Array.fill(16*1024)(0) def addOne(index:Int)={ memContext(index)=memContext(index) }

一個(gè)很簡(jiǎn)單的功能。一個(gè)16K大小的數(shù)組。在軟件人眼里這連最初級(jí)的面試題都算不上是吧~

那么我們考慮下在FPGA里面的實(shí)現(xiàn)。數(shù)組位寬如此之大,如果誰(shuí)上來(lái)說(shuō)用寄存器實(shí)現(xiàn)那真的要貽笑大方了~這種情況無(wú)他,只能使用Block Mem來(lái)實(shí)現(xiàn)。

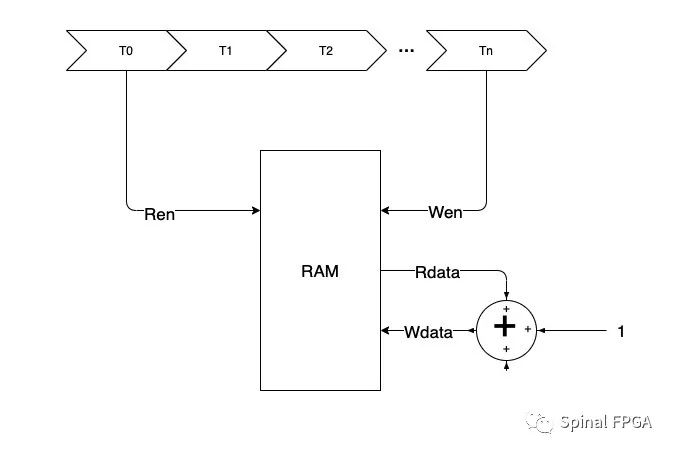

相比于軟件,邏輯設(shè)計(jì)引入了時(shí)序的概念,也就是加上了時(shí)鐘這個(gè)維度。這里是要首先讀出原始的數(shù)據(jù)加1后再寫回回去。而對(duì)于Block Mem,其讀延遲至少有一拍的讀延遲,這里實(shí)現(xiàn)需要先讀后寫,如果要實(shí)現(xiàn)每拍均能處理一個(gè)指令那顯然是需要Mem Write First類型了。

Block Mem

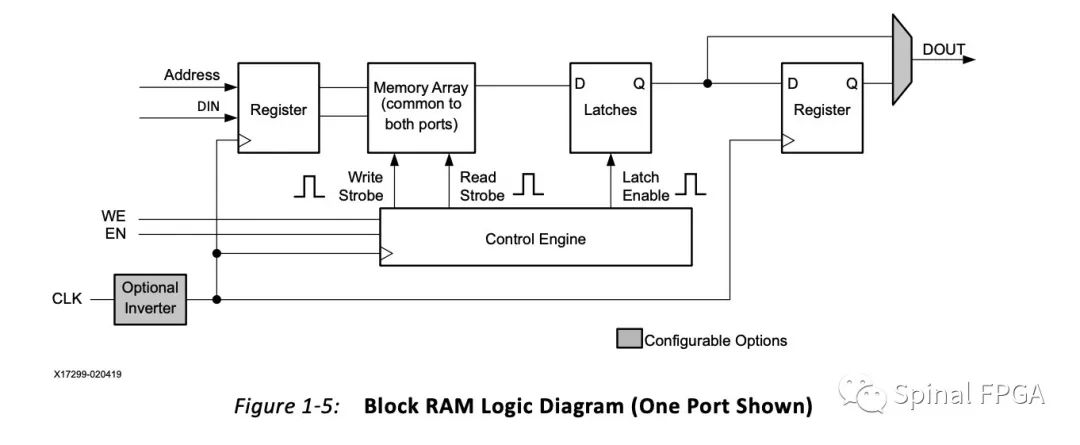

對(duì)于Block Mem,下面是Xilinx中Block Ram的結(jié)構(gòu)圖:

對(duì)于Block RAM,地址線在進(jìn)入到Memory Array之前會(huì)先經(jīng)過(guò)一級(jí)寄存器。Memory Array選擇輸出則會(huì)經(jīng)過(guò)一級(jí)Latch,隨后可通過(guò)選擇器選擇是直接輸出還是再經(jīng)過(guò)一級(jí)寄存器輸出。

對(duì)于Block RAM的使用,如果選擇讀延遲為1 cycle,那么Dout會(huì)通過(guò)Latches輸出,如果讀延遲為2 cycle,那么Dout將會(huì)通過(guò)寄存器輸出。初學(xué)FPGA那會(huì)兒,一般在使用Block RAM時(shí),往往就無(wú)腦的選擇一拍的delay設(shè)計(jì)模式。現(xiàn)在再來(lái)看,在FPGA設(shè)計(jì)里,這種形式往往不利于提升時(shí)鐘頻率。在FPGA設(shè)計(jì)里,如果想要盡可能提高時(shí)鐘頻率,那么對(duì)于Block Ram的使用則需要將Block Ram中Dout前的寄存器給使用起來(lái),即讀延遲需要兩拍的延遲。而再考慮Block RAM的拼接,布局布線的位置,那么可能就需要更高的讀延遲了。

對(duì)于高頻設(shè)計(jì),Memory的Write First的設(shè)計(jì)實(shí)現(xiàn)就需要考慮讀延遲的拍數(shù)了~

假定Read Latency為N,那么上面的例子就相當(dāng)于:

-

FPGA

+關(guān)注

關(guān)注

1643文章

21969瀏覽量

614282 -

Xilinx

+關(guān)注

關(guān)注

73文章

2182瀏覽量

124380 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30614 -

代碼

+關(guān)注

關(guān)注

30文章

4887瀏覽量

70270

原文標(biāo)題:做個(gè)Mem加法器——Mem Write First

文章出處:【微信號(hào):Spinal FPGA,微信公眾號(hào):Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

加法器

加法器,加法器是什么意思

十進(jìn)制加法器,十進(jìn)制加法器工作原理是什么?

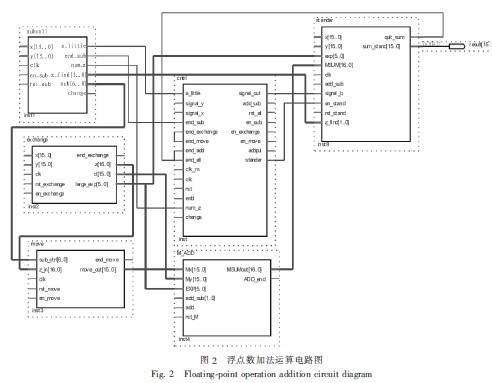

FPU加法器的設(shè)計(jì)與實(shí)現(xiàn)

同相加法器電路原理與同相加法器計(jì)算

加法器是什么?加法器的原理,類型,設(shè)計(jì)詳解

加法器是如何實(shí)現(xiàn)的

超前進(jìn)位加法器是如何實(shí)現(xiàn)記憶的呢

加法器的原理及采用加法器的原因

加法器的原理是什么 加法器有什么作用

基于FPGA實(shí)現(xiàn)Mem加法器

基于FPGA實(shí)現(xiàn)Mem加法器

評(píng)論