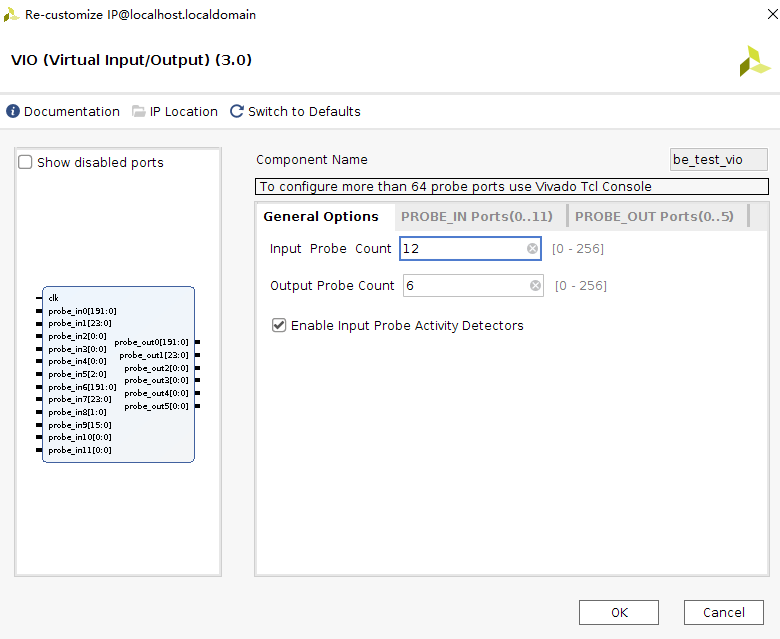

在Vivado中,VIO(Virtual Input/Output)是一種用于調(diào)試和測試FPGA設(shè)計的IP核,它允許設(shè)計者通過JTAG接口實時讀取和寫入FPGA內(nèi)部的寄存器,從而檢查設(shè)計的運行狀態(tài)并修改其行為。VIO IP核提供了一個簡單易用的接口,使得用戶可以輕松地與FPGA內(nèi)部寄存器進(jìn)行交互。

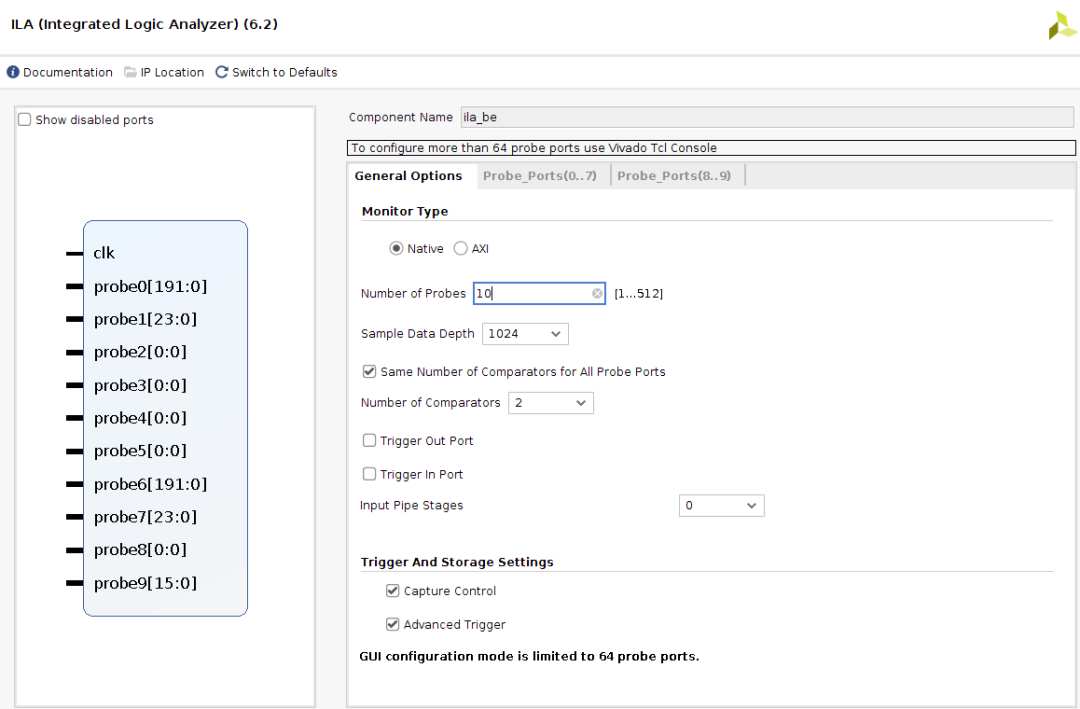

在Vivado中,ILA(Integrated Logic Analyzer)是一種強(qiáng)大的在系統(tǒng)調(diào)試工具,它可以捕獲并分析FPGA內(nèi)部的信號。使用ILA時,需要確保ILA的時鐘信號與被觀察信號的時鐘域一致,以避免由于時鐘域不匹配導(dǎo)致的數(shù)據(jù)捕獲錯誤。此外,ILA的探針數(shù)量和數(shù)據(jù)深度應(yīng)根據(jù)實際需求進(jìn)行配置,以平衡資源消耗和調(diào)試需求。

VIO與ILA基本上就是我們在板調(diào)試FPGA的主要工具,在vivado中均有相應(yīng)的IP core,具體的步驟如下:

1. vivado中打開IP Catalog

2. 搜索ila,在Debug&Verification 中選擇ILA(Inegrated Logic Analyzer)

3. 右鍵Customize IP ,設(shè)置參數(shù),多數(shù)的選擇可以采用默認(rèn)的選擇。

這里對ILA的特殊參數(shù)做一點說明:

Capture Control:即可以選擇一個條件信號,僅條件信號滿足設(shè)置要求時,才會進(jìn)行采樣或者觸發(fā)操作,用于我們在需要某些信號進(jìn)行觸發(fā)時勾選;

Advanced Trigger:支持高級觸發(fā)功能,它允許用戶通過編寫觸發(fā)狀態(tài)機(jī)(Trigger State Machine,TSM)來定義更復(fù)雜的觸發(fā)條件。TSM是一個簡單的腳本語言,用于定義觸發(fā)狀態(tài)機(jī)。可以在ILA的屬性窗口中編寫TSM代碼,或者創(chuàng)建一個后綴為.tsm的文件來編寫TSM腳本,實現(xiàn)相應(yīng)的觸發(fā)設(shè)置,可以利用ILA的高級觸發(fā)功能來更精確地捕獲和分析FPGA設(shè)計中的信號。

Setup Debug:由于這種Debug方式是將Debug信息寫入XDC文件的方式,vivado提示我們需要更新XDC文件,可以選擇覆蓋overwite現(xiàn)有的XDC文件,該選項并不會刪除我們現(xiàn)有的XDC文件約束,而是將Debug信息添加在XDC約束后面,實際操作中會發(fā)現(xiàn),并不是完全將新的ILA約束信息,添加在原有XDC文件之后,而是以vivado自己的方式,重新寫我們的約束文件,即如果我們有重要的約束信息,建議新增XDC文件save constraints as,這樣可以保障原有XDC信息不被修改。

ILA其他注意事項

(1)ILA核的采樣深度不宜過大,采樣深度盡量設(shè)置在1024bit以內(nèi):在每個采樣時鐘下,ILA都會將捕獲到的探針信號的值送入RAM中,由于RAM的存儲空間是有限的,其數(shù)值越大,消耗的RAM資源也越多,從而對設(shè)計性能產(chǎn)生不利影響。

(2)ILA核的采樣寬度不宜過大,隨探針寬度增加,對資源利用率和時序的影響也會增大。

(3)請確保輸入到ILA核的時鐘與抓取的信號是同步關(guān)系,否則在設(shè)計編程到器件中時會產(chǎn)生時序問題并導(dǎo)致通信失敗。

(4)抓信號的時鐘必須為全局時鐘網(wǎng)絡(luò)。

(5)請盡量確保ILA核選擇的時鐘均為自由運行的時鐘(常開穩(wěn)定時鐘),否則可能造成在器件上加載版本時無法與調(diào)試核通信。

(6)請盡量確保FPGA JTAG時鐘比Debug Hub時鐘慢2.5倍,否則可能出現(xiàn)運行后報錯或者運行后不報錯但不顯示任何結(jié)果的情況,ug908。

VIO的配置界面中,設(shè)置Input Probe Count和Output Probe Count,即輸入和輸出探頭的數(shù)量。

Enable Input Probe Activity Detectors:當(dāng)輸入信號發(fā)生變化時,Vivado會顯示一個活動指示,幫助追蹤信號的變化。啟用Input Probe Activity Detectors后,你可以在ILA調(diào)試波形中看到哪些信號是活動的,這有助于快速定位問題。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615443 -

寄存器

+關(guān)注

關(guān)注

31文章

5427瀏覽量

123727 -

調(diào)試工具

+關(guān)注

關(guān)注

1文章

52瀏覽量

12794 -

Vivado

+關(guān)注

關(guān)注

19文章

834瀏覽量

68375

原文標(biāo)題:FPGA上板調(diào)試方式總結(jié)----VIO/ILA

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA遠(yuǎn)程燒寫bit文件和調(diào)試ILA指南

XILINX FPGA Debug with VIO and TCL

玩轉(zhuǎn)Zynq連載5——基于Vivado的在線板級調(diào)試概述

chipcope pro核心生成并在設(shè)計中使用它們

Chipscope中的ILA,VIO和ATC2有什么區(qū)別?

關(guān)于ILA核心使用的一些事情?

Arty是否有可能不支持ILA調(diào)試?

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA

Vivado調(diào)試ILA debug結(jié)果也許不對

Vivado之ILA詳解

ILA工作原理 ILA使用方法與注意

Vivado之VIO原理及應(yīng)用

FPGA調(diào)試方式之VIO/ILA的使用

FPGA調(diào)試方式之VIO/ILA的使用

評論