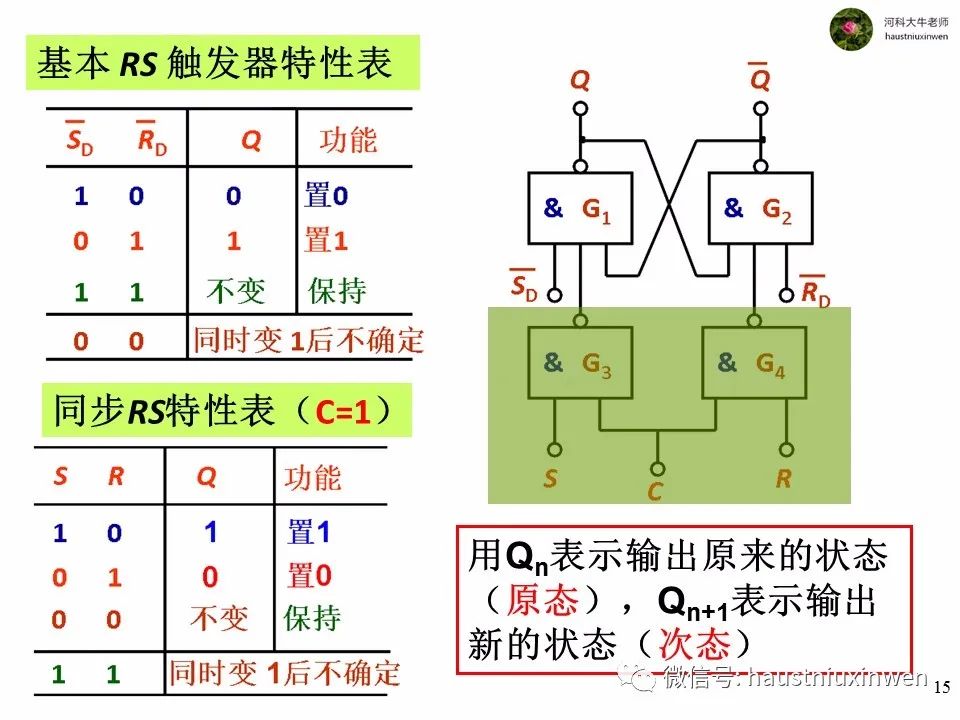

時(shí)序邏輯電路與組合邏輯電路的區(qū)別在于,時(shí)序邏輯電路的輸出并不僅僅由輸入條件決定,還由輸出的前一個(gè)狀態(tài)有關(guān)。也就是說,當(dāng)輸入改變時(shí),不能唯一確定輸出是什么,還要看輸入改變前輸出是什么狀態(tài),一起決定后面的輸出狀態(tài)。簡而言之,這是一個(gè)有反饋的電路。

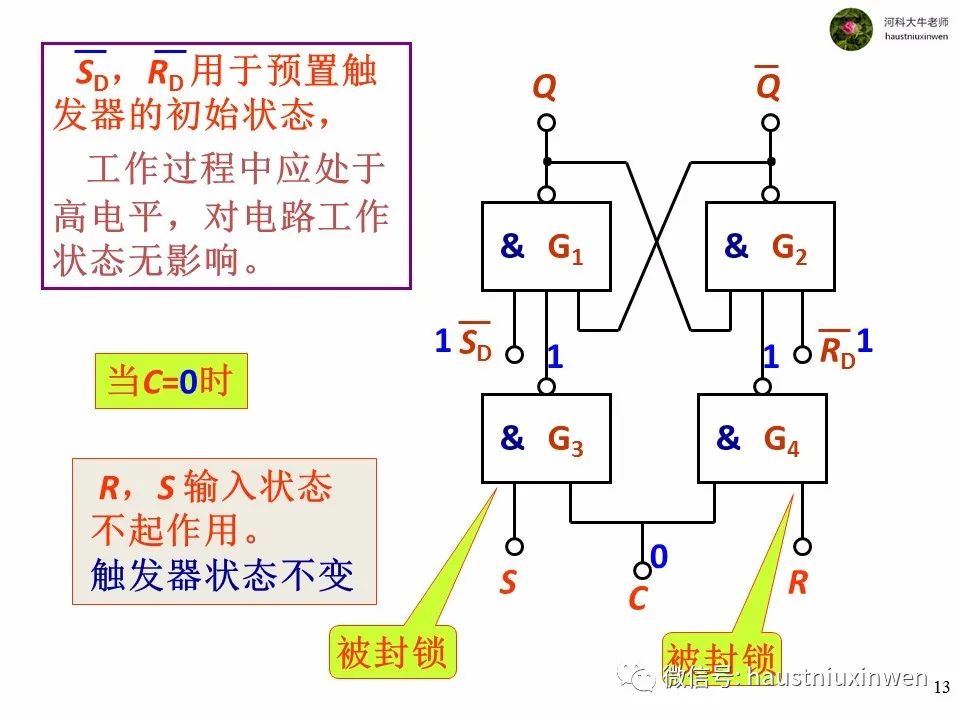

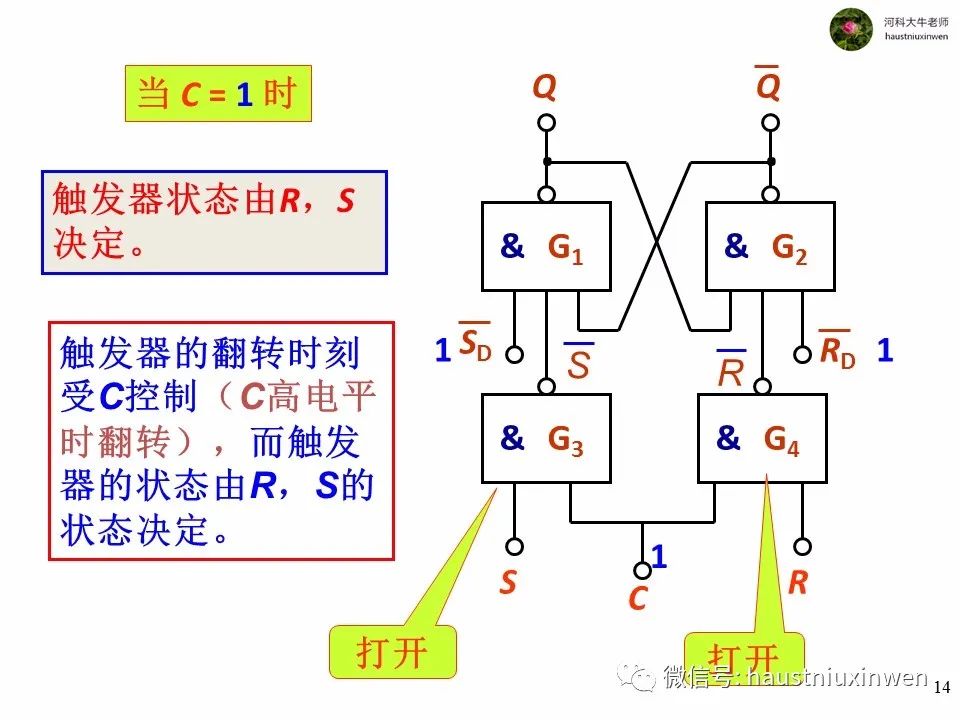

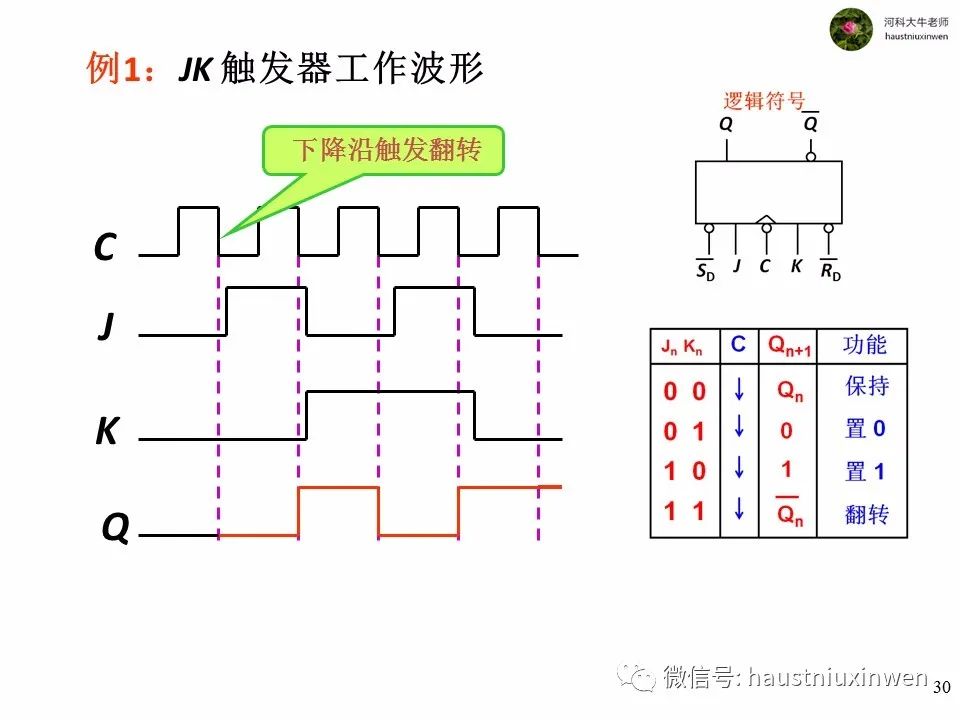

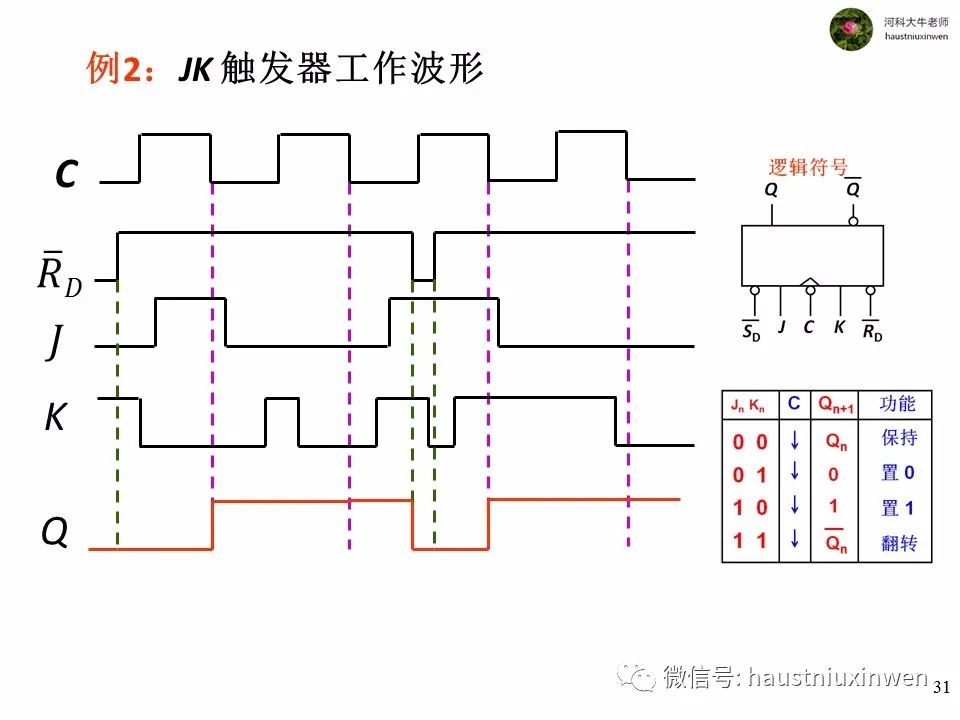

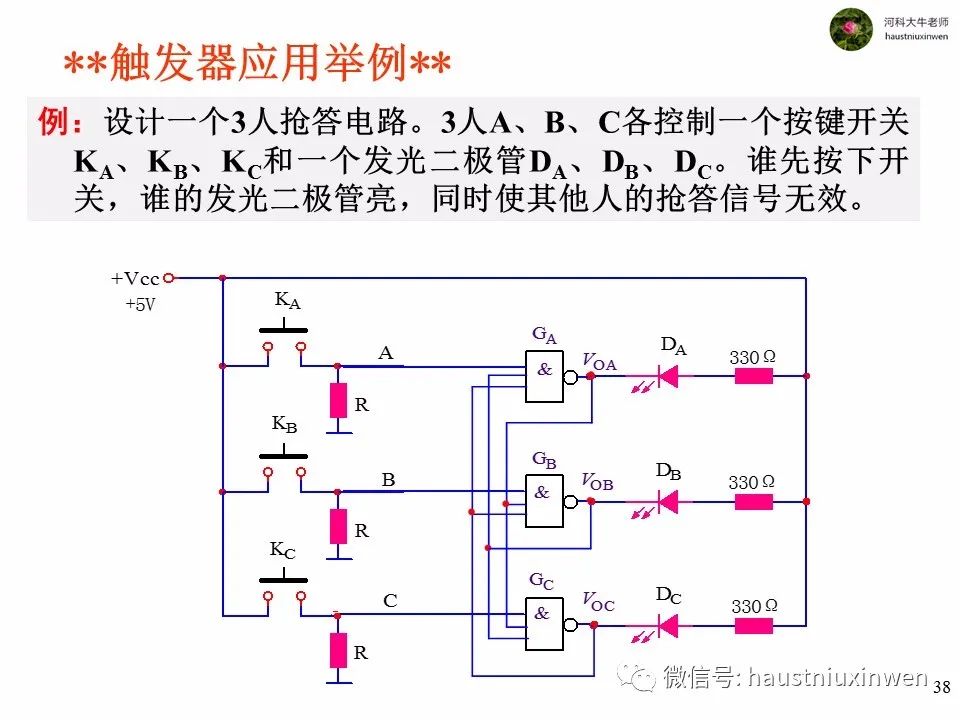

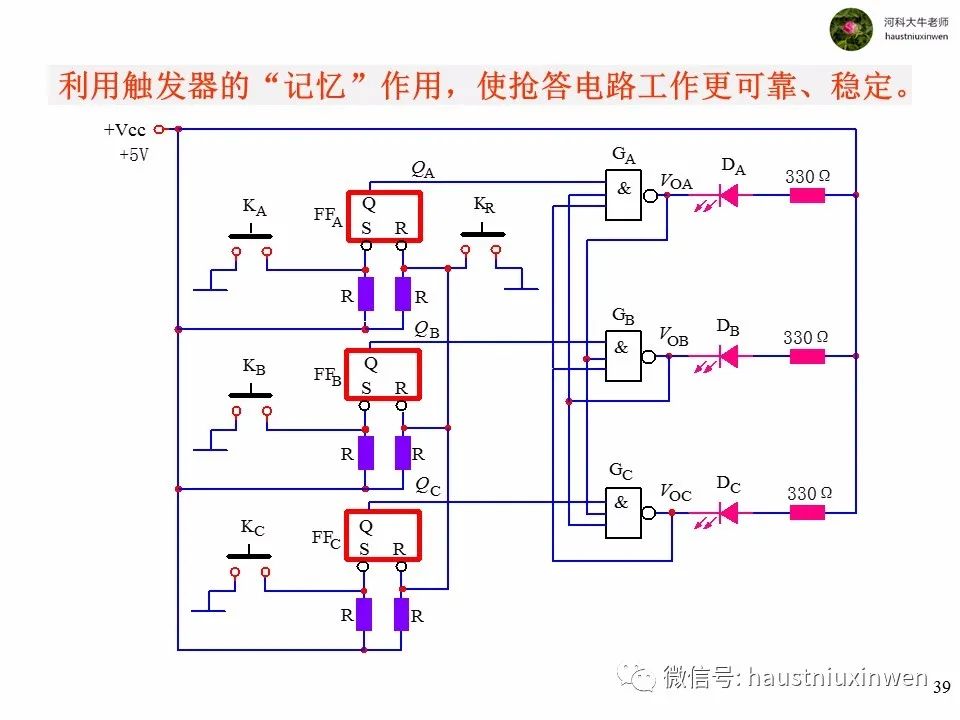

與模擬電路中的反饋不同的是,反饋不是隨時(shí)隨地進(jìn)行的,而是有節(jié)奏的,當(dāng)有效觸發(fā)信號(hào)來臨,才能進(jìn)行控制輸出的作用。觸發(fā)信號(hào)不來,輸入信號(hào)即便有變化,也不能改變輸出。這種動(dòng)作機(jī)制可以保證邏輯電路的多個(gè)輸入信號(hào)動(dòng)作完成后才去實(shí)現(xiàn)邏輯功能,即減少誤動(dòng)作,增加可靠性。

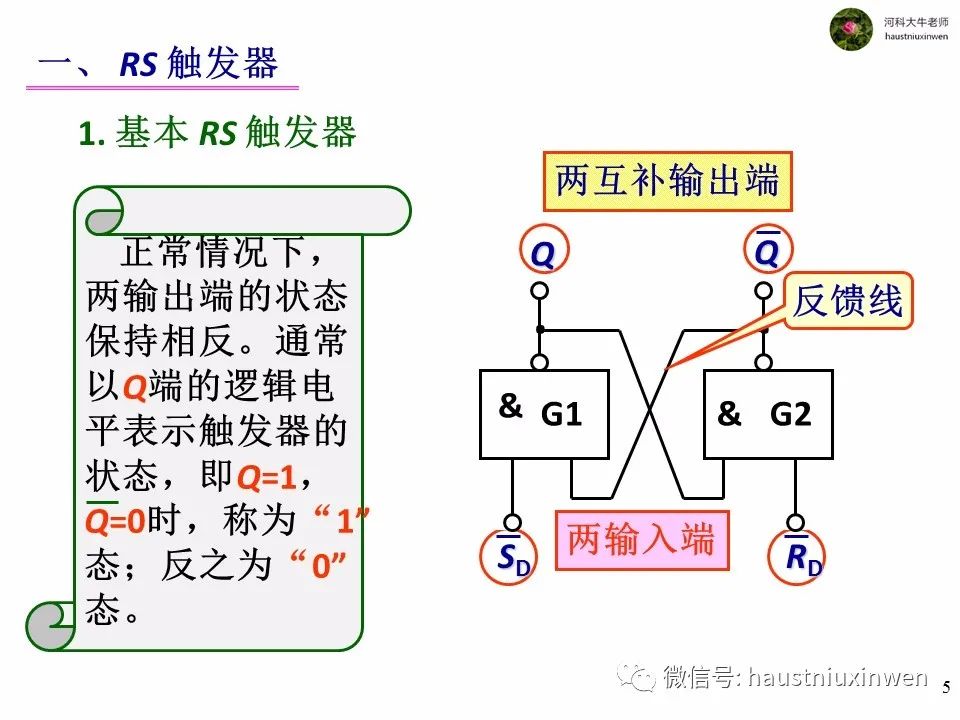

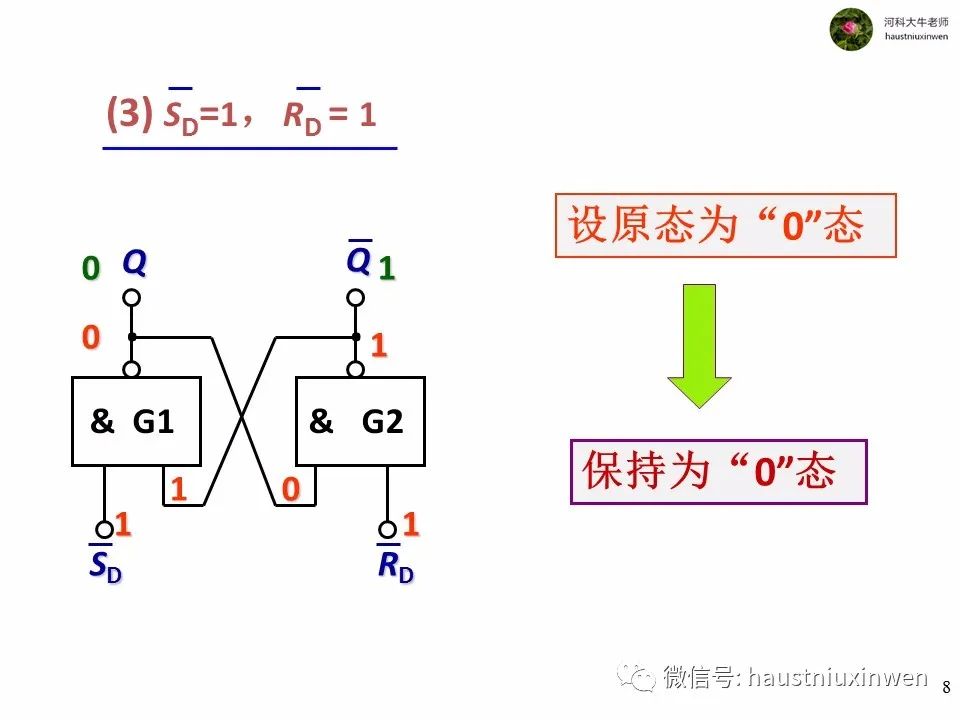

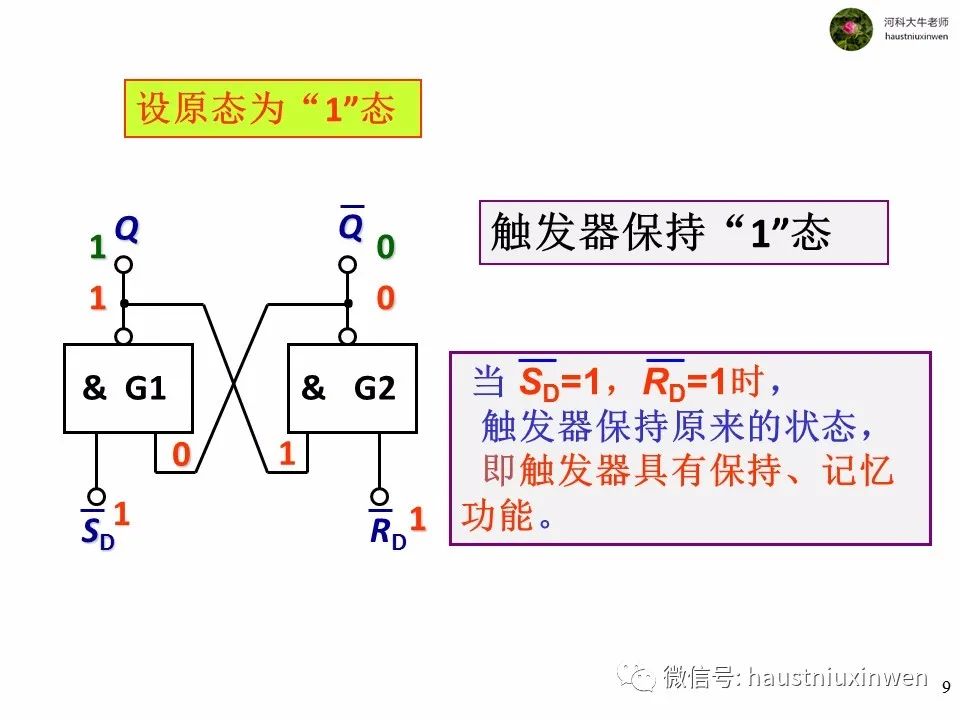

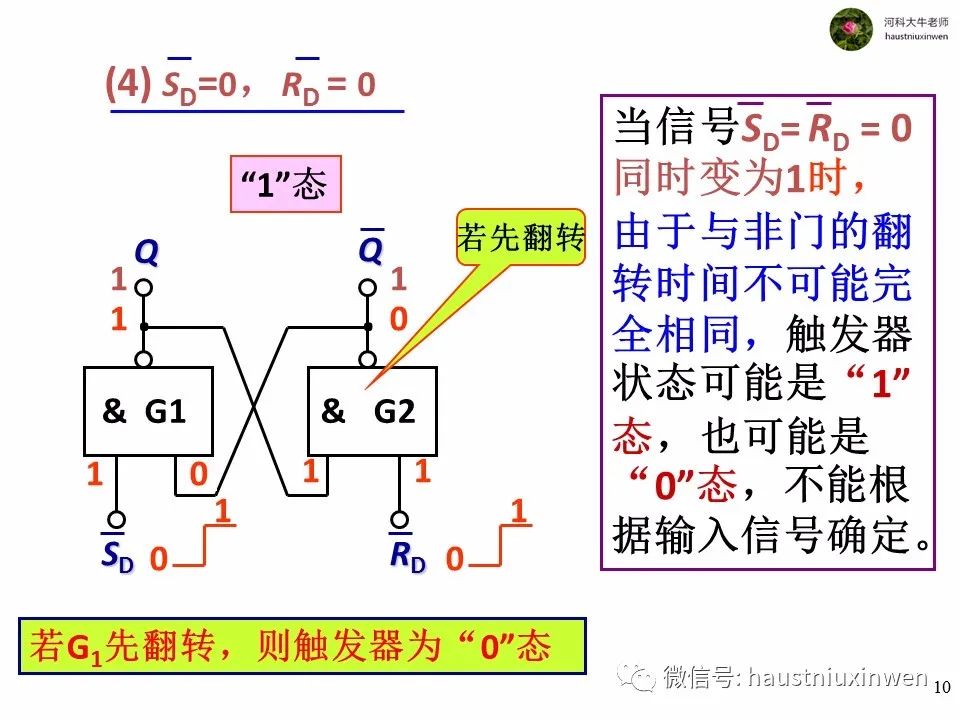

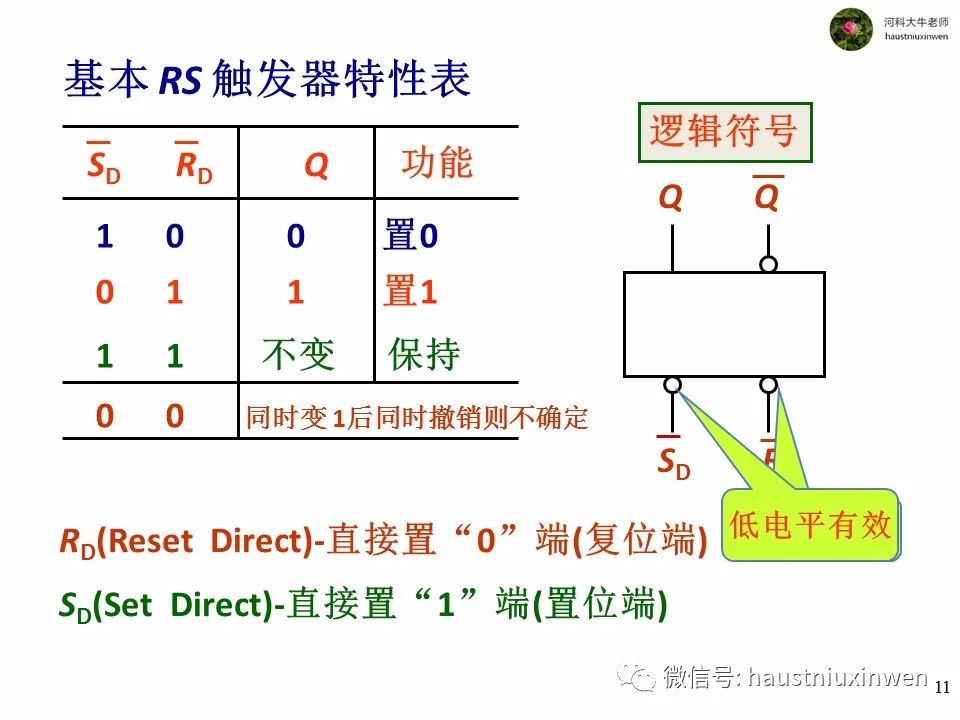

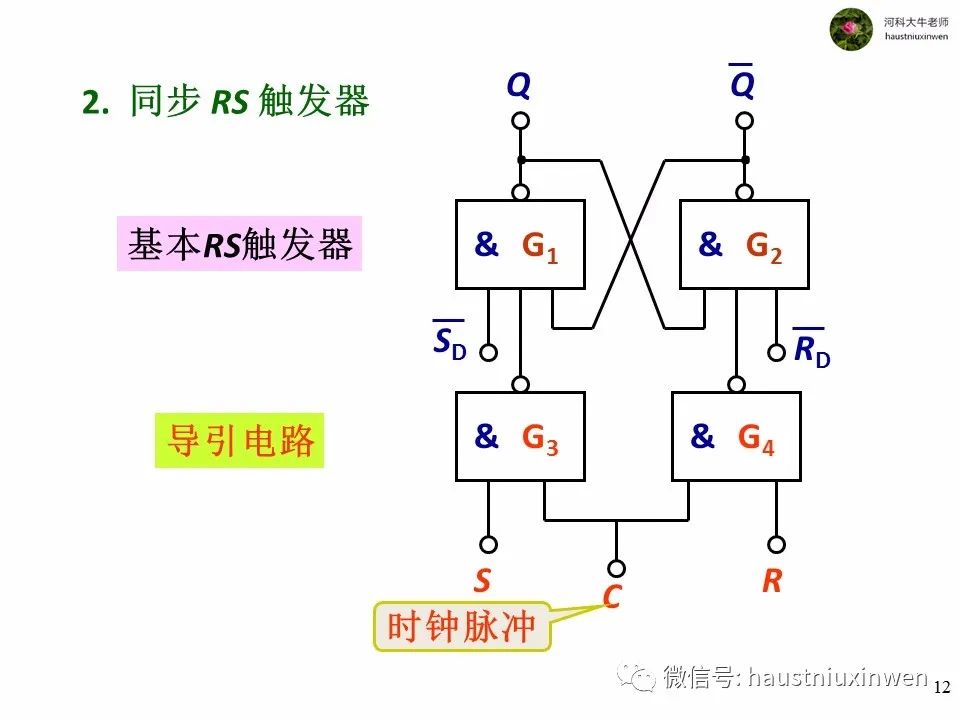

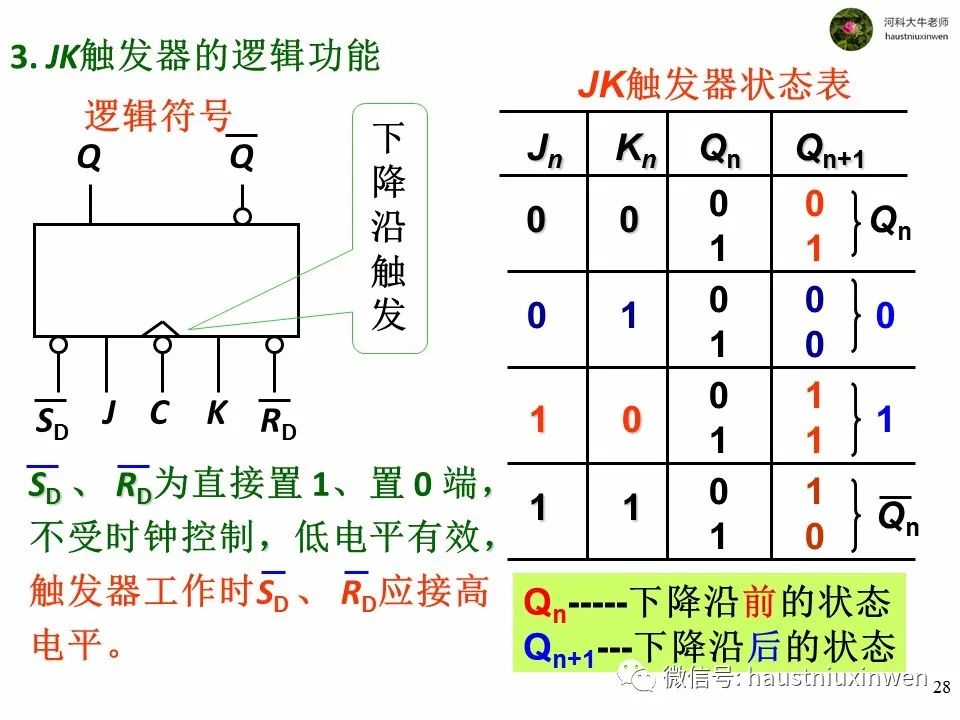

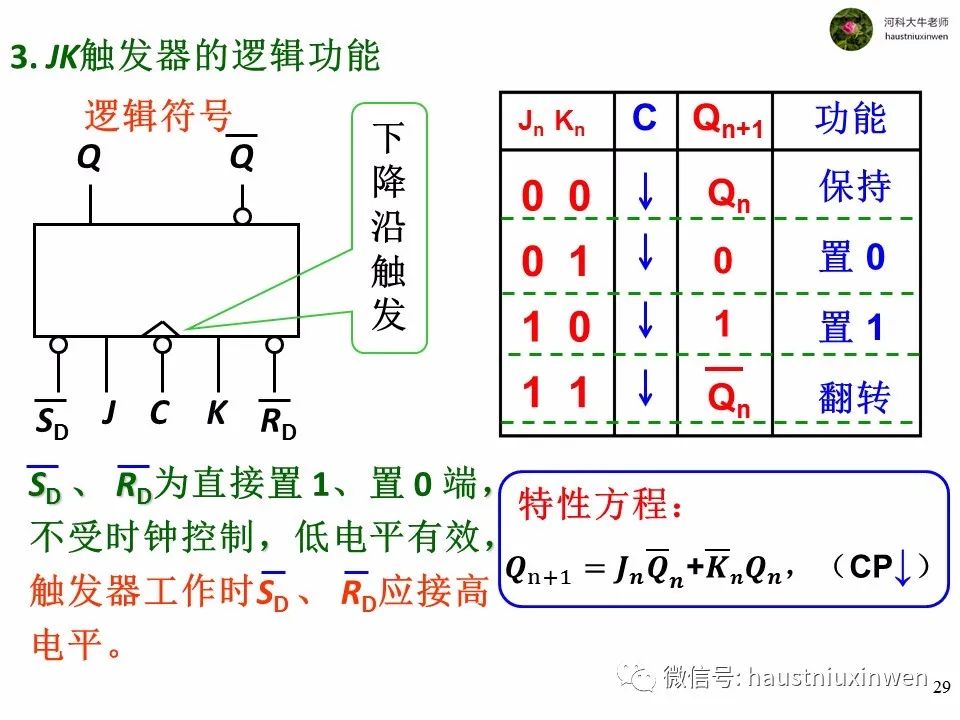

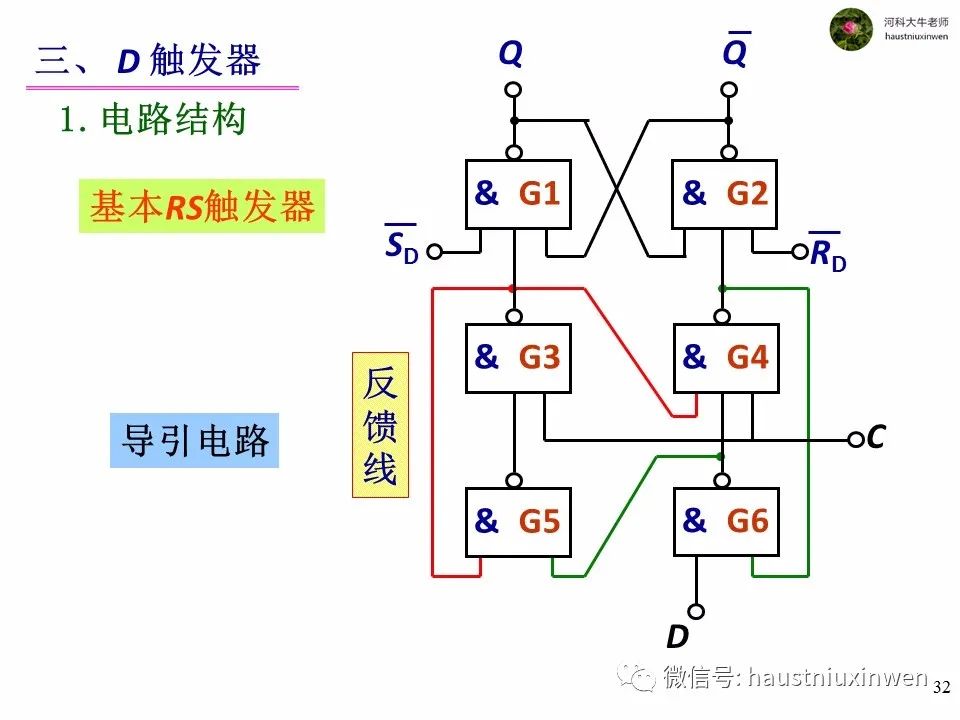

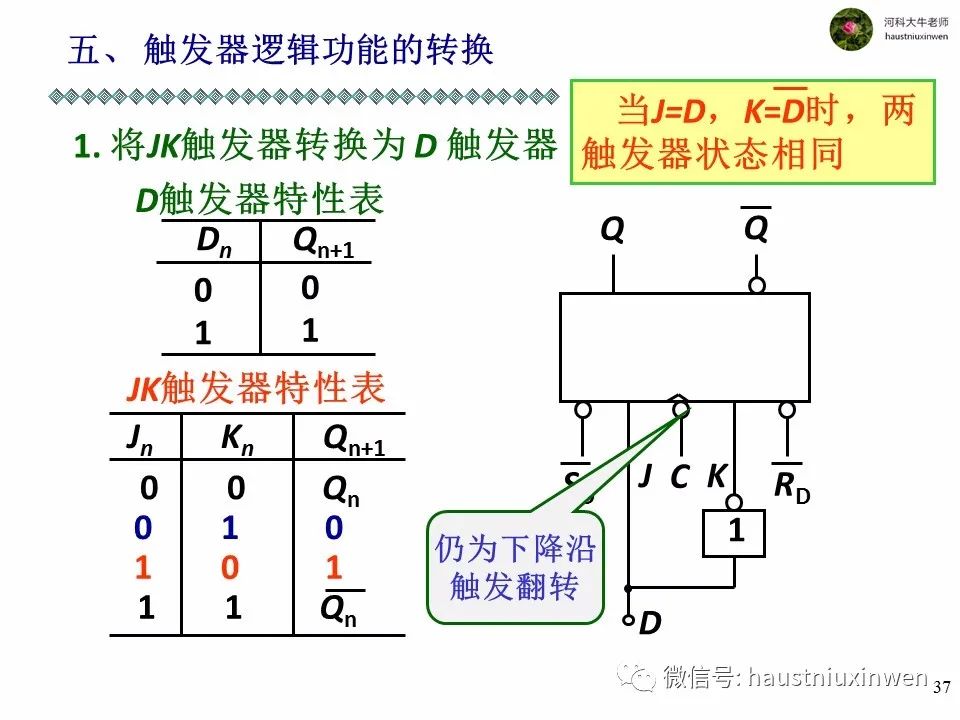

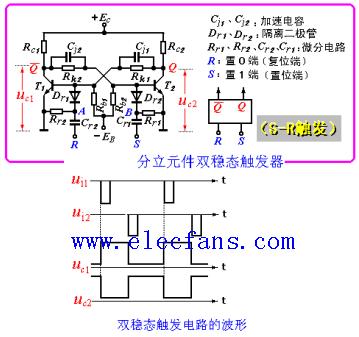

組合邏輯電路的基本單元是門電路,而時(shí)序邏輯電路的基礎(chǔ)單元是雙穩(wěn)態(tài)觸發(fā)器。

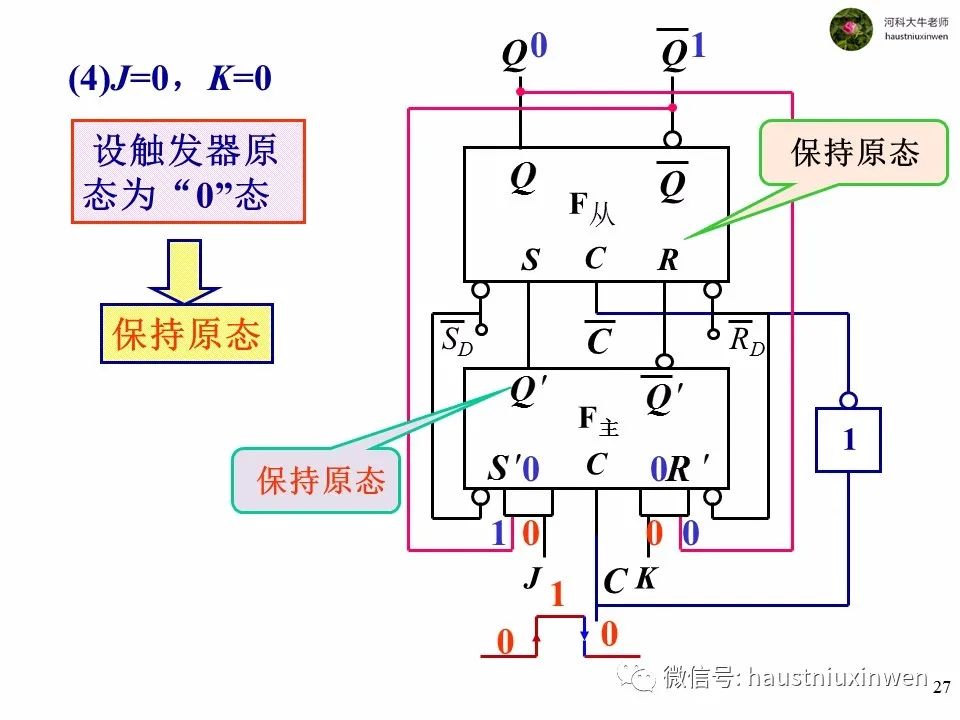

穩(wěn)態(tài)是指在沒有有效觸發(fā)信號(hào)時(shí),輸出端的狀態(tài)始終保持不變。

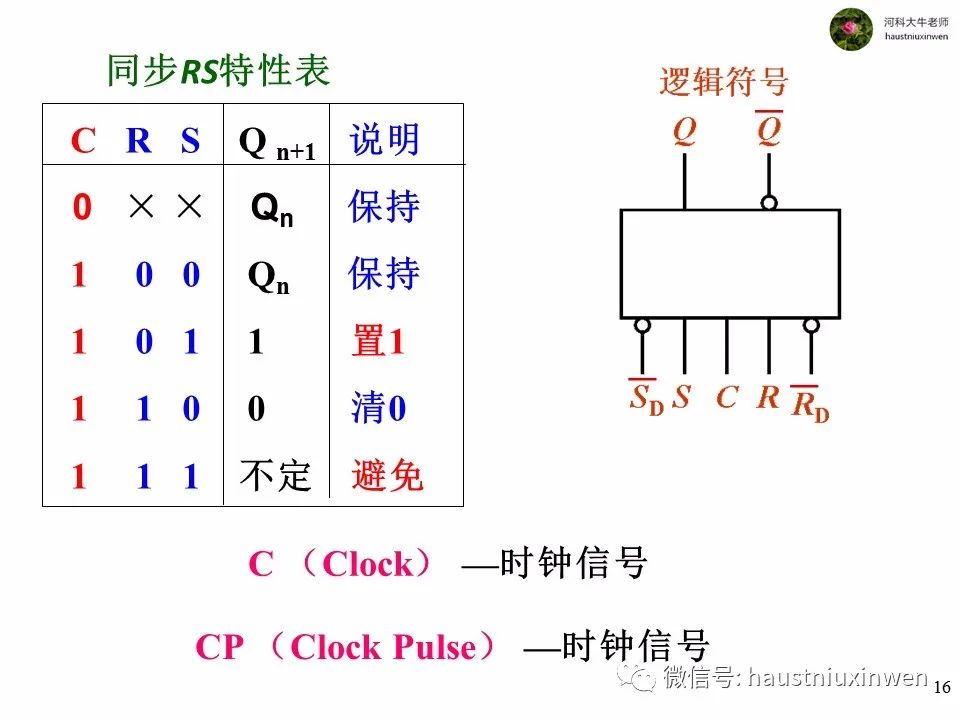

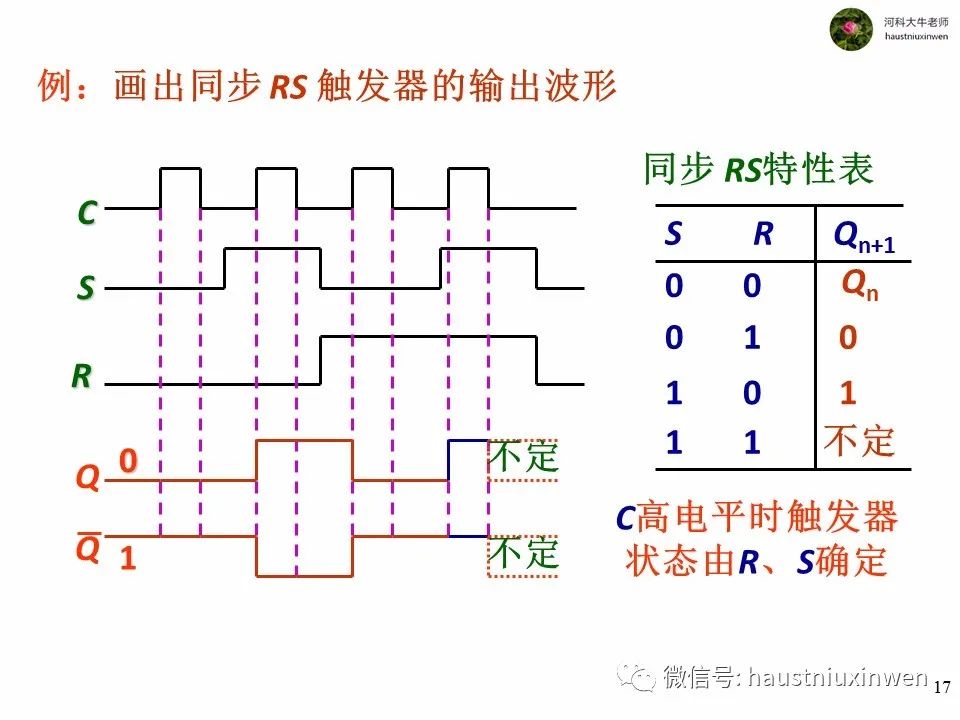

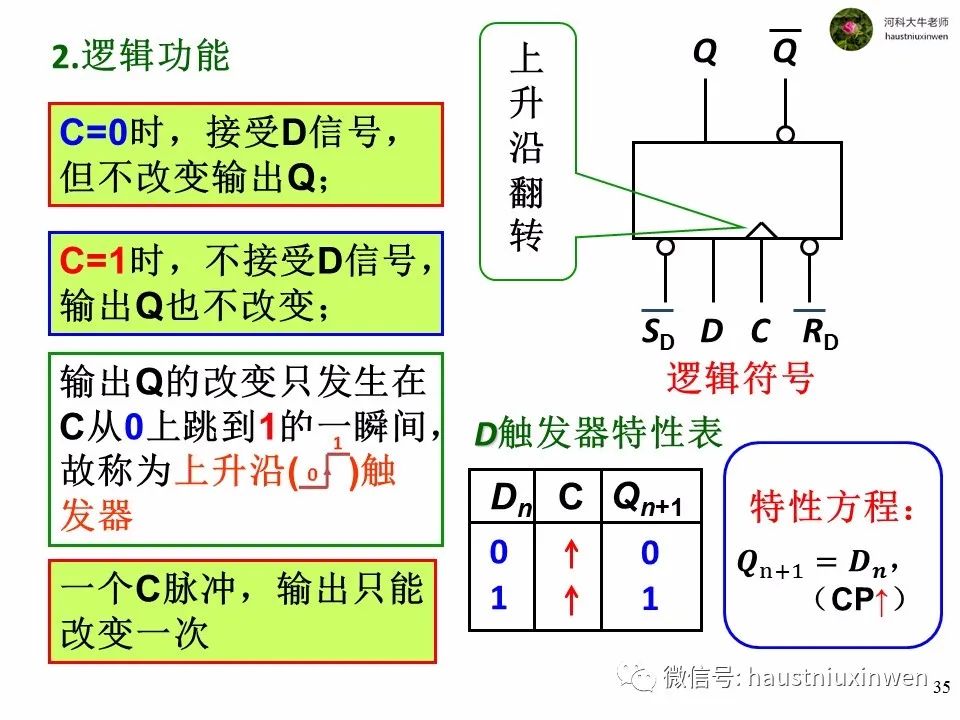

而觸發(fā)信號(hào)有電平觸發(fā)和邊沿觸發(fā)兩種。

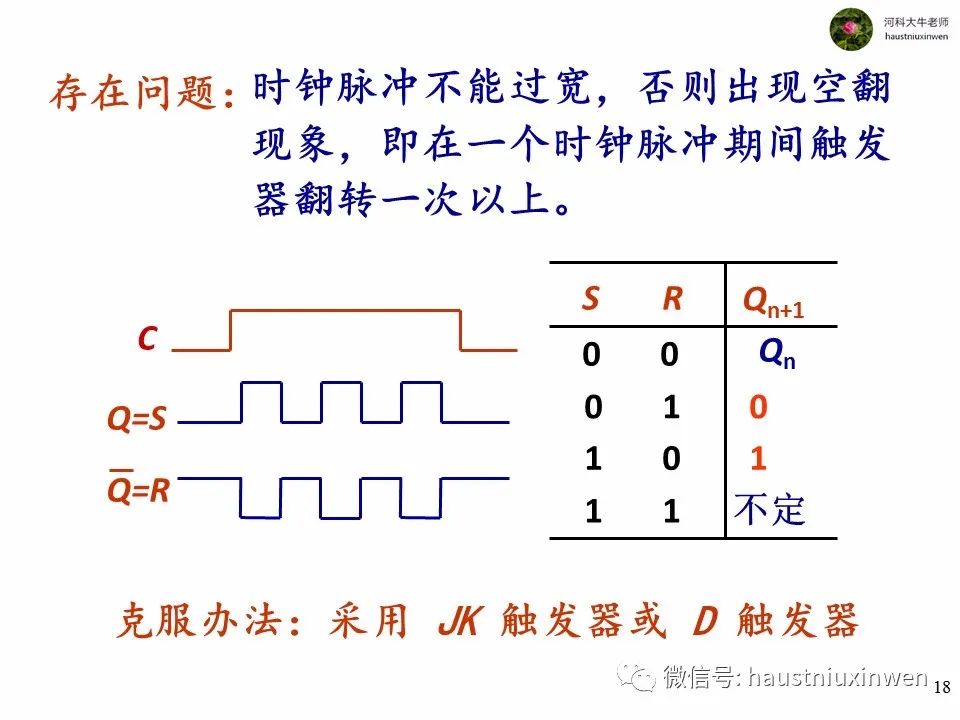

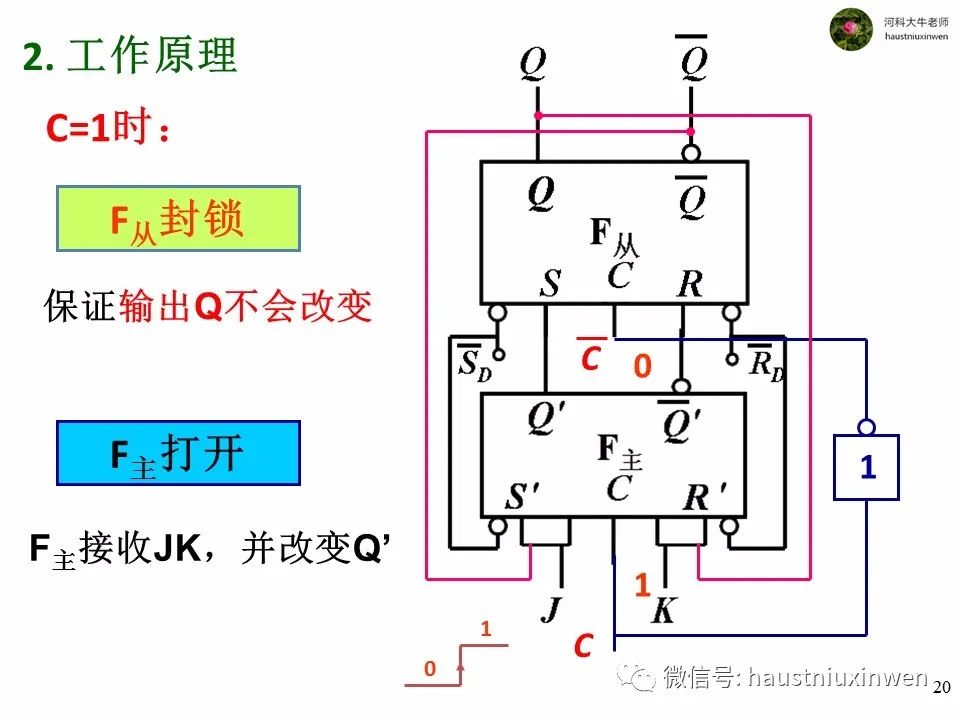

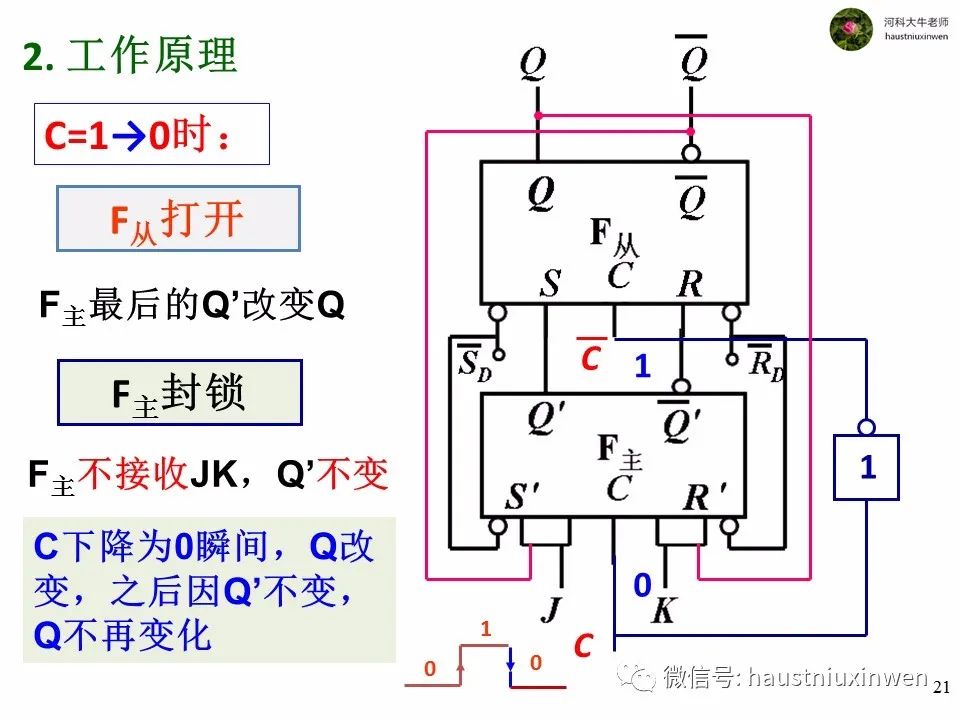

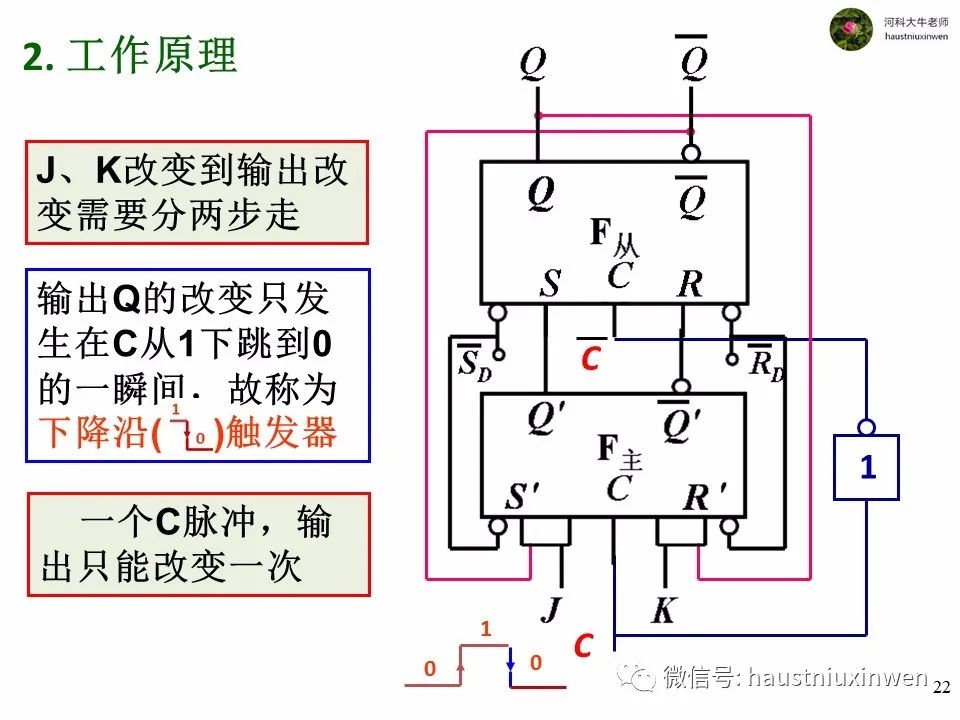

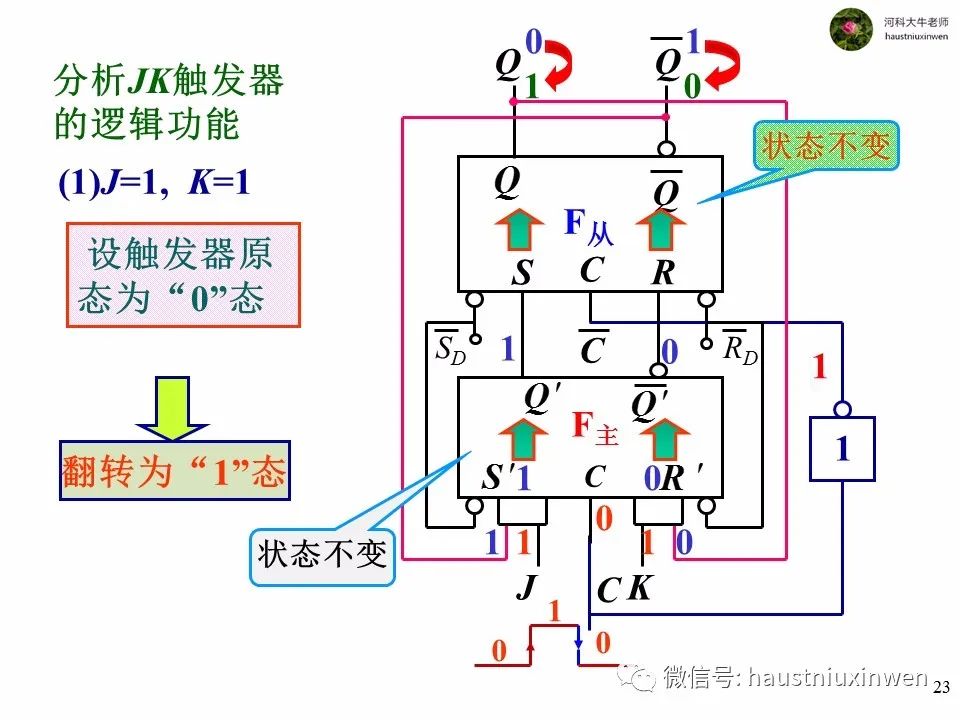

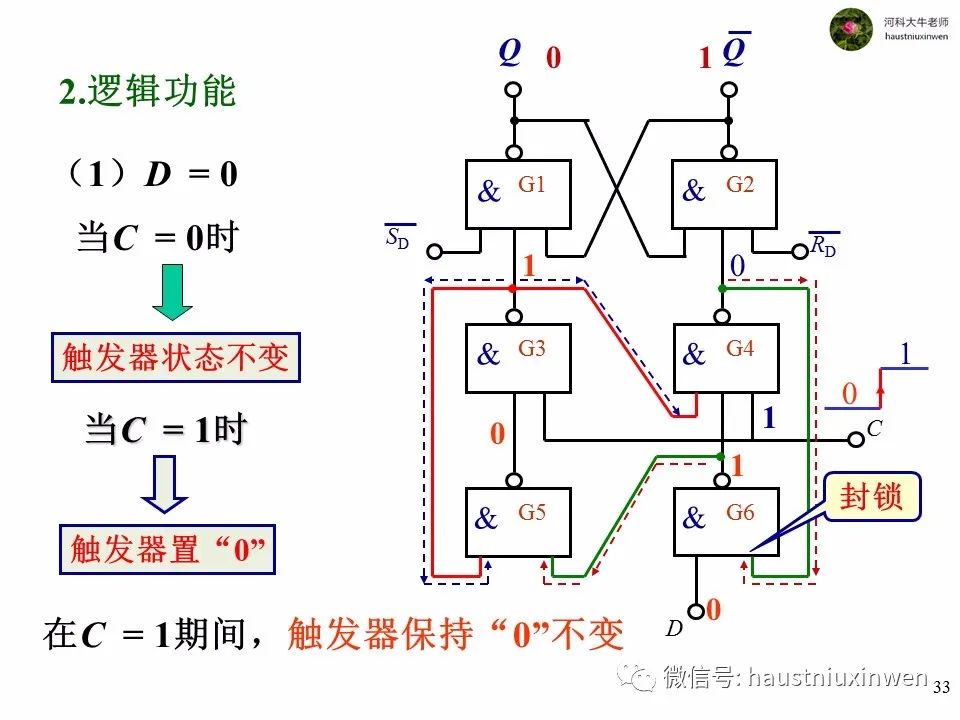

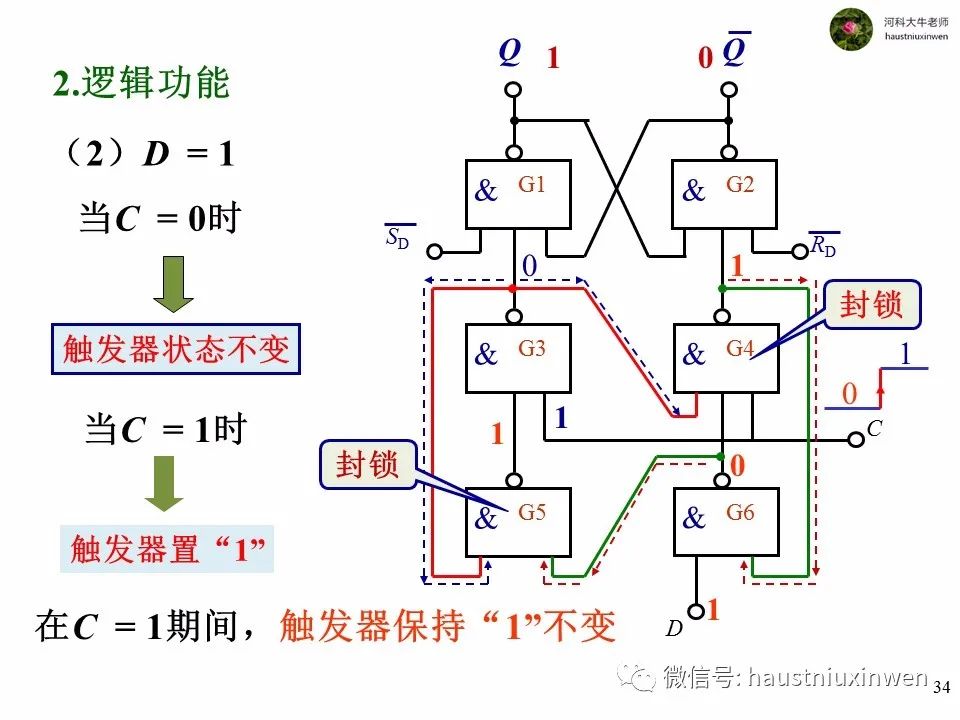

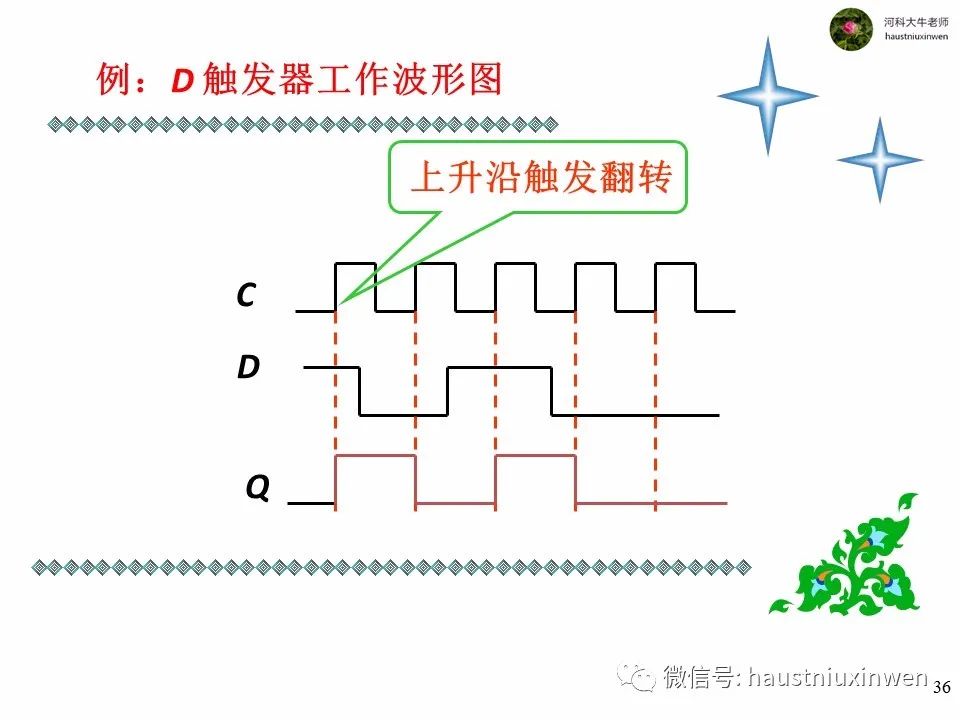

電平觸發(fā)是指當(dāng)時(shí)鐘信號(hào)為高電平時(shí),允許輸出根據(jù)輸入和原狀態(tài)改變。邊沿觸發(fā)是指當(dāng)時(shí)鐘信號(hào)由0變1或者由1變0時(shí),輸出才能根據(jù)輸入和原狀態(tài)改變。

電平觸發(fā)在需要多個(gè)信號(hào)都滿足時(shí)才執(zhí)行功能的情況下經(jīng)常使用,以避免因多路信號(hào)反應(yīng)時(shí)間不一致造成的誤操作。

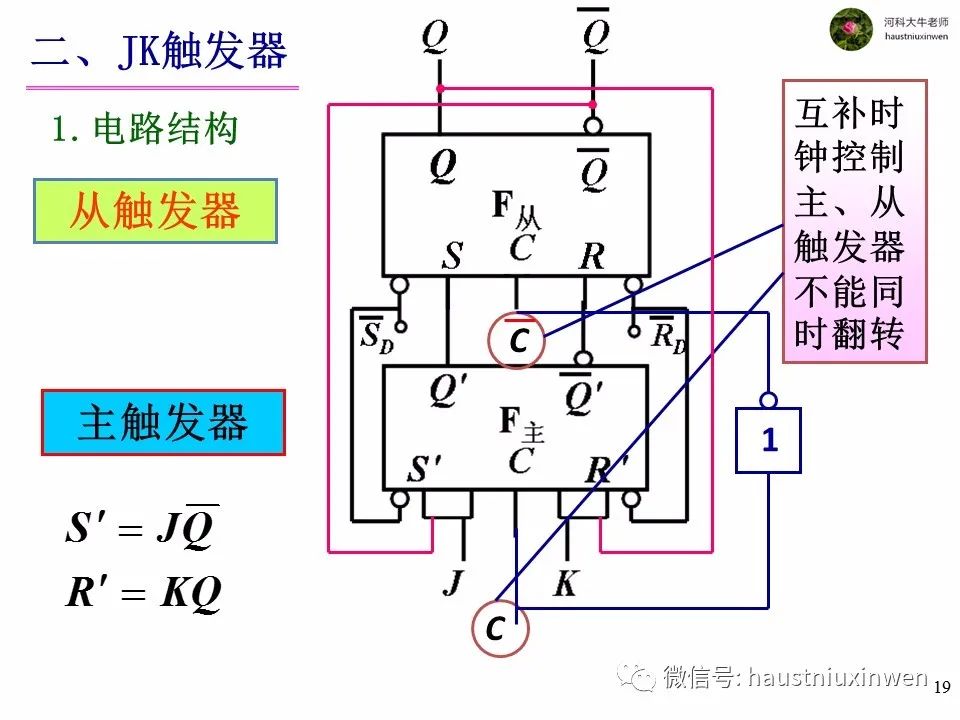

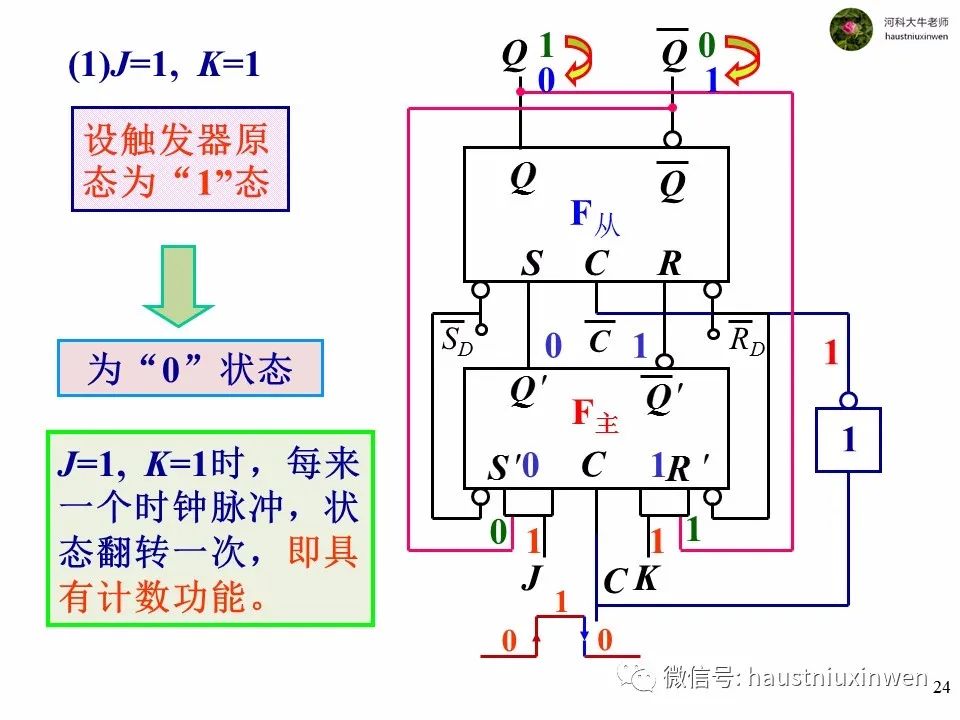

邊沿觸發(fā)可以實(shí)現(xiàn)一個(gè)觸發(fā)脈沖信號(hào)觸發(fā)器只動(dòng)作一次的功能,避免空翻失控。

-

模擬電路

+關(guān)注

關(guān)注

125文章

1591瀏覽量

103845 -

門電路

+關(guān)注

關(guān)注

7文章

200瀏覽量

40714 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2039瀏覽量

62050 -

時(shí)序邏輯電路

+關(guān)注

關(guān)注

2文章

94瀏覽量

16835 -

脈沖信號(hào)

+關(guān)注

關(guān)注

6文章

402瀏覽量

37601

發(fā)布評論請先 登錄

什么是雙穩(wěn)態(tài)觸發(fā)器?

數(shù)字電路--觸發(fā)器雙穩(wěn)態(tài)觸發(fā)器

雙穩(wěn)態(tài)觸發(fā)器的工作原理詳解

雙穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)

雙穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)

評論