100G光口測試采用C50測試儀和Xilinx的VCU118開發板測試,經過測試發現,Xilinx自帶的100G IP核仍然無法跑到滿速,跟10G一樣,也是只跑到99%的負載率。另外,工具的版本和License的申請都需要特別留意。歡迎感興趣的同學們留言討論。

一、軟硬件環境、IP核及對應License

1、軟硬件環境

軟件環境為VIVADO2019.1,不建議采用VIVADO 2018.2,原因在于2018.2中的該IP核沒有AXI總線,只有LBUS總線,LBUS總線使用起來需要進行總線的聚合與分拆(數據總線分為4路,每路位寬為128bit),較為繁瑣,所以建議使用2019.1中的AXI總線的IP核。

硬件環境為采用TestCenter C50測試儀的100G光口連接VCU118開發板上的100G光口進行測試。

連接圖(必須用100G專用光纖)

VCU118開發板

C50網絡分析儀(兩個100G光口、4個五速光口(40G、20G和十百千)、16個十百千自適應電口)

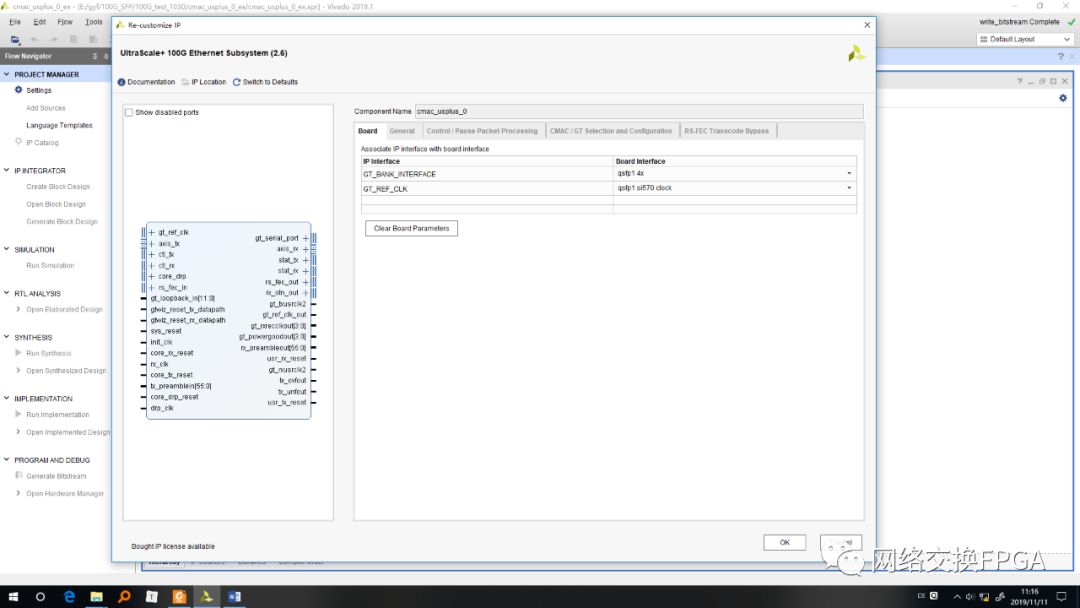

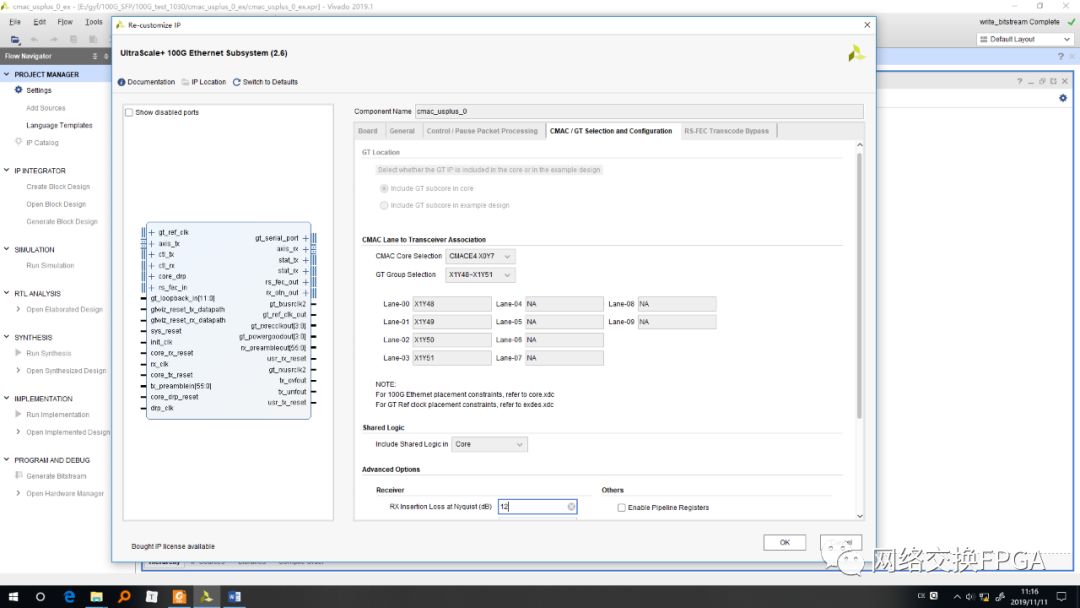

2、100G IP核 所使用的IP核是UltraScale+ 100G Ethernet subsystem。IP核配置界面如下圖所示:

因環境選擇的是Xilinx官方開發板,所以此處可以進行選擇,參考時鐘為全是qsfp1 si570 clock。

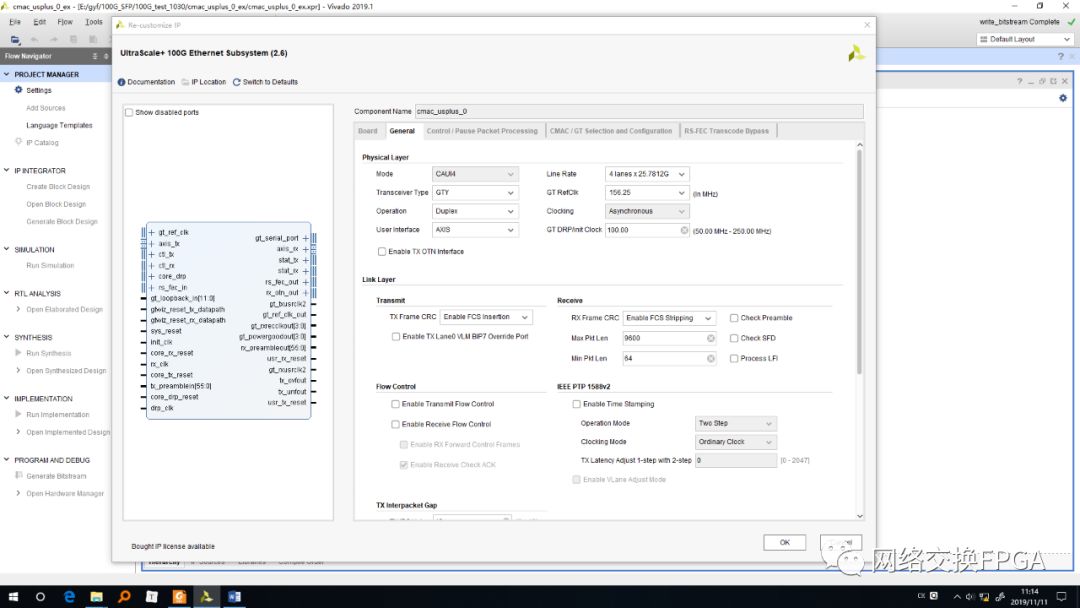

選擇四通道(CAUI4),線速率默認為4lanes * 25.7812G,GTY參考時鐘頻率為156.25Mhz(VCU118開發板給出)。發送與接收CRC校驗默認開啟。

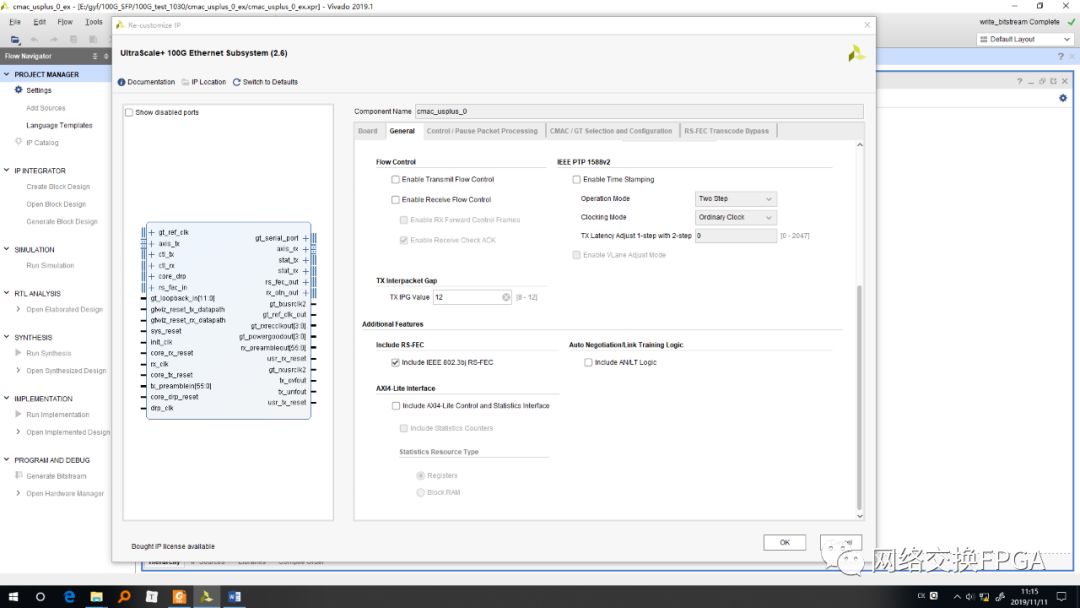

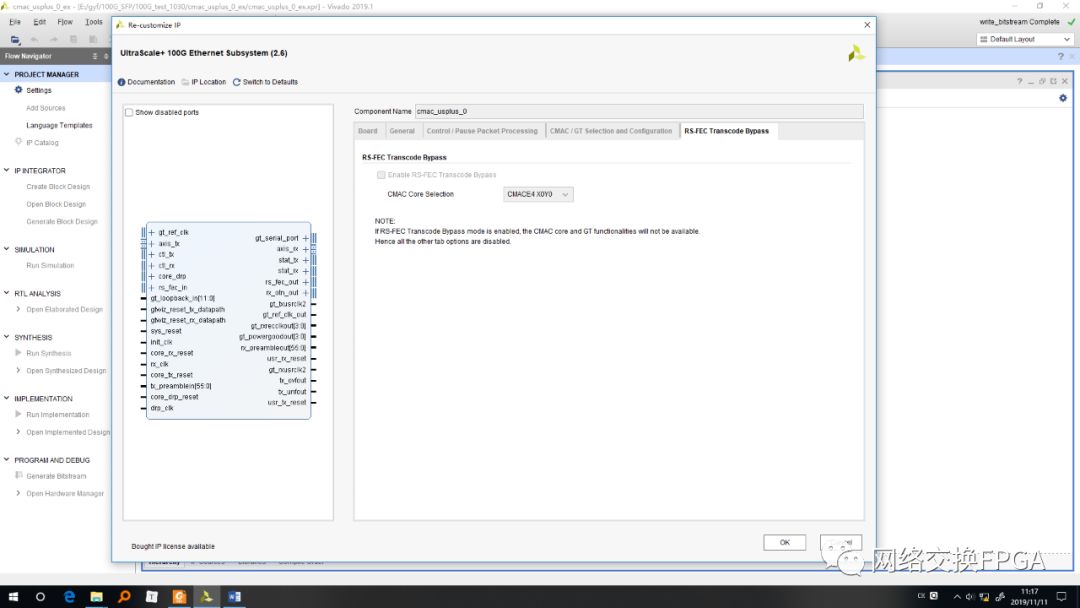

使用前向糾錯碼(RS-FEC),不開啟自適應選項(Auto Negotiation)。若FEC不開啟,開發板與網絡測試儀無法建立連接;若開啟自適應選項,IP核的bit文件無法生成(猜測與VIVADO的Licese文件有關)。

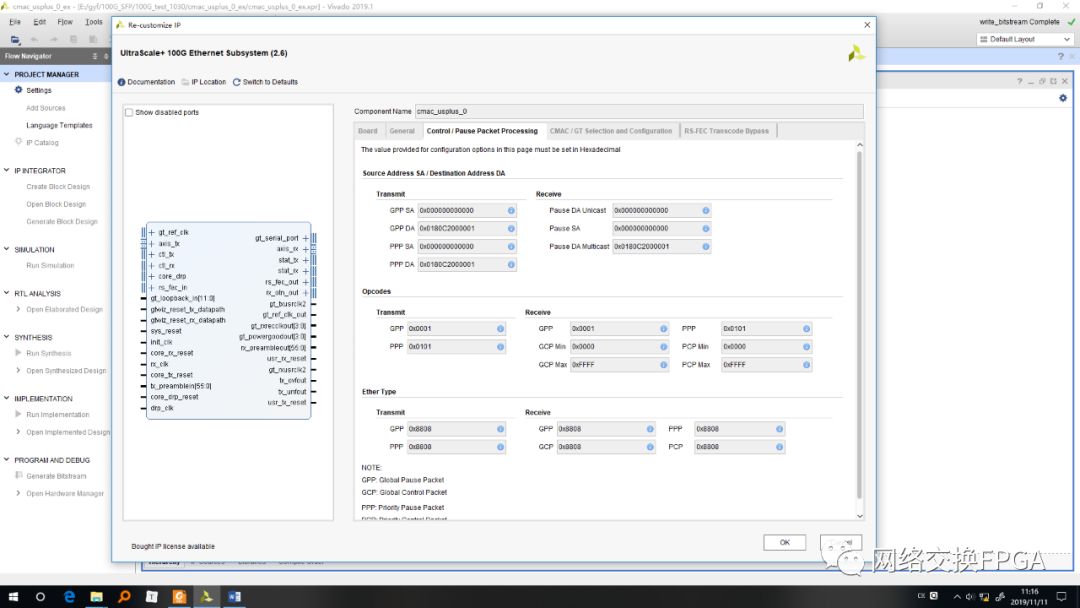

其余選項皆為默認配置,沒有進行修改。具體配置如上圖所示。3.License文件

License文件主要影響該IP核bit文件的生成,可以在Xilinx官網申請試用版License,但是License的試用期只有一年,而且在申請的時候會綁定申請主機的MAC地址,所以換到其他主機設備時無法使用,需要另外申請License文件。

二、100G工程組成及參數配置

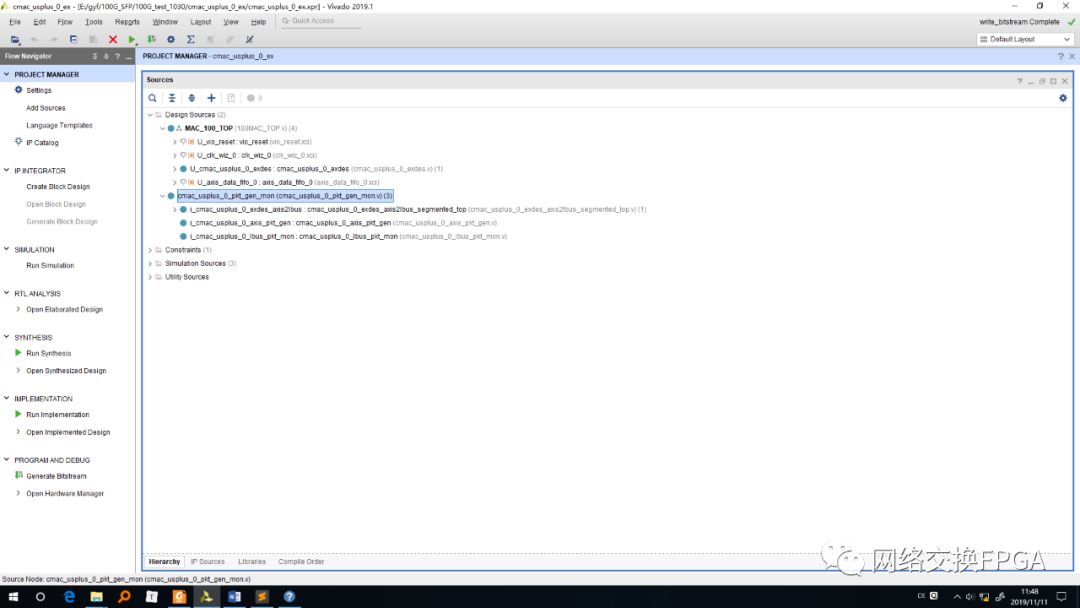

1.工程組成 由上文所述的IP核生成example design文件,刪去工程中的cmac_usplus_0_pkt_gen_mon模塊。(此模塊用于生成用戶側數據源,并校驗數據接收結果,因為需要使用網絡測試儀進行測試,所以不需要此數據源與校驗模塊) 另外復位選擇軟復位,通過VIO來實現。時鐘生成模塊產生IP核所需要的時鐘。

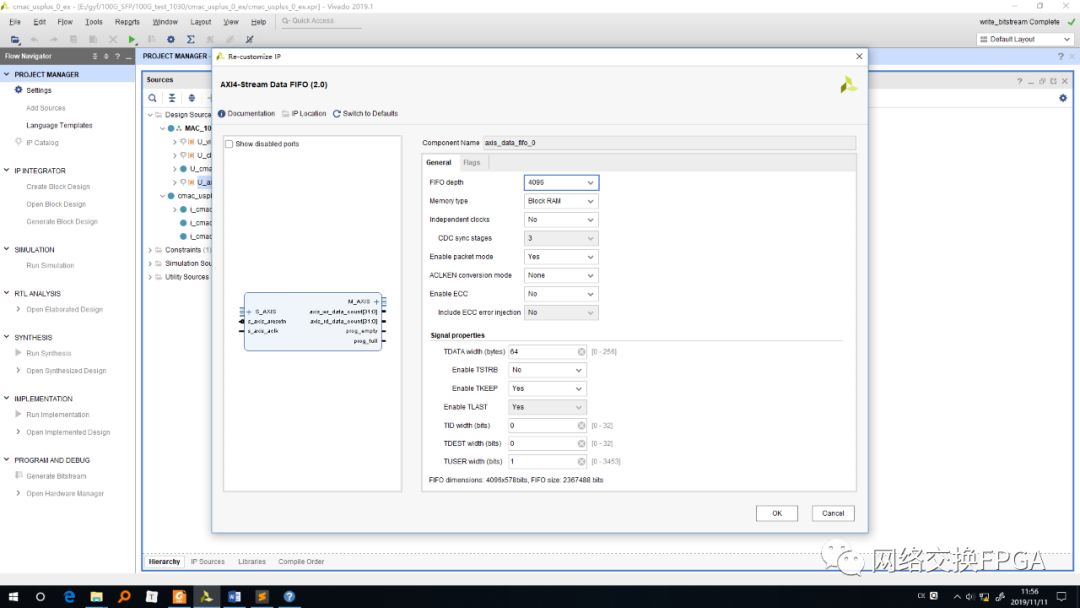

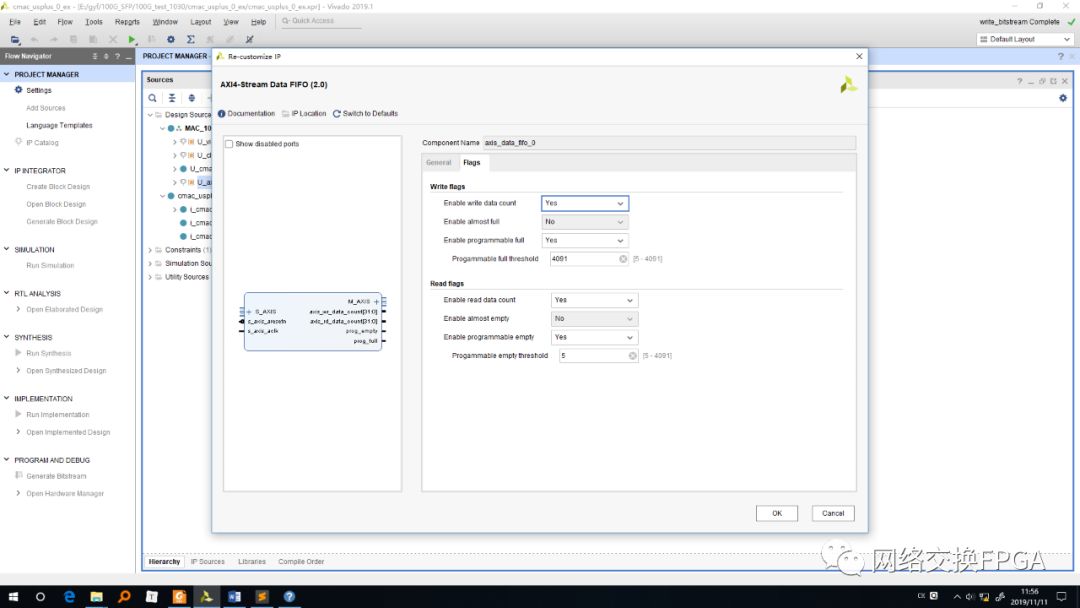

為了穩定用戶側數據,在IP核后接一個FIFO,先對用戶側接收到的數據進行緩存處理,然后將數據發往發送端。FIFO的配置如下圖所示:

2.參數配置

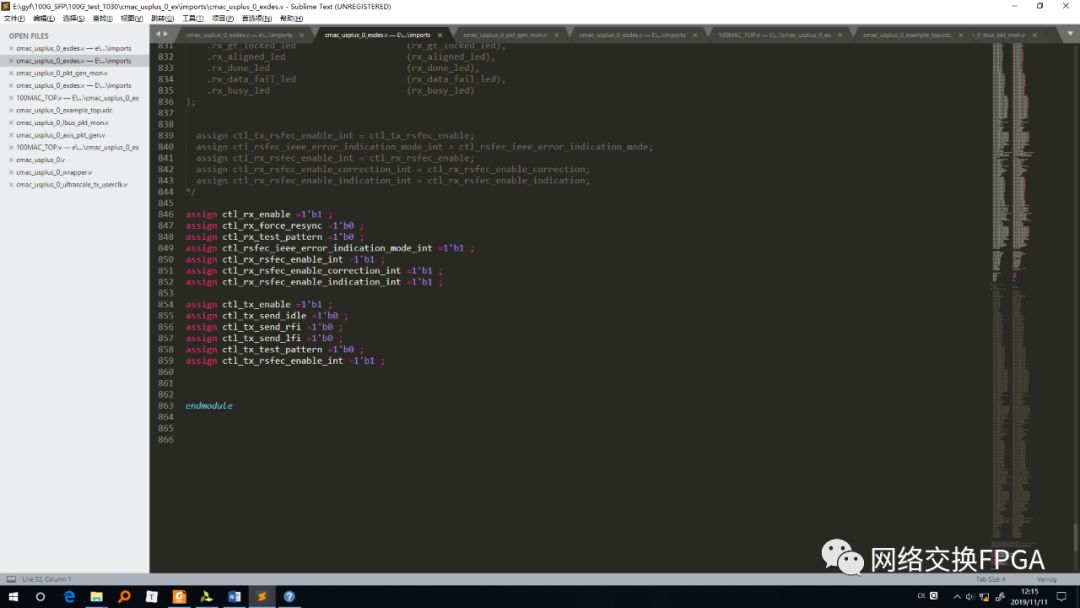

LBUS總線控制信號(信號具體解釋可以參考pg203中表2-6和表2-7)。主要是使能信號(ctrl_rx_enable和ctrl_tx_enable)要賦值為1。

三、測試結果

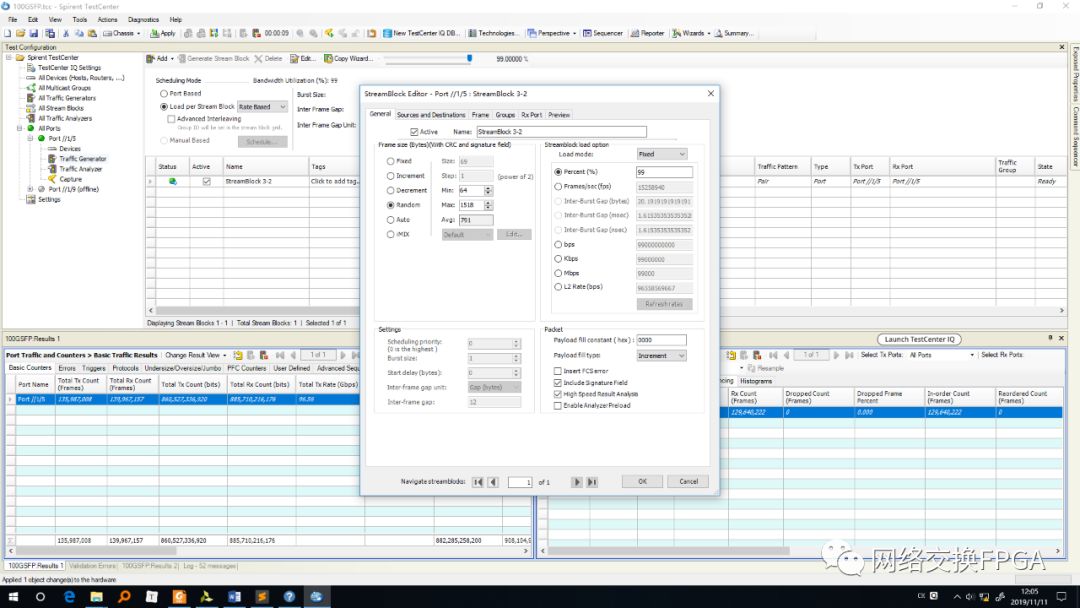

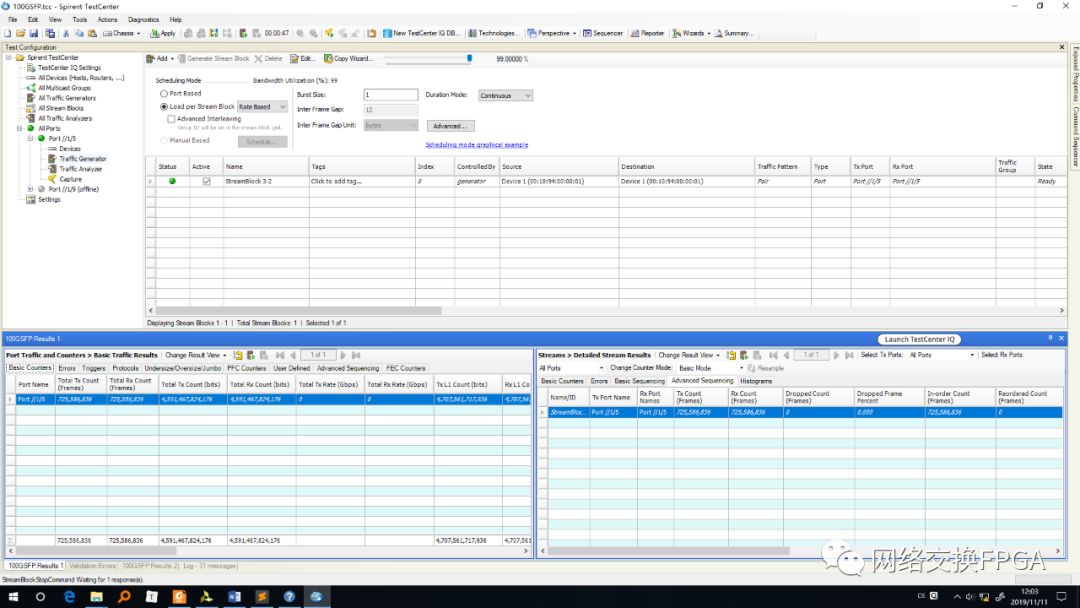

速率配置為99G(同10G接口一樣,配置為100%時會有丟幀產生),幀長為隨機幀長(64~1518)。丟幀問題與10G光口測試時的現象一致(詳見本公眾號之前文章:10G 以太網接口的FPGA實現,你需要的都在這里了),可能是Xilinx的IP核保護吧,也許你花錢購買后就可以跑到滿速了。

測試結果如下圖所示,幀計數與字節計數均一致,且未出現丟幀與錯幀,說明工程工作正常,可以完成數據的收發。

本文轉載自網絡交換FPGA

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618732 -

以太網

+關注

關注

41文章

5635瀏覽量

176031 -

Xilinx

+關注

關注

73文章

2185瀏覽量

125405 -

網絡分析儀

+關注

關注

9文章

696瀏覽量

29177 -

開發板

+關注

關注

25文章

5683瀏覽量

104896

原文標題:100G以太網光口的FPGA測試實例

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

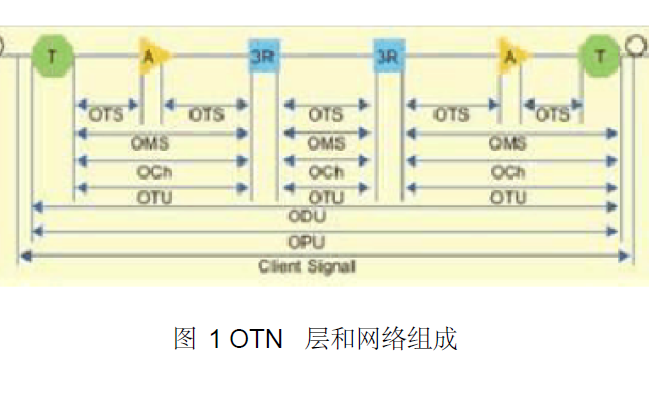

采用StratixIV FPGA實現100G光傳送網

真正實用的100G QSFP28 DAC以太網連接解決方案

怎么利用FPGA實現100G光傳送網?

如何實現100G光傳送網?

光通信主流100G光模塊淺析

Altera FPGA通過以太網聯盟100G HSE互操作性

100G比特以太網物理層標準和傳輸問題

Solomon差錯校正IP可用于100G以太網MAC IP和100G光模塊

16nm UltraScale+ FPGA的集成100G以太網解決方案介紹

QSFP28光模塊又被稱為100G光模塊,主要用在100G以太網和EDR InfiniBand應用

如何使用FPGA實現100G光傳送網的設計

100G以太網光口的FPGA測試實例

100G以太網光口的FPGA測試實例

評論