ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢?

在計算機系統中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應與系統操作相關的事件。 由于處理器必須同時執行多個任務,例如輸入/輸出(I / O)操作或計時器計數,因此異常和中斷是必不可少的。

ARM異常和中斷是在ARM內核中實現的,即在芯片上的處理器內部。當處理器執行特定的任務時,根據相應的事件,就會發生異常或中斷。

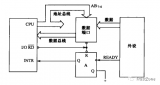

ARM的異常和中斷模塊由多個不同的組件組成。 這些組件包括處理器模式,管理寄存器和中斷控制器等。 然后,處理器根據模式來響應異常和中斷請求,并執行特定的處理過程。

在ARM體系結構中,處理器模式是ARM處理器的一種狀態。 處理器模式有七種不同的類型:用戶模式,FIQ(快速中斷請求)模式,IRQ(普通中斷請求)模式,監管模式,異常處理程序模式,中止處理程序模式和無效模式。 每個模式都定義了處理器在執行任務時可以訪問的寄存器和內存空間等。其中,異常處理程序模式是由ARM處理器用來響應異常事件和中斷請求的模式。

當ARM處理器通過異常或中斷請求進入異常處理程序模式時,它會從當前用戶模式切換到異常處理模式。處理器會將當前CPU狀態(如程序計數器,標志寄存器等)保存到內部寄存器中,然后加載處理器模式下的堆棧指針。 接下來,處理器將跳轉到指定的異常處理程序來處理異常或中斷請求。

在ARM中,中斷被分為兩類:快速中斷請求(FIQ)和普通中斷請求(IRQ)。 FIQ是ARM中處理時間敏感任務的快速中斷碼,可以提供更高的搶占優先級和更快的響應時間。所以,如果有FIQ請求,處理器會首先進入FIQ模式處理中斷請求。IRQ被認為是標準中斷請求,如果沒有FIQ請求,當出現IRQ請求時,ARM處理器便會進入中斷模式。

在ARM中,中斷請求是通過中斷控制器發送的。中斷控制器位于ARM處理器芯片中,可以將中斷請求通過對應的GPIO端口發送到ARM處理器中。 中斷控制器還會將相應的中斷優先級和中斷信息發送到ARM處理器,以便ARM處理器能夠進入恰當的模式處理中斷請求。

總結一下,ARM的異常和中斷機制提供了一種響應系統事件的方式。從硬件角度來看,ARM處理器通過處理器模式,管理寄存器和中斷控制器等多個組件來處理異常和中斷請求。當ARM處理器進入異常處理程序模式時,它從當前模式切換到處理器模式,并依據中斷類型切換到FIQ模式或IRQ模式。此過程中,中斷控制器會發送中斷請求并提供相應的優先級和信息。所有這些組成了ARM中異常和中斷機制的核心。

-

ARM

+關注

關注

134文章

9168瀏覽量

369220 -

寄存器

+關注

關注

31文章

5363瀏覽量

121172 -

異常中斷

+關注

關注

0文章

9瀏覽量

1245

發布評論請先 登錄

相關推薦

ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢?

ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢?

評論