《Vivado Design Suite 用戶指南:編程和調(diào)試》

文檔涵蓋了以下設(shè)計(jì)進(jìn)程:

硬件、IP 和平臺(tái)開(kāi)發(fā):為硬件平臺(tái)創(chuàng)建 PL IP 塊、創(chuàng)建 PL 內(nèi)核、功能仿真以及評(píng)估 AMD Vivado 時(shí)序收斂、資源使用情況和功耗收斂。還涉及為系統(tǒng)集成開(kāi)發(fā)硬件平臺(tái)。本文檔中適用于此設(shè)計(jì)進(jìn)程的主題包括:

-

第 9 章:設(shè)計(jì)調(diào)試

-

第 10 章:系統(tǒng)內(nèi)邏輯設(shè)計(jì)調(diào)試流程

-

第 11 章:在硬件中調(diào)試邏輯設(shè)計(jì)

-

第 12 章:在波形查看器中查看 ILA 探針數(shù)據(jù)

-

第 13 章:實(shí)現(xiàn)后的設(shè)計(jì)調(diào)試

開(kāi)發(fā)板系統(tǒng)設(shè)計(jì):通過(guò)原理圖和開(kāi)發(fā)板布局設(shè)計(jì) PCB。還包含功耗、散熱以及信號(hào)完整性注意事項(xiàng)。本文檔中適用于此設(shè)計(jì)進(jìn)程的主題包括:

-

第 4 章:器件編程

-

第 5 章:在 Vivado 中執(zhí)行遠(yuǎn)程調(diào)試

-

第 6 章:配置存儲(chǔ)器器件編程

-

第 7 章:高級(jí)編程功能

-

第 8 章:串行矢量格式 (SVF) 文件編程

-

第 14 章:串行 I/O 硬件調(diào)試流程

-

第 16 章:在硬件中調(diào)試串行 I/O 設(shè)計(jì)

本文選取了“第3章:生成比特流或器件鏡像”部分進(jìn)行分享。如果您希望獲取完整版用戶指南,請(qǐng)至文末掃描二維碼進(jìn)行下載。

生成比特流或器件鏡像

在生成比特流或器件鏡像之前,請(qǐng)復(fù)查其設(shè)置,確保這些設(shè)置對(duì)于您的設(shè)計(jì)都正確無(wú)誤,這一點(diǎn)至關(guān)重要。

AMD Vivado IDE 中的比特流和器件鏡像設(shè)置分為 2 種類(lèi)型:

-

比特流或器件鏡像文件格式設(shè)置。

-

器件配置設(shè)置。

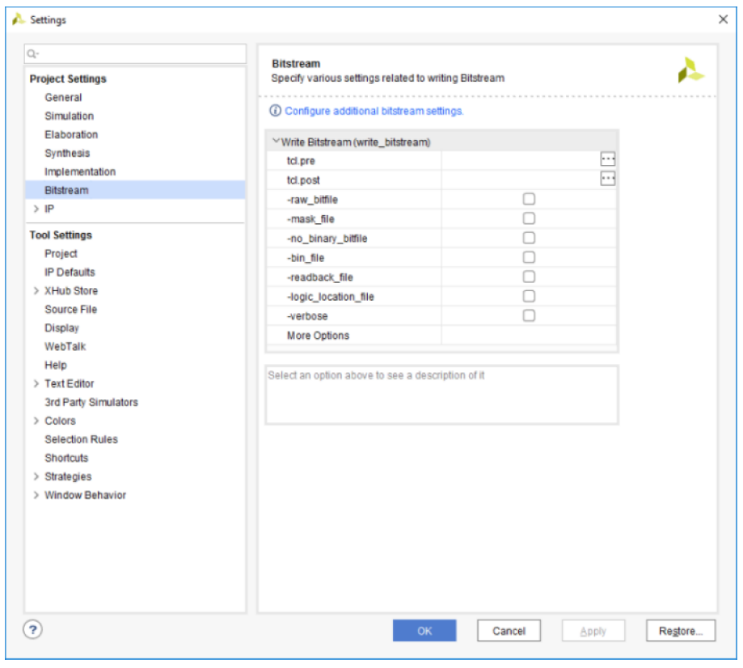

在 Vivado Flow Navigator 中依次選擇“Settings ” → “Bitstream”(設(shè)置 > 比特流),或者選擇“Flow” → “Settings” → “Bitstream Settings”(流程 > 設(shè)置 > 比特流設(shè)置)菜單選項(xiàng)以打開(kāi)“Bitstream Settings”(比特流設(shè)置)彈出窗口(如下圖所示)。只要設(shè)置正確,即可使用 write_bistream Tcl 命令或者使用 Vivado Flow Navigator 中的“Generate Bitstream”(生成比特流)按鈕來(lái)生成比特流數(shù)據(jù)文件。

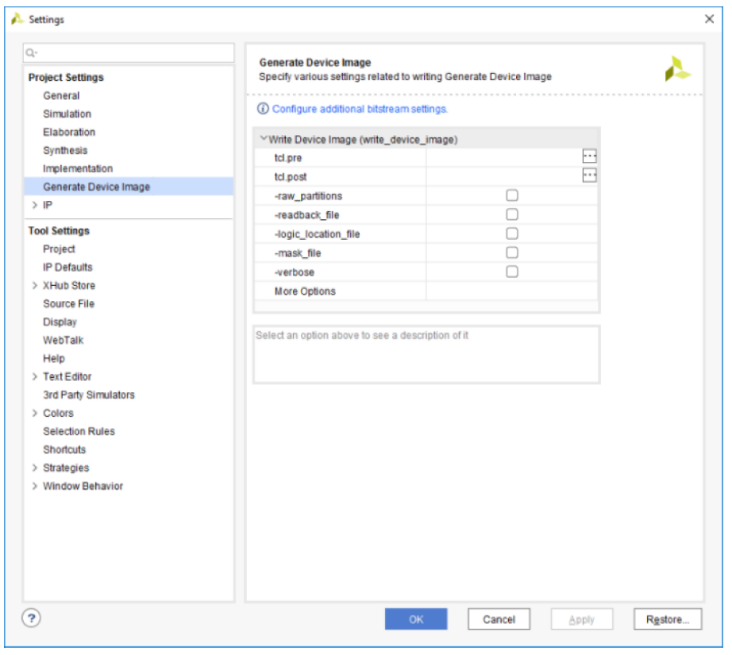

如果以 AMD Versal 器件為目標(biāo),則會(huì)生成可編程器件鏡像 (.pdi),而不是比特流文件。更改器件鏡像設(shè)置的過(guò)程與先前架構(gòu)類(lèi)似,但菜單選項(xiàng)、Tcl 命令和可用設(shè)置會(huì)有所不同。

要訪問(wèn)器件鏡像設(shè)置,請(qǐng)依次選中 Vivado Flow Navigator 中的“Settings” → “Generate Device Image”(設(shè)置 > 生成器件鏡像),或者選中“Flow” → “Settings” → “Generate Device Image Settings...”(流程 > 設(shè)置 > 生成器件鏡像設(shè)置)菜單選項(xiàng),這樣即可在“Settings”(設(shè)置)彈出窗口中打開(kāi)“Device Image”(器件鏡像)部分(請(qǐng)參閱下圖)。要生成器件鏡像數(shù)據(jù)文件,可使用 write_device_image Tcl 命令,或者使用 Vivado Flow Navigator 中的“Write Device Image”(寫(xiě)入器件鏡像)按鈕。

圖:比特流設(shè)置面板

圖:生成器件鏡像設(shè)置面板

更改比特流文件格式設(shè)置

默認(rèn)情況下,write_bitstream Tcl 命令僅生成二進(jìn)制比特流 (.bit)文件。(可選)您可通過(guò)使用以下命令開(kāi)關(guān)來(lái)更改 write_bitstream Tcl 命令寫(xiě)出的文件格式:

-

-raw_bitfile:(可選)此開(kāi)關(guān)會(huì)導(dǎo)致 write_bitstream 編寫(xiě)原始比特文件 (.rbt),其中所含信息與二進(jìn)制比特流文件中所含信息相同,但格式為 ASCII。輸出文件名為

.rbt。 -

-mask_file:(可選)編寫(xiě)掩碼文件 (.msk),其中包含有關(guān)比特流文件中配置數(shù)據(jù)所在位置的掩碼數(shù)據(jù)。此文件可用于判定比特流中哪些位應(yīng)與回讀數(shù)據(jù)進(jìn)行比較和驗(yàn)證。如果掩碼位為 0,那么應(yīng)根據(jù)比特流數(shù)據(jù)驗(yàn)證該位。如果掩碼位為 1,那么不應(yīng)驗(yàn)證該位。輸出文件名為

.msk。 -

-no_binary_bitfile:(可選)不編寫(xiě)二進(jìn)制比特流文件 (.bit)。如果要生成 ASCII 比特流文件或掩碼文件或者要生成比特流報(bào)告(而不生成二進(jìn)制比特流文件),請(qǐng)使用此命令。

-

-logic_location_file:(可選)創(chuàng)建 ASCII 邏輯位置文件 (.ll),以顯示鎖存器、觸發(fā)器、LUT、塊 RAM 和 I/O 塊輸入輸出的比特流位置。這些位元可供位置文件中的幀和位編號(hào)引用,以幫助您觀察 FPGA 寄存器的內(nèi)容。

-

-bin_file:(可選)創(chuàng)建二進(jìn)制文件 (.bin),其中僅包含器件編程數(shù)據(jù),不含標(biāo)準(zhǔn)比特流文件 (.bit) 中找到的報(bào)頭信息。

-

-reference_bitfile

:(可選)讀取引用比特流文件,并輸出增量比特流文件,其中僅含不同于指定引用文件的內(nèi)容。此部分比特流文件可用于對(duì)含更新設(shè)計(jì)的現(xiàn)有器件進(jìn)行增量編程。

向下滑動(dòng)查看

更改器件鏡像 (PDI) 文件格式設(shè)置

默認(rèn)情況下,write_device_image Tcl 命令僅生成 1 個(gè) .pdi 文件。(可選)您可通過(guò)使用以下命令開(kāi)關(guān)來(lái)更改write_device_image Tcl 命令寫(xiě)出的文件格式:

-

-force(可選):覆蓋現(xiàn)有文件。

-

-verbose(可選):打印 write_device_image 選項(xiàng)。

-

-raw_partitions(可選):寫(xiě)入原始 CFI 和 NPI 分區(qū)文件(.rnpi 和 .rcdo)

-

-mask_file(可選):寫(xiě)入掩碼文件 (.msk)

-

-logic_location_file(可選):寫(xiě)入邏輯位置文件 (.ll)

-

-cell

(可選):僅為指定單元?jiǎng)?chuàng)建部分器件鏡像。 -

-no_pdi:不生成 pdi 文件。僅生成原始分區(qū)文件后即停止操作。

-

-no_partial_pdifile(可選):不為 Dynamic Function eXchange 設(shè)計(jì)寫(xiě)入部分 pdi 文件。

-

-quiet(可選):忽略命令錯(cuò)誤。

-

(必需):要寫(xiě)入的 .pdi 文件名。

向下滑動(dòng)查看

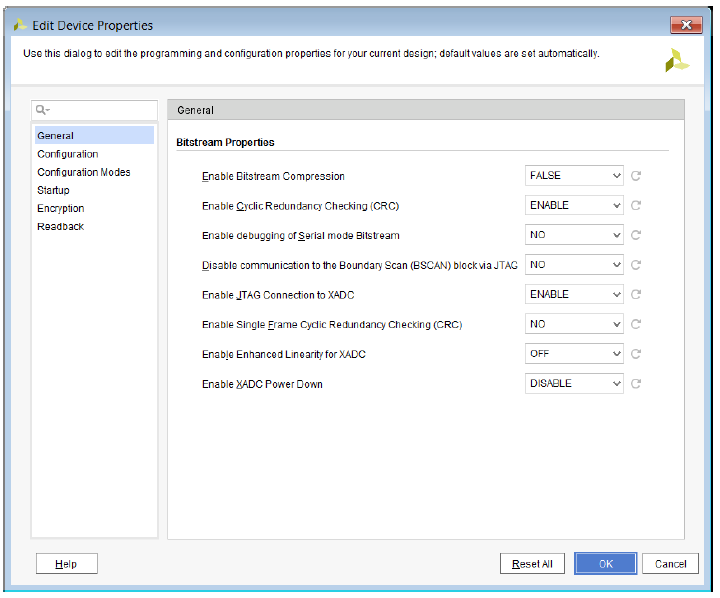

更改器件配置比特流設(shè)置

您可更改的最常見(jiàn)的配置設(shè)置歸為器件配置設(shè)置類(lèi)別。這些設(shè)置是器件模型的屬性,您可使用“Edit Device Properties”(編輯器件屬性)對(duì)話框來(lái)為選定的已綜合或已實(shí)現(xiàn)的設(shè)計(jì)網(wǎng)表更改這些設(shè)置。以下步驟描述了如何使用此方法來(lái)設(shè)置各種比特流屬性:

1.選擇“Tools” → “Edit Device Properties”(工具 > 編輯器件屬性)。

2.在“Edit Device Properties”對(duì)話框中,選擇左側(cè)列中的類(lèi)別之一(請(qǐng)參閱下圖)。

3.將屬性設(shè)為期望的值,然后單擊“OK”(確定)。

4.依次選擇“File” → “Constraints” → “Save”(文件 > 約束 > 保存)以將更新后的屬性保存到目標(biāo) XDC 文件中。

您也可以在 XDC 文件中使用 set_property 命令來(lái)設(shè)置比特流屬性。例如,以下提供了如何更改 start-up DONE cycle 屬性的示例:

set_property BITSTREAM.STARTUP.DONE_CYCLE 4 [current_design]

在 Vivado 模板中提供了更多示例和模板。“器件配置比特流設(shè)置”描述了所有器件配置設(shè)置。

獲取完整版用戶指南,請(qǐng)掃描二維碼進(jìn)行下載

原文標(biāo)題:Vivado Design Suite 用戶指南:編程和調(diào)試

文章出處:【微信公眾號(hào):Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132164 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124542

原文標(biāo)題:Vivado Design Suite 用戶指南:編程和調(diào)試

文章出處:【微信號(hào):賽靈思,微信公眾號(hào):Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

AMD Vivado Design Suite 2025.1現(xiàn)已推出

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

AMD Vivado Design Suite IDE中的設(shè)計(jì)分析簡(jiǎn)介

Vivado Design Suite用戶指南: 設(shè)計(jì)分析與收斂技巧

Vivado Design Suite用戶指南:邏輯仿真

MSP430存儲(chǔ)器編程用戶指南

《CST Studio Suite 2024 GPU加速計(jì)算指南》

MSP Gang編程器(MSP-GANG)用戶指南

AMD Vivado Design Suite 2024.2全新推出

U50的AMD Vivado Design Tool flow設(shè)置

MicroBlaze V軟核處理器的功能特性

Vivado Design Suite 用戶指南:編程和調(diào)試

Vivado Design Suite 用戶指南:編程和調(diào)試

評(píng)論