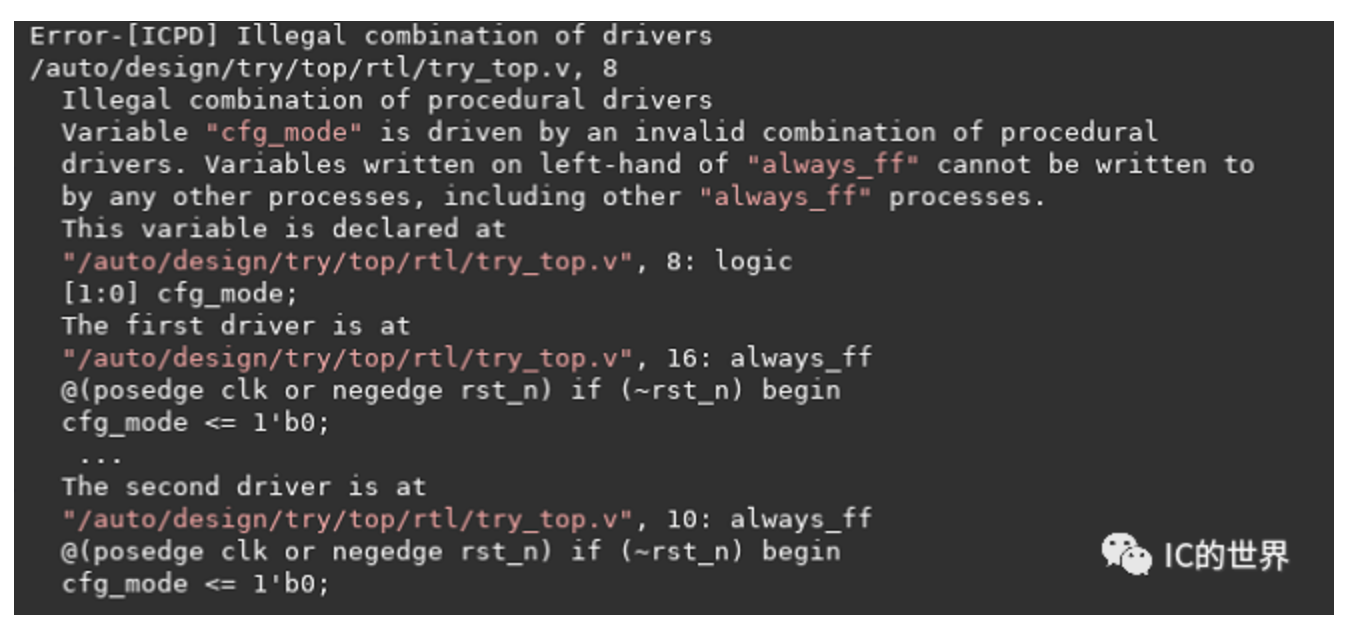

我們再從對可綜合代碼的支持角度看看SystemVerilog相比于Verilog的優勢。針對硬件設計,SystemVerilog引入了三種進程always_ff,always_comb和always_latch。always_ff用于描述時序邏輯,對應FPGA中的觸發器,其內部應使用非阻塞(<=)賦值方式,因為它模擬的正是觸發器傳輸數據的方式。always_comb用于描述純組合邏輯,其內部使用阻塞賦值方式,采用了隱式的全變量敏感列表。always_latch用于描述鎖存器。FPGA設計中一般不建議使用鎖存器。這樣,三種進程對應三種場景,無論是設計者還是工具本身對電路意圖都非常清晰。在Verilog中,只有always,換言之,這三種進程都能通過always實現。例如:

always @(posedge clk) 對應 always_ff@(posedge clk)

always @* 對應always_comb或always_latch

SystemVerilog引入了轉換操作符,支持類型轉換、位寬轉換和符號轉換。

類型轉換:casting_type’(expression)

位寬轉換:size’(expression)

符號轉換:signed’(expression) 和unsigned’(expression)

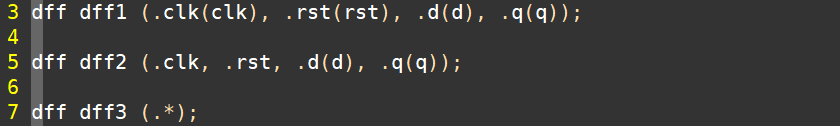

再從端口映射看,SystemVerilog支持Verilog傳統的一一映射方式,如下圖所示代碼第3行。同時也支持自動匹配,如代碼第5行,.clk和.rst會自動與名為clk和rst的信號相連。而更為簡潔的是代碼第7行所示的.*連接方式,這表明所有端口將自動與其名字相同的信號相連。盡管這三種方式都是可綜合的,但從代碼風格角度而言,仍然建議采用第3行所示方式。在描述測試文件時,可采用第7行所示方式。

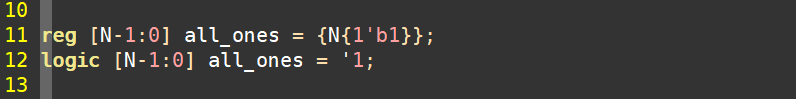

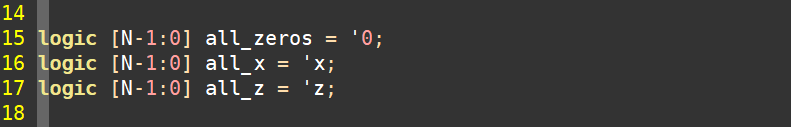

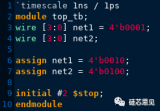

在Verilog中,給一個信號所有位賦值為1,需要采用如下圖所示方式,而SystemVerilog可直接采用下圖代碼第12行所示方式。同時此方式還適用于賦值全0、全X和全Z。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1640文章

21903瀏覽量

611501 -

Verilog

+關注

關注

28文章

1363瀏覽量

111357 -

System

+關注

關注

0文章

165瀏覽量

37476 -

觸發器

+關注

關注

14文章

2029瀏覽量

61735

原文標題:SystemVerilog不只是用于驗證(2)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog學習一 —— 計數器

相比較于LPDDR4X,LPDDR5有哪些優勢?

SystemVerilog 3.1a語言參考手冊

SystemC 和SystemVerilog的比較

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

從Verilog PLI到SystemVerilog DPI的演變過程

verilog-2005和systemverilog-2017標準規范

systemverilog:logic比reg更有優勢?

SystemVerilog在硬件設計部分有哪些優勢

systemverilog:logic比reg更有優勢

SystemVerilog相比于Verilog的優勢

SystemVerilog相比于Verilog的優勢

評論