Microchip推出針對(duì)智能邊緣設(shè)計(jì)的定制PolarFire FPGA和SoC解決方案堆棧,以加快開發(fā)速度,同時(shí)推動(dòng)FPGA的采用。

為了加快智能邊緣設(shè)計(jì),Microchip Technology Inc.在其中端PolarFire FPGA和片上系統(tǒng)(SoC)中增加了10個(gè)技術(shù)和應(yīng)用特定的解決方案堆棧。這些解決方案集合面向工業(yè)邊緣、智能嵌入式視覺和邊緣通信,包括 IP、參考設(shè)計(jì)、開發(fā)套件、應(yīng)用說明和演示指南。

多年來,F(xiàn)PGA制造商面臨的一件事是FPGA編程的復(fù)雜性,這阻礙了許多應(yīng)用的采用。盡管FPGA的主要優(yōu)勢(shì)在于提供AI算法加速,定制設(shè)計(jì)和重新編程以滿足新需求的能力。

成本也是一個(gè)問題,但在某些特定應(yīng)用中,F(xiàn)PGA 比其他處理器(如微控制器 (MCU)、微處理器 (MPU) 和圖形處理器 (GPU))具有優(yōu)勢(shì)。然而,多年來,像Microchip這樣的FPGA制造商在降低成本方面取得了進(jìn)展,使FPGA更節(jié)能,更小。

Microchip的新解決方案堆棧和軟件開發(fā)套件(SDK)正在解決這些問題,使FPGA設(shè)計(jì)變得更加容易,同時(shí)使計(jì)算機(jī)工程師和FPGA設(shè)計(jì)人員之間能夠更好地協(xié)作。

為什么Microchip要為智能邊緣提供這些量身定制的設(shè)計(jì)?其中一個(gè)重要原因是需求,當(dāng)然,該公司希望成為智能邊緣的領(lǐng)導(dǎo)者。另一個(gè)原因是推動(dòng)FPGA的采用。

“作為一種技術(shù),我們需要更加平易近人,這就是我們提供解決方案堆棧的原因,”Microchip的FPGA業(yè)務(wù)部門戰(zhàn)略副總裁Shakeel Peera說。

Microchip聲稱其FPGA業(yè)務(wù)同比增長(zhǎng)32%,這得益于其PolarFire中端旗艦FPGA平臺(tái)。

Peera表示,PolarFire是該公司35年歷史上增長(zhǎng)最快的FPGA平臺(tái)(1985年作為Actel開始,后來于2010年被Microsemi收購(gòu),2018年被Microchip收購(gòu))。現(xiàn)在已經(jīng)是第五個(gè)年頭了,PolarFire已經(jīng)增長(zhǎng)了90%。

Peera表示,推動(dòng)這一增長(zhǎng)的是智能邊緣,Microchip的前20名PolarFire客戶中有65%在這個(gè)領(lǐng)域。智能邊緣增長(zhǎng)跨越各行各業(yè),包括工業(yè)邊緣、5G/數(shù)據(jù)網(wǎng)絡(luò)、物聯(lián)網(wǎng)中的 AI/ML、醫(yī)學(xué)成像診斷、自動(dòng)駕駛汽車、軍事/航空航天和空間計(jì)算。

FPGA 因其靈活性而非常適合智能邊緣應(yīng)用。這些應(yīng)用程序高度專業(yè)化,具有不同的架構(gòu)和不斷發(fā)展的算法。

Peera說,這些應(yīng)用程序是由在邊緣生成數(shù)據(jù)和處理數(shù)據(jù)的需求驅(qū)動(dòng)的,而不是在云和數(shù)據(jù)中心進(jìn)行。

他補(bǔ)充說,在過去十年左右以及最近發(fā)生的事情是,大部分處理將在邊緣設(shè)備上本地完成。

引用的一個(gè)例子是高級(jí)駕駛輔助系統(tǒng)(ADAS),它需要低延遲。皮拉說,如果不對(duì)汽車本身進(jìn)行處理,它就無法工作。“它必須是天生的低延遲,因此處理必須在本地完成,并且必須在本地做出決定。

其他示例包括可實(shí)現(xiàn)設(shè)備之間低延遲通信的 5G 網(wǎng)絡(luò)、工業(yè) 4.0+ 或工業(yè)自動(dòng)化、醫(yī)學(xué)成像和物聯(lián)網(wǎng)。

為什么選擇 FPGA 實(shí)現(xiàn)智能邊緣?

Peera說,今天的處理元件通常是串行處理單元 - GPU,MCU,MPU或CPU - 并且FPGA并行執(zhí)行處理,并且比串行處理單元更有效地處理。

AI / ML應(yīng)用于各種架構(gòu) - 面部識(shí)別,車牌識(shí)別,安全,熱成像等 - FPGA非常擅長(zhǎng)支持各種架構(gòu),因?yàn)樗鼈兛梢噪S著時(shí)間的推移重新編程,他補(bǔ)充說。“因此,當(dāng)有高度專業(yè)化的應(yīng)用需要加速時(shí),F(xiàn)PGA非常擅長(zhǎng)。

但是,Peera 也明確表示,工程師有很多選擇,根據(jù)他們?cè)噲D解決的問題和所需的性能,它將決定他們將使用哪個(gè)處理器平臺(tái)。

PolarFire FPGA 和 SoC FPGA

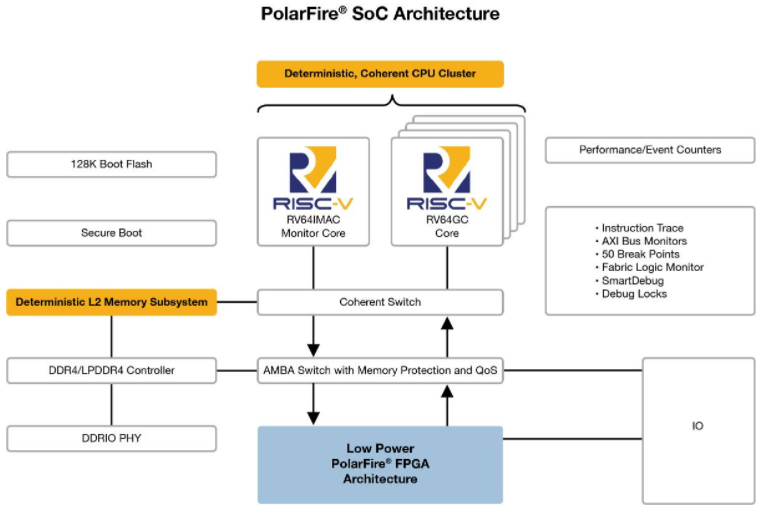

Microchip在功率效率方面處于市場(chǎng)領(lǐng)先地位。據(jù)該公司稱,PolarFire系列的功率效率是同類FPGA的兩倍,具有最高的可靠性和軍用級(jí)安全性,并且是第一款也是唯一一款量產(chǎn)的RISC-V SoC FPGA。PolarFire SoC 器件可創(chuàng)建新的可配置處理功能,面向功耗敏感型智能邊緣應(yīng)用。

智能邊緣設(shè)計(jì)有特殊要求。Peera說,邊緣設(shè)備通常不是大型系統(tǒng),而是小型盒狀系統(tǒng),可以遠(yuǎn)程部署在不在中央辦公室的區(qū)域。

因此,從一開始,熱約束和最小功率預(yù)算就是獨(dú)特的需求,他補(bǔ)充說。

Peera表示,與競(jìng)爭(zhēng)對(duì)手相比,Microchip的PolarFire設(shè)備可以平均以大約一半的功率執(zhí)行相同的工作負(fù)載,盡管它在30%到70%之間變化。

這與競(jìng)爭(zhēng)器件的熱效率成本有關(guān)。Peera說,從貨幣化的角度來看,為了消除熱量并使系統(tǒng)正常工作,Microchip的研究表明,它的成本約為1.50美元/瓦。

此外,由于漏電流高,熱失控成為一個(gè)問題,Peera說。“在某些時(shí)候,如果你負(fù)擔(dān)過重,你的設(shè)備就會(huì)出現(xiàn)故障,所以你必須非常小心芯片中有多少處理。

Microchip的PolarFire器件由于使用了非易失性(NV)存儲(chǔ)器,因此固有地提供較低的漏電流。“泄漏電流越低,熱失控上限就越低,因此您可以進(jìn)行更多處理,這與您在單個(gè)芯片上進(jìn)行更多計(jì)算而節(jié)省了多少美元有關(guān),”Peera說。

他說,NV技術(shù)天生具有較低的泄漏,PolarFire FPGA的靜態(tài)泄漏電流是其他FPGA供應(yīng)商使用的易失性SRAM的十分之一。“這給了我們一個(gè)競(jìng)爭(zhēng)無法克服的優(yōu)勢(shì)。

Peera說,安全性也正在成為一個(gè)大問題,隨著能夠破解不對(duì)稱密碼學(xué)的量子計(jì)算,這種情況只會(huì)變得更糟。

他補(bǔ)充說,兩大問題是知識(shí)產(chǎn)權(quán)保護(hù)和信息保障。“知識(shí)產(chǎn)權(quán)保護(hù)意味著有人不會(huì)從你的FPGA竊取你的IP,然后克隆它,數(shù)據(jù)安全意味著當(dāng)你的芯片與外界通信時(shí),這些信息從A點(diǎn)傳輸?shù)紹點(diǎn)時(shí)是有保證的,沒有人入侵它。

“有大量的加密元素可以放入軟件中,但你的設(shè)備是否可以被物理篡改并不重要,”Peera補(bǔ)充道。

Microchip的FPGA與美國(guó)國(guó)防部合作超過30年,內(nèi)置了安全硬件,包括NIST認(rèn)證的加密加速器,物理上不可克隆的功能和內(nèi)置的篡改檢測(cè)器。此外,抗量子身份驗(yàn)證也在路線圖上。

此外,在擁有關(guān)鍵基礎(chǔ)設(shè)施或高輻射環(huán)境的地區(qū),需要零配置故障,Peera說。

他補(bǔ)充說,Microchip的FPGA不受輻射效應(yīng)的影響,輻射效應(yīng)正在成為地面系統(tǒng)中的一個(gè)問題,例如智能電網(wǎng),數(shù)據(jù)存儲(chǔ),通信基礎(chǔ)設(shè)施和航空航天系統(tǒng)以外的安全關(guān)鍵應(yīng)用。

這就是NV內(nèi)存技術(shù)的優(yōu)勢(shì)所在。

高能輻射粒子可以翻轉(zhuǎn)SRAM位 - 改變SRAM單元的狀態(tài) - 因?yàn)殡妷悍矫娴木幊趟椒浅5筒⑶铱梢院苋菀椎胤D(zhuǎn),Peera說,而NV技術(shù)是在更高的電壓電平下編程的,并且位不能翻轉(zhuǎn)。

這些優(yōu)勢(shì)共同轉(zhuǎn)化為商業(yè)市場(chǎng)的軍用和航空級(jí)安全性和可靠性。

最重要的是,平臺(tái)需要做兩件事,Peera說:“一是擁有具有FPGA信號(hào)處理單元或微處理器子系統(tǒng)(MSS)的異構(gòu)計(jì)算架構(gòu),所有這些都可供用戶使用并能夠?qū)崟r(shí)計(jì)算,因?yàn)榈脱舆t在邊緣非常重要。

“我們能夠提供可以進(jìn)行各種處理的異構(gòu)計(jì)算平臺(tái),無論是具有確定性加速器的操作系統(tǒng)還是用裸機(jī)代碼編程的東西,”他補(bǔ)充說。“一切都可以在一個(gè)FPGA平臺(tái)中作為單片解決方案使用。

除了技術(shù)優(yōu)勢(shì)之外,將開放標(biāo)準(zhǔn)RISC-V用于其PolarFire SoC FPGA使Microchip能夠更輕松,更快速地進(jìn)行創(chuàng)新。

Peera表示,該公司當(dāng)時(shí)冒著很大的風(fēng)險(xiǎn)選擇RISC-V而不是Arm,關(guān)于他們是否應(yīng)該這樣做有很多爭(zhēng)論。

一旦決定遷移到RISC-V,Microchip開發(fā)了一種架構(gòu),以非常小的外形在單片MSS平臺(tái)上提供低功耗,高度靈活的緩存,非對(duì)稱處理功能(使用四核64位RISC-V處理器),實(shí)時(shí)裸機(jī)和RTOS。

使計(jì)算機(jī)工程師更容易訪問 FPGA

Peera說,F(xiàn)PGA是非常節(jié)能的加速器,但要使用它們進(jìn)行編程和設(shè)計(jì),工程師需要對(duì)定制硬件有先天的知識(shí)。

這意味著您必須是ASIC或FPGA設(shè)計(jì)人員。

問題在于算法設(shè)計(jì)人員不是 ASIC 或 FPGA 設(shè)計(jì)人員;Peera解釋說,他們是計(jì)算機(jī)工程師,他們學(xué)會(huì)了用C / C++設(shè)計(jì)算法,這不支持定制硬件開發(fā)。

“那么,如何讓FPGA對(duì)計(jì)算機(jī)工程師來說更容易接近,這是業(yè)界正在進(jìn)行的爭(zhēng)論?人們喜歡FPGA,但他們最終使用GPU,CPU和MCU進(jìn)行設(shè)計(jì),因?yàn)樗麄冎恍枰肅 / C++進(jìn)行設(shè)計(jì),他們不需要了解底層定制硬件,這就是FPGA,“他補(bǔ)充道。

因此,Microchip選擇了三個(gè)熱門領(lǐng)域——計(jì)算機(jī)視覺(或智能嵌入式視覺)、工業(yè)邊緣(或工業(yè)自動(dòng)化)和邊緣通信,這些領(lǐng)域“對(duì)智能邊緣來說是完全神圣不可侵犯的”——以加快開發(fā)和設(shè)計(jì)時(shí)間,同時(shí)應(yīng)對(duì)一些最大的挑戰(zhàn),包括能效、安全性、延遲和尺寸。

“這些是智能邊緣的主要?dú)⑹旨?jí)應(yīng)用,”Peera說。

他補(bǔ)充說,圍繞生成人工智能有很多嗡嗡聲,但它仍處于起步階段。“推動(dòng)貨幣化的是機(jī)器視覺。

Peera說,工業(yè)邊緣包括機(jī)器人技術(shù)、揀選技術(shù)和工廠自動(dòng)化等領(lǐng)域,而支撐所有這些的是邊緣通信,因此所有系統(tǒng)都可以相互通信,包括從光學(xué)數(shù)據(jù)網(wǎng)絡(luò)到5G O-RAN的所有內(nèi)容。

雖然這些解決方案是一個(gè)良好的開端,但計(jì)算機(jī)工程師使用 C/C++ 進(jìn)行編程。FPGA編程的標(biāo)準(zhǔn)語言是Verilog硬件描述語言(HDL)或VHSIC HDL(VHDL)。

Microchip為FPGA提供了自己的C/C++高級(jí)合成,稱為SmartHLS,允許工程師通過處理軟件/硬件分區(qū)、編譯MSS和硬件代碼以及編程FPGA來輕松使用其算法進(jìn)行FPGA設(shè)計(jì)。好處包括更快的設(shè)計(jì)周期和更少的代碼行,并且無需完全了解底層硬件。

“學(xué)校并沒有為 FPGA 培養(yǎng)大量電氣工程師;我們正在培養(yǎng)更多的計(jì)算機(jī)工程師,這只是美國(guó)生活的事實(shí),“皮拉說。

“所以FPGA設(shè)計(jì)師是一種罕見的商品,”他補(bǔ)充道。“這里的想法是使計(jì)算機(jī)工程師和FPGA設(shè)計(jì)人員之間的協(xié)作更加容易。并非所有計(jì)算機(jī)工程師都會(huì)使用FPGA作為事實(shí)上的標(biāo)準(zhǔn),但FPGA擅長(zhǎng)某些事情。

Peera 解釋說,這些解決方案的架構(gòu)使計(jì)算機(jī)工程師能夠處理 AI/ML 算法,并以他們理解的方式將其移交給 FPGA 設(shè)計(jì)人員,并補(bǔ)充說,這使得 FPGA 在協(xié)作設(shè)計(jì)環(huán)境中變得平易近人。

FPGA提供了一個(gè)空白的石板,Peera說。“如果你完成了80%的算法,但需要處理20%的新算法,那么FPGA在這方面非常棒,并且在新興的混沌領(lǐng)域占有一席之地,而今天,它是AI / ML。

解決方案

PolarFire FPGA 智能邊緣解決方案堆棧針對(duì)特定技術(shù)和垂直市場(chǎng):智能嵌入式視覺、工業(yè)邊緣和邊緣通信。

智能嵌入式視覺堆棧包括 H.264 壓縮、HDMI、串行數(shù)字接口和 CoaXpress。它們?yōu)?a href="http://m.xsypw.cn/v/tag/117/" target="_blank">傳感器和顯示接口、編碼/解碼、圖像處理、DDR 控制器、傳輸接口和深度學(xué)習(xí)推理(通過 VectorBlox SDK)提供了多種選項(xiàng)。

嵌入式應(yīng)用,如增強(qiáng)現(xiàn)實(shí)、醫(yī)療視覺、監(jiān)控、熱視覺和虛擬現(xiàn)實(shí),正在推動(dòng)AI/ML以非常高的分辨率(4K到8K以上)的貨幣化,共同的因素是它們非常小,功耗低,需要熱效率,Peera說。

他解釋說,預(yù)制的解決方案堆棧和SDK使嵌入式視覺所需的算法的移植變得非常容易,包括從傳感器后處理到將處理后的圖像分發(fā)到顯示器,網(wǎng)絡(luò)或機(jī)械臂等的所有內(nèi)容,中間是深度學(xué)習(xí)推理。

Peera說,這些構(gòu)建模塊使設(shè)計(jì)人員更容易開始設(shè)計(jì),提供整體系統(tǒng)解決方案,不僅提供FPGA,還提供其底層解決方案堆棧及其周圍的解決方案。

工業(yè)邊緣專注于電機(jī)控制和開放平臺(tái)通信/統(tǒng)一架構(gòu)(OPC/UA)。邊緣通信面向軟件定義無線電、USXGMII、小型可插拔 (SFP+) 光模塊和 5G O-RAN。

電機(jī)控制解決方案由 PolarFire 設(shè)備和 SmartFusion 2 經(jīng)典 FPGA 的 IP 模塊和算法組成;雙軸電機(jī)控制套件;使用極火SoC進(jìn)行非對(duì)稱處理;以及軟件、編程和調(diào)試,以優(yōu)化設(shè)計(jì)。OPC/UA工業(yè)邊緣解決方案包括用于智能相機(jī)應(yīng)用的PolarFire SoC視頻套件和控制步進(jìn)電機(jī)的Icicle套件。兩者都在Linux上的OPC / UA服務(wù)器上運(yùn)行。主機(jī)Windows PC運(yùn)行UA Expert,一個(gè)Windows OPC客戶端。

OPC / UA是開放式工業(yè)總線的一個(gè)例子,Peera說。他補(bǔ)充說,這種開放式網(wǎng)絡(luò)提供了即插即用多種解決方案的能力 - 遠(yuǎn)程連接在一起,利用FPGA靈活的I / O。

邊緣通信解決方案提供了一系列構(gòu)建塊。其中包括數(shù)據(jù)聚合/橋接、編碼/解碼、傳輸接口、以太網(wǎng) MAC 和 DDR 控制器以及光模塊接口。與PolarFire SoC FPGA一起,Microchip提供PoE PD,電源/ LDO,MEMS振蕩器和1G / 10G PHY。

SDK 也是新解決方案的一部分。一個(gè)例子是VectorBlox Accelerator SDK,用于PolarFire和PolarFire SoC FPGA的ML推理。據(jù)Microchip稱,與中檔SRAM FPGA相比,它的功率效率提高了2×至3×。主要應(yīng)用包括面部識(shí)別和車牌檢測(cè)。

擴(kuò)展的解決方案堆棧是在 6 月份宣布的面向 OPC/UA 和新資源的工業(yè)邊緣堆棧之后推出的。未來的解決方案包括 AI/ML/圖像處理、高速連接、安全性和面向計(jì)算的軟件設(shè)計(jì)套件。

Microchip還搶先了解了其第二代PolarFire FPGA,它將再次將電源效率提高一倍,提高4×。它們還將提供確定性和不對(duì)稱處理;軍用級(jí)防篡改和網(wǎng)絡(luò)安全;以及對(duì) SEU 的免疫力。

審核編輯:彭菁

-

處理器

+關(guān)注

關(guān)注

68文章

19896瀏覽量

235322 -

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618639 -

軟件開發(fā)

+關(guān)注

關(guān)注

0文章

645瀏覽量

28690 -

microchip

+關(guān)注

關(guān)注

52文章

1549瀏覽量

119085 -

soc

+關(guān)注

關(guān)注

38文章

4392瀏覽量

222818

發(fā)布評(píng)論請(qǐng)先 登錄

Microchip公布基于RISC-V的低功耗PolarFire? SoC FPGA產(chǎn)品系列的詳細(xì)信息,并啟動(dòng)早期使用計(jì)劃

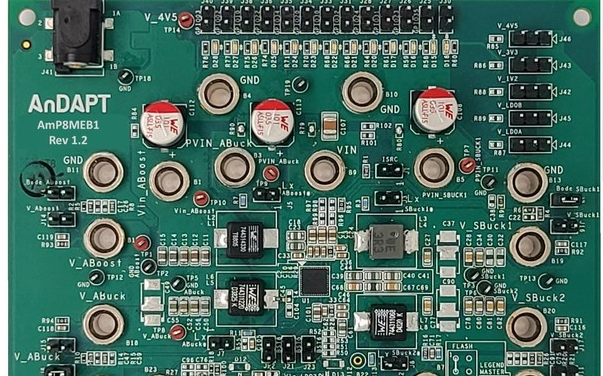

AnDAPT推出面向Microchip PolarFire FPGA的電源解決方案

Microchip發(fā)布業(yè)界首款基于 RISC-V 指令集架構(gòu)的 SoC FPGA 開發(fā)工具包

首款基于 RISC-V 指令集架構(gòu)的 SoC FPGA 開發(fā)工具包

Microchip FPGA 和基于 SoC 的 RISC-V 生態(tài)系統(tǒng)簡(jiǎn)介

Microchip將啟動(dòng)PolarFire片上系統(tǒng)FPGA EAP

Microchip計(jì)劃啟動(dòng)PolarFire片上系統(tǒng)FPGA

Microchip RISC-V FPGA SoC應(yīng)用方案

MPFS025 PolarFire FPGA SoC解決方案

Microchip推出針對(duì)智能邊緣設(shè)計(jì)的PolarFire FPGA和SoC解決方案堆棧

Microchip推出針對(duì)智能邊緣設(shè)計(jì)的PolarFire FPGA和SoC解決方案堆棧

評(píng)論