什么是阻抗匹配?高速PCB設計為什么要控制阻抗匹配?

阻抗匹配是指在電路傳輸信號時,控制電路中信號源、傳輸線和負載之間的阻抗相等的過程,從而確保信號的完整性和可靠性。在高速PCB設計中,阻抗匹配非常重要,因為在高速數(shù)字和模擬電路中,信號頻率通常在數(shù)兆赫或甚至更高的范圍內運行。如果信號阻抗不匹配,就會導致信號反射、串擾、噪聲等問題,從而影響信號穩(wěn)定性和可靠性。

阻抗匹配的定義是在不同電路元件之間實現(xiàn)阻抗的匹配,以便傳輸電路中的信號以最大可能地減少信號反射和串擾。信號源的輸出端和接收器的輸入端的特定阻抗是被標準化的,通常我們說50歐姆阻抗的條件下進行阻抗匹配。這種標準化的選擇是因為50歐姆是一種廣泛使用的標準阻抗,許多電子設備都預先設計好了50歐姆負載阻抗,并且許多電纜和傳輸線也都具有50歐姆的特性阻抗。實際上,在不同的實際應用場景中使用的阻抗值可能不同,比如在通信領域,阻抗值一般是50歐姆或75歐姆。

阻抗匹配的主要目的是防止信號反射和串擾。在傳輸線上的信號會有信號反向的現(xiàn)象發(fā)生,如果在電路中兩個相鄰的傳輸線寬度不同,阻抗就不匹配。如果反射信號回到信號源,則會導致信號的失真和噪音。

高速PCB設計中,要控制在數(shù)字和模擬電路之間的串擾,就需要做到阻抗匹配。傳輸線的質量對阻抗匹配有重要影響,因此正確地設計和選用傳輸線可大大提高傳輸線的質量。在布局設計時,應將相同類型的信號線集中在一起,確保它們有相同的阻抗,然后在連接時盡可能的使用直接連接。在傳輸信號時最好使用不同層流動的布局風格,并為其設置充分的靜電保護。

可以說高速PCB設計阻抗匹配的控制是一項非常關鍵的工作。如果沒有在設計過程中考慮到阻抗匹配的問題,最終產(chǎn)品可能會存在一系列的阻抗問題影響其正常工作,甚至導致設備損壞。因此,高速數(shù)字和模擬電路的阻抗匹配工作一定要謹慎處理。

最后,在高速PCB設計中要考慮的其他一些問題包括封裝類型和引腳數(shù)量,應在完成布局設計之后進行仿真模擬,以確定設備是否能夠正常工作。此時,系統(tǒng)應該能夠容納所有的連接,并且應該以適當?shù)姆绞竭B接所有的電子元件。我們建議在制定設計方案之前,對標準應用進行研究和測試,以便了解在實際實施過程中應該考慮哪些事項。

-

接收器

+關注

關注

15文章

2563瀏覽量

73479 -

阻抗匹配

+關注

關注

14文章

358瀏覽量

31299 -

PCB設計

+關注

關注

396文章

4788瀏覽量

89406

發(fā)布評論請先 登錄

如何確保模擬示波器的輸入阻抗匹配?

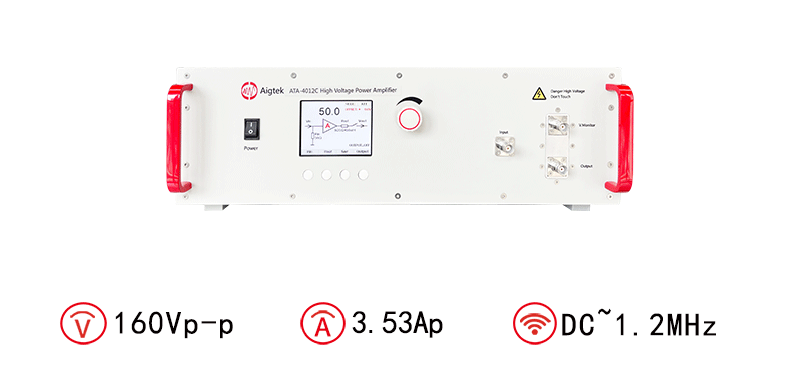

Aigtek:功率放大器如何進行阻抗匹配

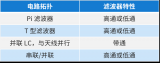

利用兩個元件實現(xiàn) L 型網(wǎng)絡阻抗匹配

Cadence技術解讀 天線的阻抗匹配技術

什么是阻抗匹配?高速PCB設計為什么要控制阻抗匹配?

什么是阻抗匹配?高速PCB設計為什么要控制阻抗匹配?

評論