1. 傳統(tǒng)單通道PLL

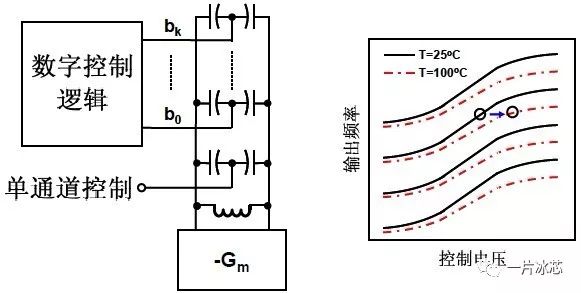

傳統(tǒng)PLL大都采用單通道控制技術,其結構框圖和調諧曲線如圖1所示。通過單通道來控制壓控振蕩器,數(shù)字邏輯控制可編程電容陣列來展寬調諧范圍,同時減小振蕩器增益(Kvco),降低了噪聲耦合和非線性。

Fig1. 單通道控制技術(a)結構框圖;(b)調頻曲線

Fig1. 單通道控制技術(a)結構框圖;(b)調頻曲線

為了滿足寬調諧范圍,往往需要較多的數(shù)字控制邏輯,電容陣列開關全部導通和全部閉合會使總電容量差別較大,導致單通道控制PLL在不同band的Kvco差別很大。如圖1(b)所示,在實際應用中,外界溫度對調頻曲線的影響明顯,特別是在調頻曲線的非中央?yún)^(qū)域,不同band的Kvco變化更加劇烈,這種變化無法通過調整數(shù)字控制邏輯進行補償。

**2. **雙通道鎖相環(huán)

2.1 Rhee****結構

雙通道結構能夠使環(huán)路濾波器控制電壓變化范圍變小,進而提高電荷泵輸出線性度,同時控制電壓處于調頻曲線的中央?yún)^(qū)域,使振蕩器調頻線性度增強。所謂雙通道就是將環(huán)路分為粗調和細調兩條支路。國內PLL大牛清華大學李宇根(Woogeun Rhee)教授發(fā)表過一篇單輸入雙通道PLL,采用90nm CMOS工藝,在PCI Express Gen2應用中實現(xiàn)了0.48ps的RJ,最大帶寬為12MHz。

Rhee提出的單輸入雙通道PLL結構和頻率調諧曲線如圖2和圖3所示,采用模擬粗調環(huán)路代替?zhèn)鹘y(tǒng)PLL中的可編程電容陣列實現(xiàn)大的頻率調諧范圍。細調控制電壓范圍相對粗調減小了k倍,提高了前級CP和后級VCO增益的線性度。

Fig2.Rhee結構框圖

Fig3.Rhee結構頻率調諧曲線

**2.2 **本人提出的雙通道結構

本人在參考Rhee提出了圖4所示的雙通道結構,控制電壓經粗調和細調環(huán)路將電壓轉成電流,為環(huán)形振蕩器(cco)提供電流(icco),滿足Icco=i1+i2,其中i1為粗調環(huán)路產生的電流,i2為細調環(huán)路產生的電流。

Fig4. 本人提出的雙通道結構

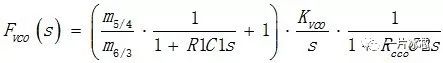

之所以稱為粗調環(huán)路是因為電阻R1和電容C1為環(huán)路提供了一個很大的時間常數(shù),R1和C1為環(huán)路增加了一組極零對。粗調環(huán)路大RC的存在,使得環(huán)路等效增益主要由細調環(huán)路決定,假設細調環(huán)路引入的增益為Kvco,M5與M4尺寸比為m5/4,M6與M3尺寸比為m6/3,則圖4所示相位域的表達式為(忽略C2的影響):

可見雙通道鎖相環(huán)在單環(huán)鎖相環(huán)的基礎上增加了一個極點和一個零點,頻率分別為:

其中ωp1和ωz1需要落在環(huán)路帶寬內且要遠遠小于單位增益帶寬,以免影響環(huán)路穩(wěn)定性。m5/4/ m6/3的比值不僅決定了環(huán)路增益,而且會影響環(huán)路穩(wěn)定性,在電路設計時應仔細考慮。

圖4中大電容C2的引入一方面降低了C2上極板的抖動,另一方面C2與cco正常工作時的等效電阻Rcco形成了一個左半軸的高頻極點,抑制了鎖相環(huán)輸出時鐘的高頻噪聲,這個極點頻率為:

C2太大會影響環(huán)路穩(wěn)定性,太小起不到濾波器作用,電路設計時置于10倍的單位增益帶寬處最佳。

由此可得圖4的完整相位域表達式為:

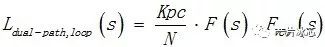

可得本文提出的單輸入雙通道鎖相環(huán)的開環(huán)傳遞函數(shù):

其中Kpc為鑒頻鑒相器和電荷泵的等效增益,大小為I CP /2π;F(s)二階濾波器傳遞函數(shù),N為內部高速分頻器的分頻比。

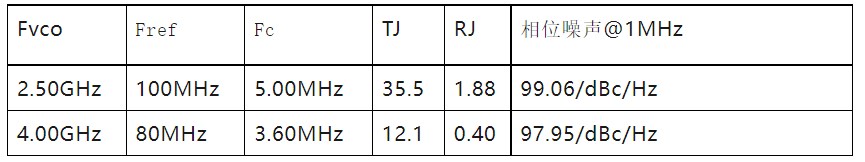

折中選取圖4中R1為421kΩ,C1為61pF,C2為17pF,m5/4為58.5,m6/3為1,細調環(huán)路Kvco為250MHz/V。然后計算出不同環(huán)路帶寬、分頻比、電荷泵電流下的濾波器參數(shù)滿足表1,其中Fref為參考頻率、Fc為環(huán)路帶寬、PM為相位裕度、Icp為電荷泵電流、Kvco為壓控振蕩器增益、N為內部高速分頻器的分頻比、R2和C1、C2表示環(huán)路濾波器中的電阻和電容。

表1 雙通道PLL輸出頻率為2.50GHz時的環(huán)路參數(shù)

傳統(tǒng)鎖相環(huán)相位在180度時向上凸起且在單位增益帶寬處有最大相位裕度,本文提出的雙通道結構由于極零對ωp1和ωz1的存在使得相位在180度時向下凹陷且在單位增益帶寬處相位裕度最大。圖5給出了表1中Fc為5.00MHz時的環(huán)路波特圖。

Fig5. Fc為5.00MHz時的環(huán)路波特圖

**2.3 **芯片測試結果

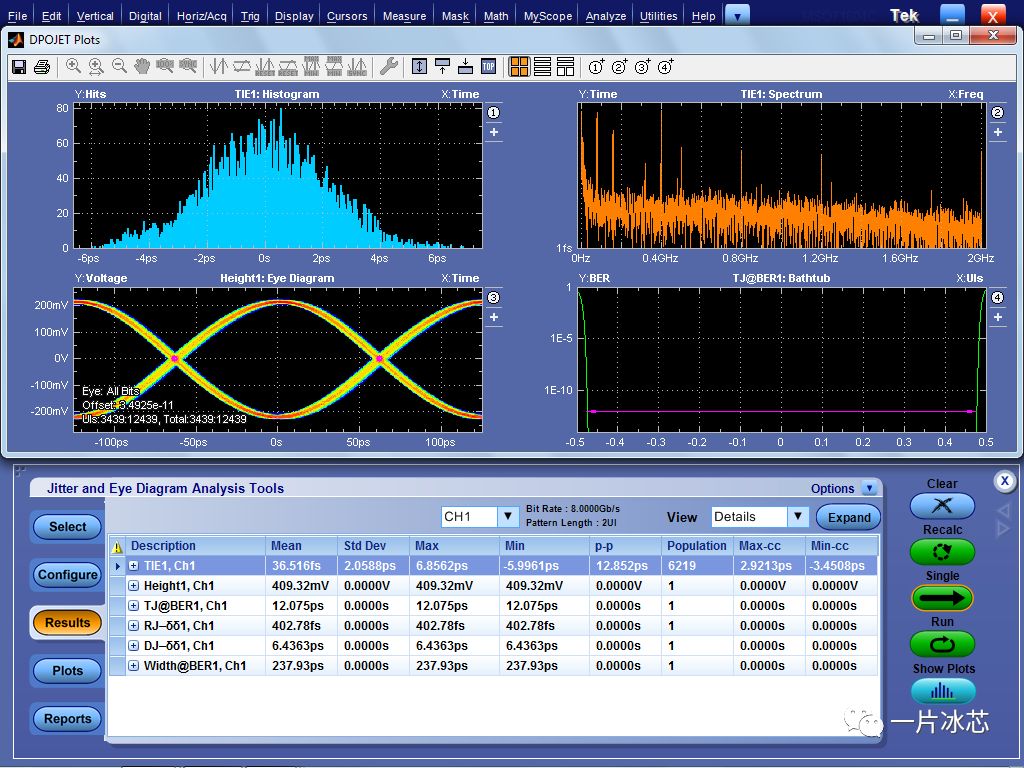

1)refclk=100MHz,環(huán)路帶寬為5MHz,輸出頻率為2.5GHz的測試結果

①頻譜儀測試結果

②示波器測試結果

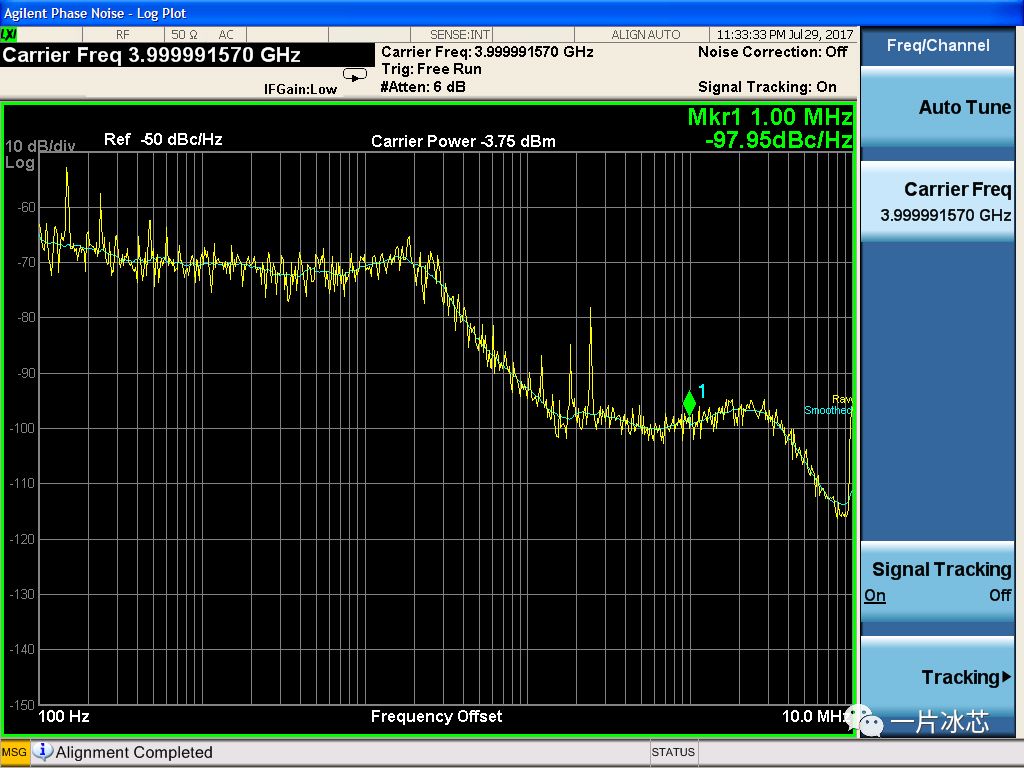

2)refclk=80MHz,環(huán)路帶寬為3.6MHz,輸出頻率為4GHz的測試結果

①頻譜儀測試結果

②示波器測試結果

測試結果總結如下表所示:

-

鎖相環(huán)

+關注

關注

35文章

596瀏覽量

88505 -

壓控振蕩器

+關注

關注

10文章

153瀏覽量

29593 -

CMOS工藝

+關注

關注

1文章

59瀏覽量

15895 -

等效電阻

+關注

關注

7文章

60瀏覽量

11667 -

PLL電路

+關注

關注

0文章

92瀏覽量

6735

發(fā)布評論請先 登錄

什么是鎖相環(huán) 鎖相環(huán)的組成 鎖相環(huán)選型原則有哪些呢?

模擬鎖相環(huán)應用實驗

鎖相環(huán)原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

模擬鎖相環(huán),模擬鎖相環(huán)原理解析

鎖相環(huán)

鎖相環(huán)技術及CD4046的結構和應用

雙通道鎖相環(huán)結構設計

雙通道鎖相環(huán)結構設計

評論