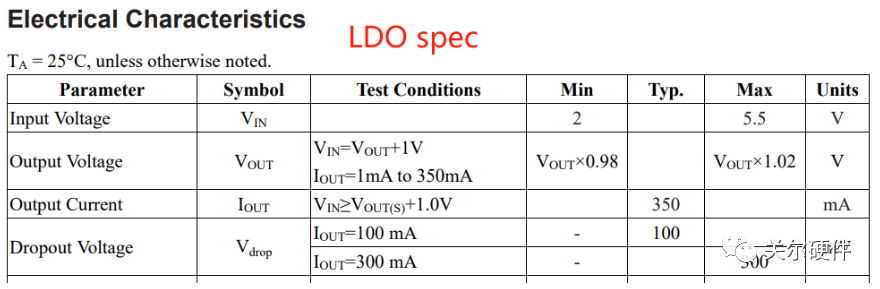

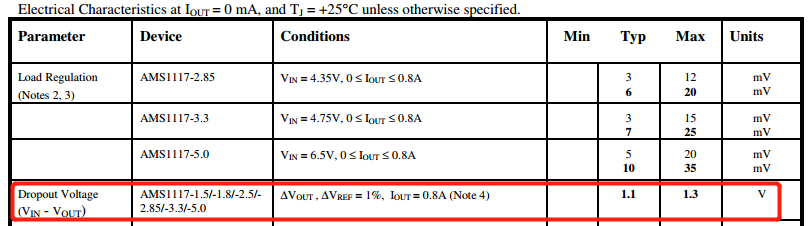

在LDO specfication里面,有Dropout Voltage(輸入輸出電壓差)的參數(shù)。如下圖,輸出電流100mA時(shí),典型壓差是100mV;輸出電流是300mA時(shí),MAX壓差是300mV(線路阻抗不變下,流過電流越大,壓降也就越大。二極管的壓降也是電流越大,壓降越大。)。

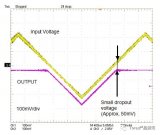

降壓DCDC是否也有輸入輸出電壓差尼?答案是肯定的。

1、100% Duty cycle的DCDC

DCDC TMI3408F上管PMOS(Vgs電壓為負(fù)時(shí)導(dǎo)通,不需要BOOST電容),下管NMOS。因?yàn)樯瞎躊MOS的S端為高(等于輸入端電源),G端為低時(shí),就導(dǎo)通。也就是說,該DCDC可以實(shí)現(xiàn)100% Duty cycle,輸入輸出的壓差就是輸出電流乘以上管PMOS的阻值,及BUCK電路電感內(nèi)阻的壓差,該輸入輸出的壓差就比較小。(note:TMI3408F是低壓輸入,輸入電壓范圍2.5V~5.5V。)

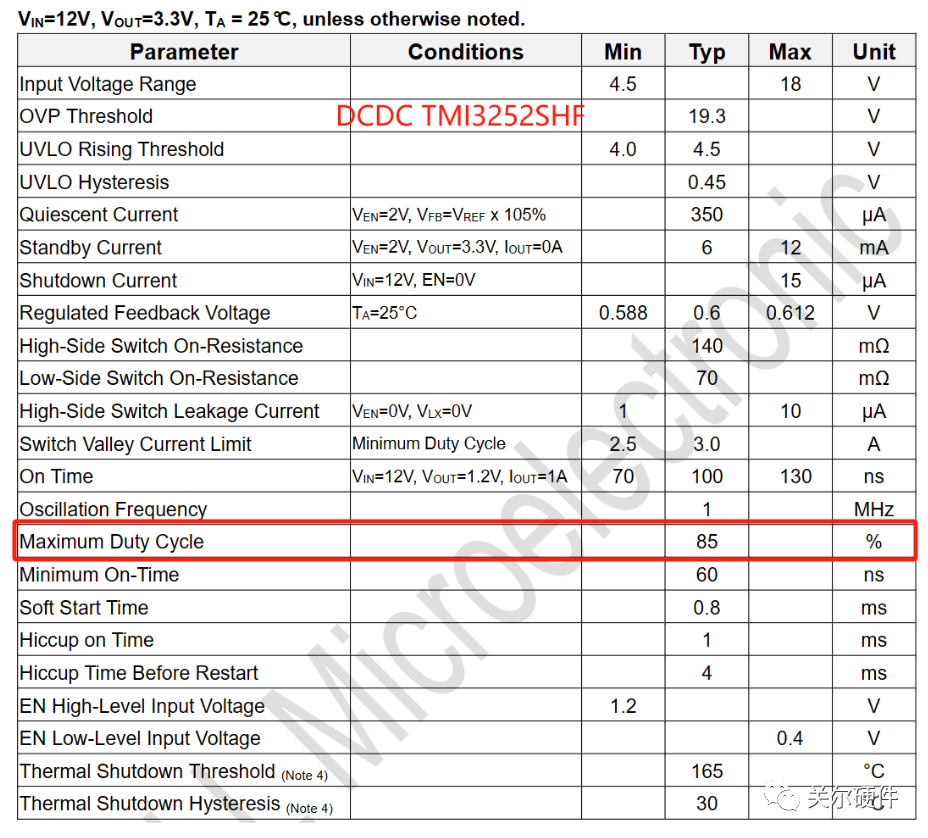

2、Maximum Duty Cycle的DCDC

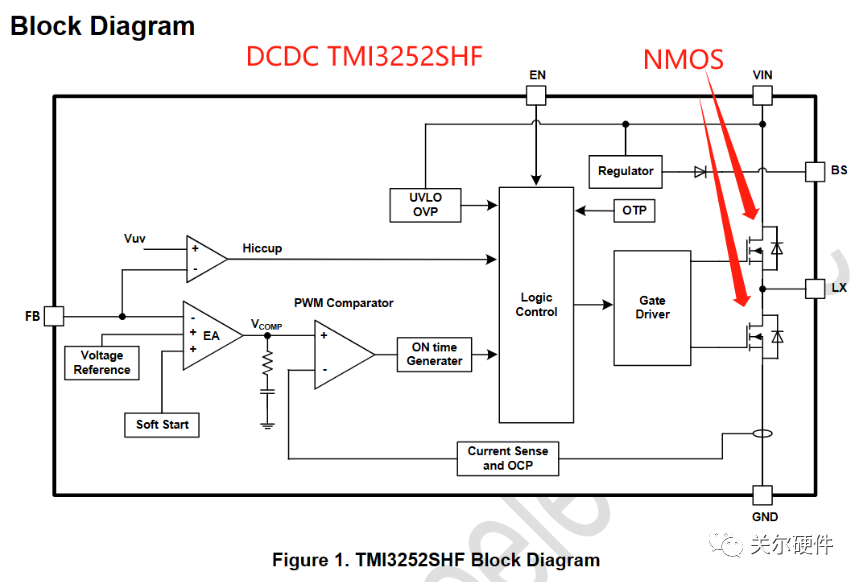

TMI3252SHF的上下管都是NMOS管,Vgs電壓為正時(shí)導(dǎo)通,即上管NMOS的S端為正,G端也要為正,且比S端還要高,因此電路需要BOOST電容。由于BOOST電容的充放電,及Vgs的電壓要大于某閾值,上管NMOS才會(huì)導(dǎo)通。當(dāng)Vgs小于閾值時(shí),上管NMOS就會(huì)關(guān)閉,就沒辦法達(dá)到100% Duty cycle。因此,該DCDC就會(huì)有Maximum Duty Cycle的參數(shù),如TMI3252SHF的maximum duty cycle是85%,即輸出電壓的最大值只能是輸入電壓的85%,還需要減去PMOS的壓降(電流乘以上管PMOS的Rds(on))。(note:TMI3252SHF是高壓輸入,輸入電壓范圍4.5V~18V。)

小結(jié),DCDC芯片有個(gè)Boost管腳的芯片,無法做到100% DutyCycle,因?yàn)橛蠧Boost電容(電容放電時(shí),導(dǎo)致Vgs電壓低于mos管導(dǎo)通閾值)。DCDC芯片上管使用PMOS時(shí),可以做到100% Duty Cycle。

-

ldo

+關(guān)注

關(guān)注

35文章

2257瀏覽量

155379 -

PMOS

+關(guān)注

關(guān)注

4文章

265瀏覽量

30216 -

buck電路

+關(guān)注

關(guān)注

28文章

487瀏覽量

47127 -

DCDC

+關(guān)注

關(guān)注

29文章

861瀏覽量

72481

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DCDC基礎(chǔ):輸入輸出電容的選擇及計(jì)算

運(yùn)放參數(shù)解析:輸入輸出電壓范圍

輸入輸出電壓差

7533和78L05這種LDO輸入輸出電壓的壓差有沒有限制

DC-DC降壓芯片有輸入輸出壓差范圍嗎

DC-DC降壓芯片是否有輸入輸出壓差范圍要求?

小白講解單片機(jī)GPIO輸入輸出

DC-DC降壓芯片的輸入輸出壓差范圍的要求

DCDC直流降壓型電壓變換原理詳解

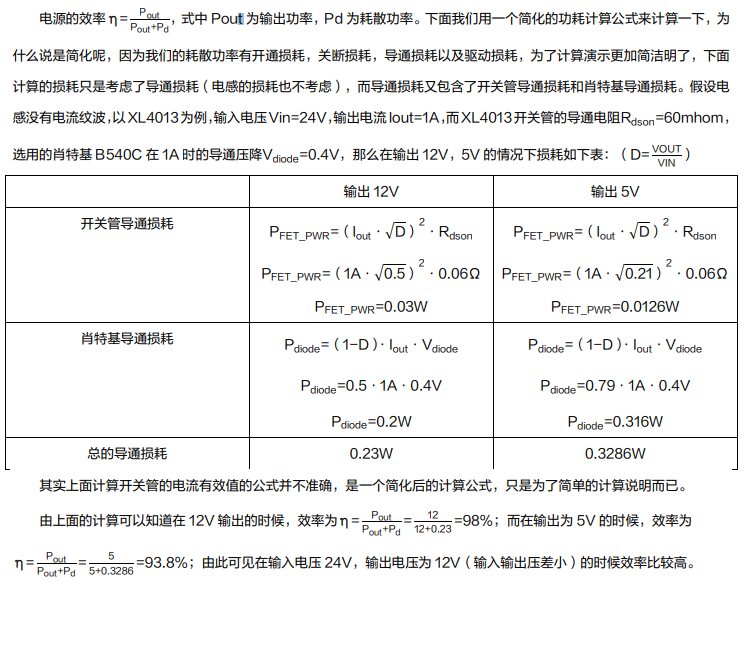

輸入輸出電壓差與效率的關(guān)系

降壓DCDC有輸入輸出電壓差嗎

降壓DCDC有輸入輸出電壓差嗎

評(píng)論