輸入輸出電壓差

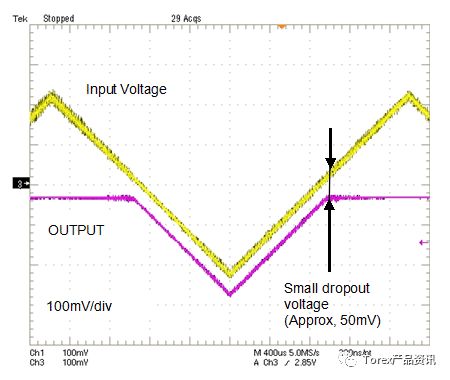

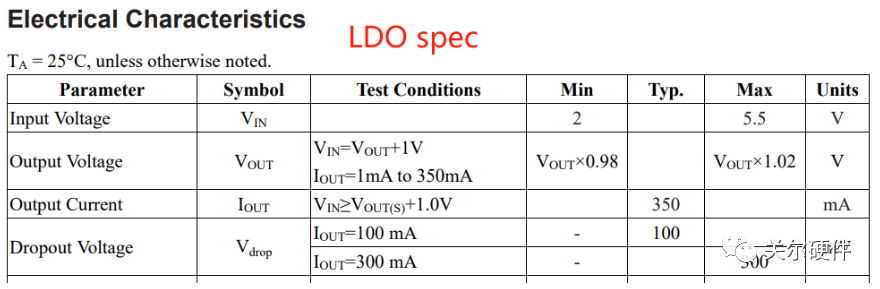

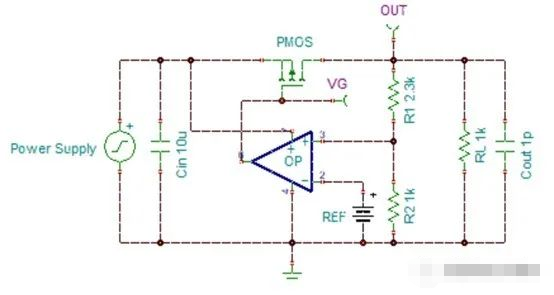

接下來(lái),介紹作為表示線性調(diào)整器基本性能之一的輸入輸出電壓差。特別是CMOS線性調(diào)整器,基本上都是輸入輸出電壓差非常小的LDO型。這是因?yàn)槠淠康脑谟诎央姵赜帽M為特征。圖7表示輸入電壓和輸出電壓的關(guān)系。很明顯輸入輸出電壓差非常小。

圖7 The Relationship between Input Voltage and Output Voltage(XC6209B302: Output Current=30mA)

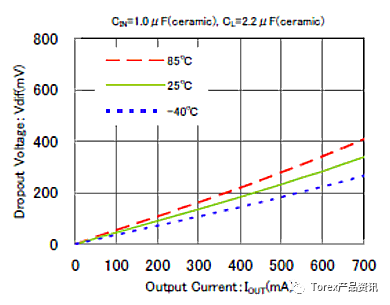

此外,按字面解釋輸入輸出電壓差是表示輸入電壓和輸出電壓的電壓差,由此說(shuō)明“只要輸入電壓和輸出電壓之間存在一定的電壓差即可汲取相對(duì)應(yīng)的電流”。作為參考,圖8表示XC6222x281的輸入輸出電位差特性例。例如把輸出電壓設(shè)定為3V的調(diào)整器,為了得到600mA的輸出電流,必須有300mV的輸入輸出電位差,即需要3.3V以上的輸入電壓。

圖8 Dropout Voltage vs. Output Current (XC6222x281)

最近的LDO,由于P溝道MOS驅(qū)動(dòng)器的驅(qū)動(dòng)性能不斷得到提高,只要有一定程度的輸入輸出電壓差,幾乎不存在任何電壓下降即可使輸出電流達(dá)到限定電流值。

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

53文章

8288瀏覽量

147140 -

ldo

+關(guān)注

關(guān)注

35文章

1953瀏覽量

154046 -

電壓

+關(guān)注

關(guān)注

45文章

5640瀏覽量

116311

原文標(biāo)題:【應(yīng)用指南--設(shè)計(jì)秘笈16】線性調(diào)整器基本性能之輸入輸出電壓差

文章出處:【微信號(hào):gh_454737165c13,微信公眾號(hào):Torex產(chǎn)品資訊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電壓調(diào)整器相關(guān)基礎(chǔ)知識(shí)運(yùn)用指南:線性調(diào)整器的相關(guān)技術(shù)

輸入輸出電壓差

XC6419低壓差CMOS雙路LDO電壓調(diào)整器芯片

TL494的電壓調(diào)整器技術(shù)分析

CMOS線性調(diào)整器的特征和分類

CMOS線性調(diào)整器的重要特性

電壓調(diào)整器之LDO低壓差線性穩(wěn)壓器

電力調(diào)整器是如何工作的

輸入電壓線性調(diào)整率、輸入電壓線性變化時(shí)對(duì)輸出電壓的相對(duì)影響?

輸入輸出電壓差與效率的關(guān)系

介紹作為表示線性調(diào)整器基本性能之一的輸入輸出電壓差

介紹作為表示線性調(diào)整器基本性能之一的輸入輸出電壓差

評(píng)論