"代碼即注釋,注釋即代碼"這個(gè)概念是如何形成的呢?記得之前看一些討論,程序員應(yīng)該如何寫(xiě)代碼的注釋,大家的意見(jiàn)很多,不過(guò)我只對(duì)兩句話記憶非常深刻:

(代碼)既然難寫(xiě),就應(yīng)難讀。

代碼本身就是注釋。

根據(jù)這兩句話意見(jiàn)呢,我們的代碼本身并不需要太多的注釋內(nèi)容。而應(yīng)該盡可能的通過(guò)合理的模塊與函數(shù)劃分、明確的信號(hào)命名、清晰的邏輯表達(dá)來(lái)替代繁瑣的注釋說(shuō)明,同時(shí)再借助比較完備的文檔進(jìn)行代碼的傳接。更何況呢坊間一直有一句傳聞:代碼易,人可替(我剛編的哈哈哈),所以久而久之我就養(yǎng)成了不寫(xiě)注釋的好習(xí)慣。

俗話說(shuō),程序員都有兩個(gè)最大的厭惡:一是別人不寫(xiě)注釋,二是別人讓自己寫(xiě)注釋。我估摸著哈,這都是和我一樣養(yǎng)成好習(xí)慣的盆友。不過(guò)不寫(xiě)注釋偶爾也會(huì)帶來(lái)一些惡果,最典型的就是隔一個(gè)月半個(gè)月要改自己的祖?zhèn)鞔a時(shí),得把代碼從頭理一遍的痛苦。當(dāng)然,代碼即注釋這句話不是本文的重點(diǎn),重點(diǎn)是后面的注釋即代碼。

注釋即代碼的思想是怎么來(lái)的呢?來(lái)自于兩個(gè)對(duì)本奪命腳本師影響頗深的事情。一件是verilog-mode的使用,這個(gè)工具的介入直接讓困擾我多年的模塊例化與互連問(wèn)題迎刃而解;另一件是前司開(kāi)發(fā)的RTL檢查工具,借助注釋生成的檢查代碼節(jié)約了驗(yàn)證大量的時(shí)間,因?yàn)槲易约菏球?yàn)證所以對(duì)此感受還是頗深的。腳本的目的無(wú)非是兩個(gè),提高效率與提高質(zhì)量,而以注釋生成代碼以小生多的思路,不僅大大的提升了工作的效率,也能夠保證生成代碼的高質(zhì)量,畢竟人會(huì)出錯(cuò)工具不會(huì)出錯(cuò)(除非是我自己和工具沖突了,此時(shí)必是工具有bug╭(╯^╰)╮)。

那么在樹(shù)立了注釋即代碼的思想后,我就沿著這個(gè)方向進(jìn)行了幾個(gè)腳本的開(kāi)發(fā)。

第一個(gè)是名叫g(shù)en_link的腳本,看這個(gè)名字就知道這是模仿verilog-mode中的自動(dòng)連線功能而開(kāi)發(fā)的RTL例化與互連工具。為什么會(huì)重復(fù)造輪子呢?說(shuō)來(lái)就比較曲折了,因?yàn)槲也恢纕erilog-mode是開(kāi)源的工具 ̄□ ̄||知道了這件事之后,我就轉(zhuǎn)而去研究了如何配置和使用該工具了,甚至還做了專欄。

第二個(gè)腳本是auto_assert,這個(gè)腳本和前司的借助注釋檢查代碼的工具思路是一致的,不過(guò)我在其中做了簡(jiǎn)化和一些功能的補(bǔ)充。最終完成的腳本能夠支持如下的功能:

1.信號(hào)的不定態(tài)檢查

2.信號(hào)在使能時(shí)的不定態(tài)檢查

3.仿真過(guò)程中信號(hào)的取值檢查

4.仿真過(guò)程中使能時(shí)信號(hào)的取值檢查

5.仿真過(guò)程中信號(hào)取值覆蓋率分析

6.仿真結(jié)束時(shí)信號(hào)結(jié)束值檢查

然后我就發(fā)現(xiàn)了這個(gè)腳本的致命問(wèn)題:這玩意會(huì)極大地增加設(shè)計(jì)的工作量!因?yàn)檫@個(gè)致命問(wèn)題的存在,后面雖然我還對(duì)其進(jìn)行了維護(hù),但是一般不會(huì)在工作中使用了,就算用也只用最基礎(chǔ)的不定態(tài)檢查和結(jié)束值檢查功能。

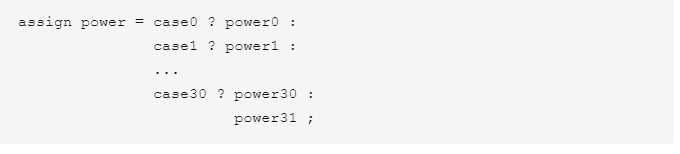

第三個(gè)腳本是auto_unfold,這個(gè)腳本的功能是對(duì)代碼中的相似代碼進(jìn)行循環(huán)展開(kāi),比如下面這種:

本來(lái)呢我以為這個(gè)是verilog-mode中的原生功能,后來(lái)才發(fā)現(xiàn)是前司內(nèi)部自己開(kāi)發(fā)的派生功能。然后我又沒(méi)有對(duì)其進(jìn)行進(jìn)一步開(kāi)發(fā)的能力,那能怎么辦呢?只好借助python開(kāi)發(fā)新的腳本然后嵌入到vim中了。

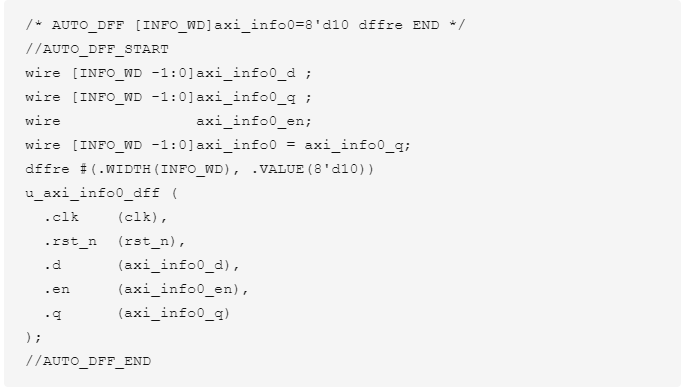

最后一個(gè)腳本是auto_dff,這個(gè)腳本我前幾天才寫(xiě)好的,寫(xiě)它的目的是啥呢?在前面的文章提到了dff例化風(fēng)格代碼,在實(shí)踐的過(guò)程中就會(huì)發(fā)現(xiàn)一個(gè)問(wèn)題,那就是每一個(gè)寄存器的例化和信號(hào)聲明寫(xiě)起來(lái)也是挺煩的。在某一個(gè)進(jìn)行進(jìn)行批量寄存器替換的夜晚,我突然感覺(jué)寫(xiě)這么多無(wú)效的寄存器代碼也非常的不能忍,所以開(kāi)發(fā)了這個(gè)腳本:

但是說(shuō)來(lái)非常的慚愧,寫(xiě)完這個(gè)腳本后我就很久沒(méi)有開(kāi)發(fā)代碼了,一直沒(méi)能好好的感受下效率提升的效果。

目前為止遵循“代碼即注釋,數(shù)值即代碼”思路開(kāi)發(fā)的腳本就是這4個(gè),以后再慢慢增加吧。

審核編輯:湯梓紅

-

代碼

+關(guān)注

關(guān)注

30文章

4891瀏覽量

70315 -

腳本

+關(guān)注

關(guān)注

1文章

397瀏覽量

28368 -

注釋

+關(guān)注

關(guān)注

0文章

11瀏覽量

6588

原文標(biāo)題:IC學(xué)霸筆記 | 代碼即注釋,注釋即代碼

文章出處:【微信號(hào):IC修真院,微信公眾號(hào):IC修真院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

麻煩問(wèn)下keil選中代碼后快速注釋為何在代碼左邊出現(xiàn)注釋符號(hào)

python基礎(chǔ):如何注釋代碼塊

用于代碼注釋生成的語(yǔ)法輔助機(jī)制設(shè)計(jì)

JAVA連接Oracle數(shù)據(jù)庫(kù)實(shí)代碼+詳細(xì)注釋

嵌入式系統(tǒng)設(shè)計(jì)中的注釋和調(diào)試代碼

python代碼中使用HTTP代理IP,demo注釋清晰

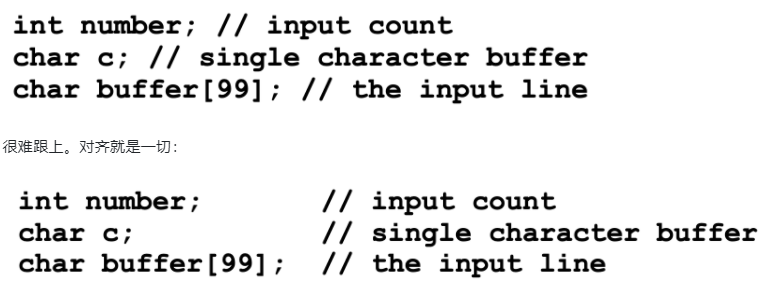

代碼編程規(guī)范之注釋風(fēng)格

代碼即注釋,注釋即代碼的概念是如何形成的

代碼即注釋,注釋即代碼的概念是如何形成的

評(píng)論