FPGA上電(Master)

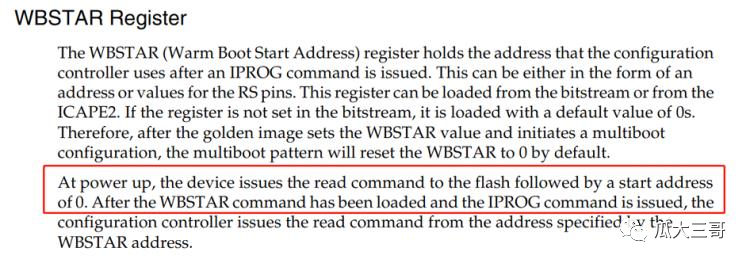

fpga 上電時,默認是從 flash 的 0x00 地址開始讀數據。如 UG470 文檔 page144 描述

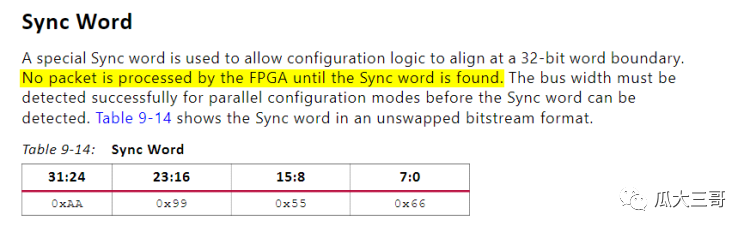

fpga 會從 0 開始讀,地址不斷自增,直到讀取到有效的同步字 sync word(0xAA995566),才認為接下來的內容是一個有效的 bin 文件內容的開始。讀到有效 sync word 后不會再繼續讀搜尋其他的 bin 文件。如 UG470 文檔 page81 描述:

幾種情況

只有一個 bit 文件,使用如下命令將該 bit 文件寫出轉換為 mcs 文件,并燒入 spi flash 中。

write_cfgmem-formatmcs-interfacespix4-size8-loadbit{up 0x400000./soc_top.bit}-filesoc_top_0x400000.mcs-force

該 bit 文件在 flash 中存放的起始地址是 0x400000 ,上電 fpga 能正常啟動,因為前部分的地址 0x000000-0x400000 之間都是無效數據, fpga 從 0x000000 地址開始讀,沒有有效的 sync word ,讀地址不斷增加,直到 0x400000 地址才會讀到同步字,然后就能正常的從 0x400000 開始配置。

有兩個 bit 文件,使用該命令轉換為一個 mcs 文件

write_cfgmem-formatmcs-interfacespix4-size8-loadbit{up0x000000./design1.bit

up0x400000./design2.bit}-filemixed.mcs-force

第一個 bit 文件放在 0x000000 地址,第二個放在 0x400000 地址,燒寫 flash ,上電后 fpga 從 deign1.bit

啟動,因為第一個 bit 在前面, fpga 上電后從 0x000000 地址開始讀,會先讀到 deign1.bit ,然后成功地從deign1.bit 初始化。

若把 mcs 文件中關于 deign1.bit 的 FDRI data 的內容手動改為其他值,使得配置的時候會出現 CRC 校驗錯誤, deign2.bit 相關的內容不變,燒寫進flash,上電, FPGA 無法正常配置數據,既不會從deign1.bit啟動,也不能從deign2.bit 啟動,這是因為第一個bit在前面, fpga 上電后從 0x000000 地址開始讀,會先讀到 deign1.bit ,然后從 deign1.bit 開始初始化,但是會發生CRC錯誤,然后又fallback 回 0 地址讀,依然是讀到 design1.bit 的數據,還是 CRC 錯誤,最后發生配置失敗。

若只把 mcs 文件中關于 deign1.bit 的 sync word 的內容手動改為其他值,比如 0xAA997866 ,deign2.bit 相關的內容不變,燒寫進 flash 上電, FPGA 成功從 deign2.bit 啟動。這是因為第一個 bit 在前面, fpga 上電后從0x000000 地址開始讀,讀到 deign1.bit 的 sync word 為 0xAA997866 時,發現不是有效的 sync word ,不會判斷接下來的內容是屬于一個有效的配置文件,于是繼續自增地址往上讀,直到讀到 0x400000 地址后面,成功讀到 design2.bit 的 sync word ,發現有效,然后從 deign2.bit 開始初始化。這樣就跳過了前面 deign1.bit 的內容。

bitstream 約束

對bit流進行壓縮

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

打開看門狗功能

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

如果加載 Update_Image 配置文件失敗后,沒有返回加載 Golden_Image ,則會根據指定的時間啟動看門狗,強制返回加載 Golden_Image 。

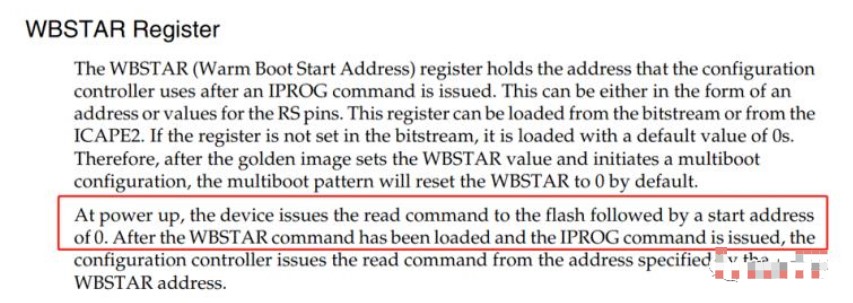

生成 bit 文件的頭部添加 IPROG 命令和設置 WBSTAR 的命令

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

配置時執行到 IPROG 命令后,會直接跳轉到指定的地址中繼續執行配置。可用于 Golden_Image 中設置為跳轉到 Update_Image 啟動。其實加不加這個約束,生成的bit流中的頭部,都會有 IPROG 和設置 WBSTAR 的相關命令的占位空間,只是不加該約束時, IPROG 的位置會由 000000 替代, NOP 指令,只是空的占位符;而寫 WBSTAR 寄存器的指令依然存在,但是寫 WBSTAR 的值卻是 0 。

-

FPGA

+關注

關注

1646文章

22068瀏覽量

619529 -

FlaSh

+關注

關注

10文章

1682瀏覽量

152075 -

Xilinx

+關注

關注

73文章

2185瀏覽量

125626 -

文件

+關注

關注

1文章

584瀏覽量

25417 -

命令

+關注

關注

5文章

742瀏覽量

22930

原文標題:Xilinx FPGA 從spi flash啟動配置數據時的地址問題

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于SPI FLASH的FPGA多重配置

FX3從SPI啟動并配置FPGA如何分離SPI閃存

怎么使用SPI閃存啟動選項實現FPGA配置文件的故障安全升級?

在BPI快速模式下配置FPGA無法從Flash啟動的解決辦法?

如何確定SPI Flash中FPGA配置的大小

可以從Virtex 6控制Xilinx Platform Flash XL?

使用高速SPI Nor Flash的FPGA配置

Xilinx7系列基于PCIe的設計如何滿足PCIe啟動時間的要求

FPGA配置– 使用JTAG是如何燒寫SPI/BPI Flash的?

基于FPGA 的SPI Flash 控制器設計及驗證

采用Xilinx FPGA的AFE79xx SPI啟動指南

Xilinx FPGA從spi flash啟動配置數據時的地址問題

Xilinx FPGA從spi flash啟動配置數據時的地址問題

評論