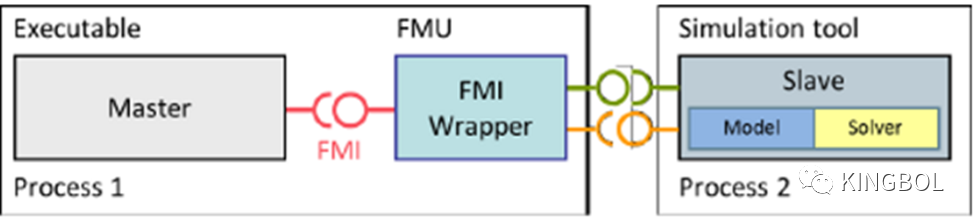

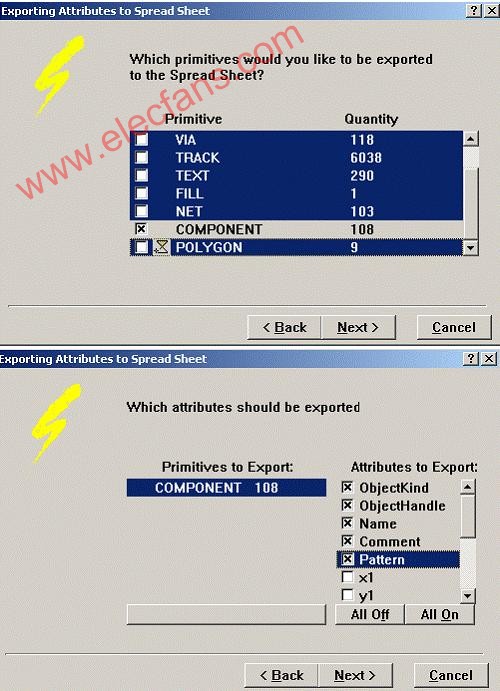

FMI聯(lián)合仿真為聯(lián)合仿真環(huán)境中仿真工具的耦合提供了接口標(biāo)準(zhǔn)。子系統(tǒng)之間的數(shù)據(jù)交換僅限于離散的通信點(diǎn)。在兩個(gè)通信點(diǎn)之間的時(shí)間內(nèi),子系統(tǒng)由各自的求解器獨(dú)立求解。主要算法控制子系統(tǒng)之間的數(shù)據(jù)交換和所有仿真求解器(子)的同步。

使用工具耦合方法進(jìn)行聯(lián)合仿真:在工具耦合方法中,F(xiàn)MU實(shí)現(xiàn)將FMI函數(shù)調(diào)用包裝到仿真工具提供的API調(diào)用中。除了FMU之外,還需要仿真工具來(lái)運(yùn)行一個(gè)聯(lián)合仿真,如圖1所示。

*Figure 1 *Cosimulation with tool coupling on a single computer

01

FMU的導(dǎo)出

1. 在SaberRD中創(chuàng)建設(shè)計(jì)

在將Saber設(shè)計(jì)導(dǎo)出到FMU之前,必須在SaberRD中創(chuàng)建Saber原理圖設(shè)計(jì)。有關(guān)如何創(chuàng)建Saber原理圖設(shè)計(jì)的信息,請(qǐng)參見(jiàn)SaberRD設(shè)計(jì)創(chuàng)建用戶(hù)指南中的創(chuàng)建設(shè)計(jì)。

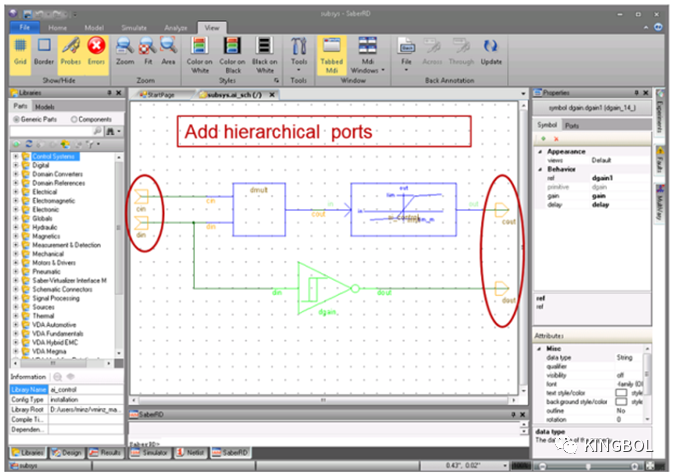

2. 為輸入和輸出添加分層端口

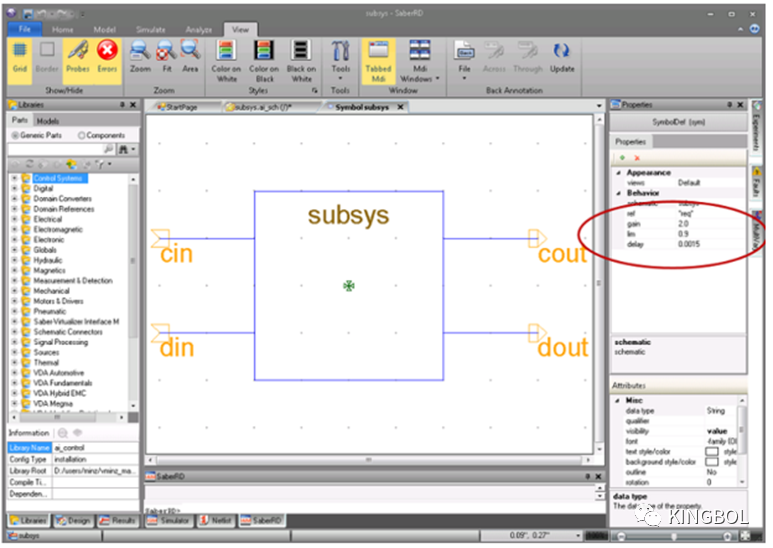

*為了將Saber設(shè)計(jì)導(dǎo)出到FMU,必須在設(shè)計(jì)中至少定義一個(gè)分層端口。您必須在需要導(dǎo)出為FMU中的輸入/輸出端口的節(jié)點(diǎn)上附加一個(gè)層次結(jié)構(gòu)端口,如圖2所示。

*Figure 2 *Adding hierarchical ports on schematic

*從部件庫(kù)中的Schematic Connectors類(lèi)別中選擇適當(dāng)?shù)亩丝诜?hào),并將其連接到需要導(dǎo)出到FMU的原理圖節(jié)點(diǎn)。如果是離散端口和模擬控制端口,請(qǐng)將分級(jí)輸入連接器連接到輸入端口,將分級(jí)輸出連接器連接到輸出端口。對(duì)于物理模擬端口,如電氣和液壓端口,連接分層模擬連接器。

*注意:將錯(cuò)誤的層次連接器連接到節(jié)點(diǎn)將導(dǎo)致FMU導(dǎo)出失敗。在原理圖中添加端口連接器的順序很重要,因?yàn)樵趯?dǎo)出的FMU的modelDescription.xml中定義FMU端口時(shí)也使用相同的順序。

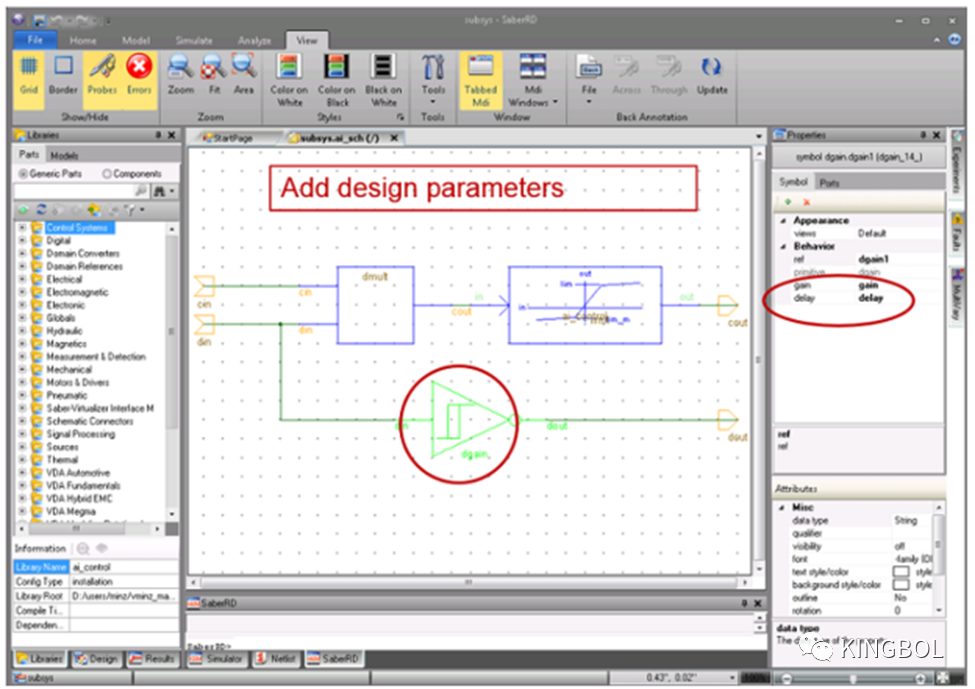

3. 在原理圖中增加設(shè)計(jì)參數(shù)(可選)

*對(duì)于任何需要作為設(shè)計(jì)參數(shù)暴露給父模擬器以便在聯(lián)合模擬開(kāi)始時(shí)對(duì)其進(jìn)行修改的模型參數(shù),都應(yīng)該在原理圖上添加設(shè)計(jì)參數(shù)。選擇需要作為模型屬性網(wǎng)格上的參數(shù)導(dǎo)出的屬性,并將其值更改為所需的名稱(chēng),該名稱(chēng)將在創(chuàng)建層次符號(hào)時(shí)用作層次參數(shù)。如圖3所示。

*Figure 3 *Adding design parameters on schematic

*注意:只有標(biāo)量、整數(shù)和字符串類(lèi)型的屬性可以導(dǎo)出為FMU參數(shù)。復(fù)合類(lèi)型的模型參數(shù),如MAST結(jié)構(gòu)、數(shù)組、VHDL-AMS記錄和向量不允許作為FMU導(dǎo)出的設(shè)計(jì)參數(shù)。

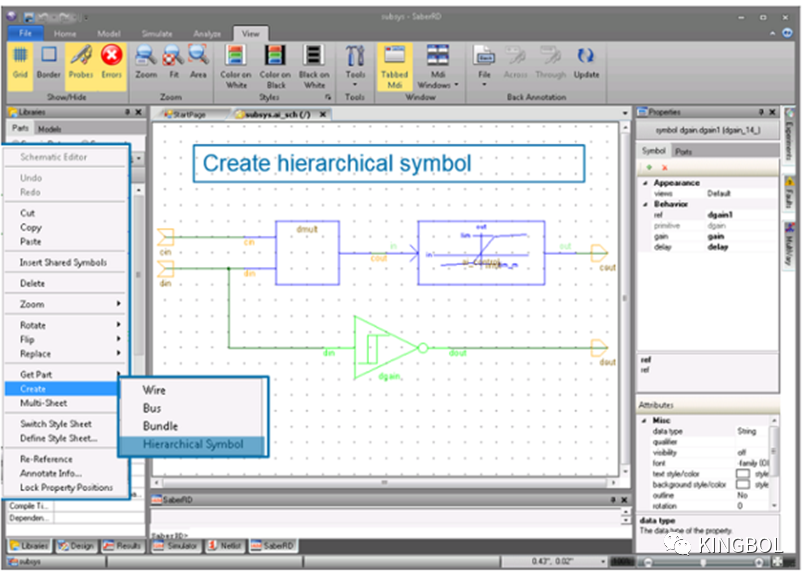

4.為Saber原理圖創(chuàng)建層次符號(hào)

*一旦Saber設(shè)計(jì)的層次原理圖準(zhǔn)備好了,在將其導(dǎo)出到FMU之前,需要使用它的層次符號(hào)。

*要?jiǎng)?chuàng)建分層符號(hào),右鍵單擊原理圖打開(kāi)原理圖編輯器Schematic Editor彈出菜單,單擊Create下拉菜單,選擇分層符號(hào)Hierarchical Symbol。

*注意:層次符號(hào)的名稱(chēng)必須與Saber設(shè)計(jì)相同。

*Figure 4 *Creating hierarchical symbol for schematic

** 5.編輯層次符號(hào)(可選 )**

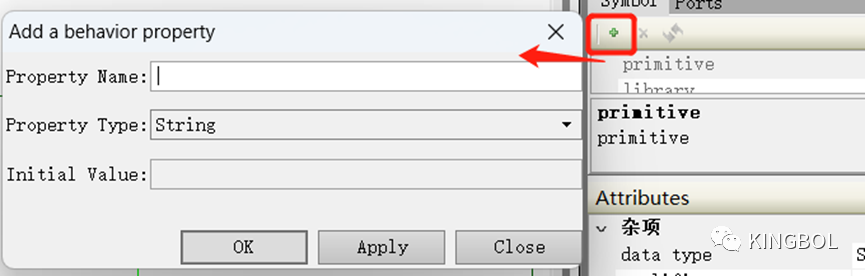

*如果分層設(shè)計(jì)有任何設(shè)計(jì)參數(shù)或物理模擬端口,生成的符號(hào)需要手動(dòng)更新,如下所示:在分層符號(hào)上添加設(shè)計(jì)參數(shù):

*打開(kāi)符號(hào)編輯器并加載生成的符號(hào)。在符號(hào)屬性網(wǎng)格上,添加之前在原理圖中添加的所有設(shè)計(jì)參數(shù),并為它們分配適當(dāng)?shù)闹担鐖D5所示。這些屬性可以在父模擬器開(kāi)始共同模擬時(shí)被更改。

Figure 5**Add design parameters on symbol

*更新分層符號(hào)上的物理端口方向和類(lèi)型:對(duì)于離散和模擬控制端口,在創(chuàng)建Saber設(shè)計(jì)原理圖時(shí),在端口連接器上定義輸入/輸出信息。這些類(lèi)型的端口不需要進(jìn)一步處理。但是,模擬物理端口能量保守,如電氣或液壓端口有兩個(gè)組成部分,單個(gè)端口上的通過(guò)變量和跨變變量。而且,它們沒(méi)有方向信息。

*為了能夠?qū)⑽锢矶丝趯?dǎo)出到FMU,必須提供物理端口的方向和類(lèi)型信息。

要提供方向和類(lèi)型信息,請(qǐng)?jiān)诜?hào)編輯器中打開(kāi)符號(hào)并選擇物理端口。

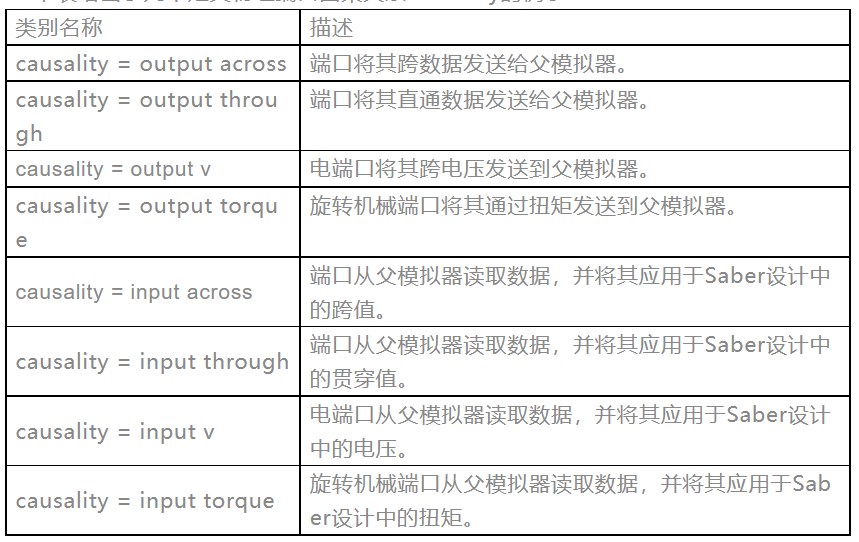

*單擊“ Properties”窗格上的“Add a behavior property”圖標(biāo),在Property Name字段中,輸入因果關(guān)系causality,在Initial Value中,提供其方向和類(lèi)型信息,用空格分隔,如下所示:

*指定模擬端口方向:第一個(gè)值指定端口方向,可以是輸入,也可以是輸出。輸入意味著端口從父模擬器讀取值,而輸出意味著端口將數(shù)據(jù)發(fā)送到父模擬器。默認(rèn)情況下,方向被設(shè)置為輸出,這意味著所有物理端口都將數(shù)據(jù)發(fā)送到父模擬器。

模擬端口類(lèi)型:第二個(gè)值表示物理端口的數(shù)據(jù)類(lèi)型。要么跨過(guò)要么穿過(guò)。value, across表示端口與父模擬器交換它的across值,而through表示端口與父模擬器交換它的through值。您還可以使用在MAST或VHDL-AMS中定義的物理單元來(lái)指定端口類(lèi)型。

*添加因果方式的方法如圖6所示:

Figure 6**Adding causality

*下表給出了幾個(gè)定義物理端口因果關(guān)系causality的例子:

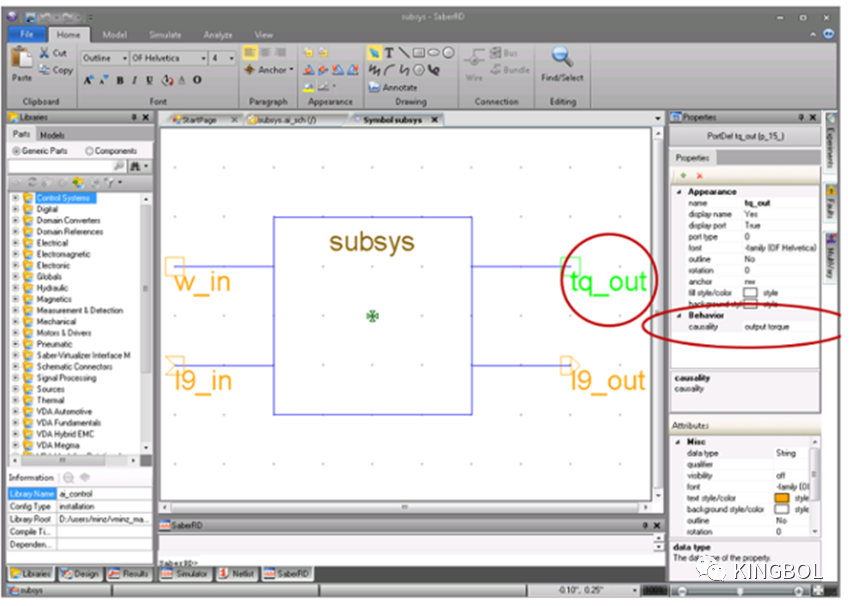

*更新后的物理端口causality屬性如圖7所示:

*Figure 7 **Adding causality *on physical port on symbol

6.驗(yàn)證SaberRD設(shè)計(jì)

*當(dāng)Saber設(shè)計(jì)就緒時(shí),在將其導(dǎo)出到FMU之前,驗(yàn)證它在SaberRD中正確工作。

這可以通過(guò)創(chuàng)建一個(gè)Saber測(cè)試來(lái)完成,如下所示:

在層次符號(hào)的輸入端口上應(yīng)用刺激,并將適當(dāng)?shù)呢?fù)載連接到層次符號(hào)的輸出端口。

運(yùn)行直流和瞬態(tài)分析。

確保在模擬過(guò)程中沒(méi)有錯(cuò)誤。

如果模擬成功,請(qǐng)檢查模擬結(jié)果是否正確。

如果仿真結(jié)果正確,Saber設(shè)計(jì)就可以導(dǎo)出到FMU。

7.導(dǎo)出一個(gè)Saber設(shè)計(jì)到FMU

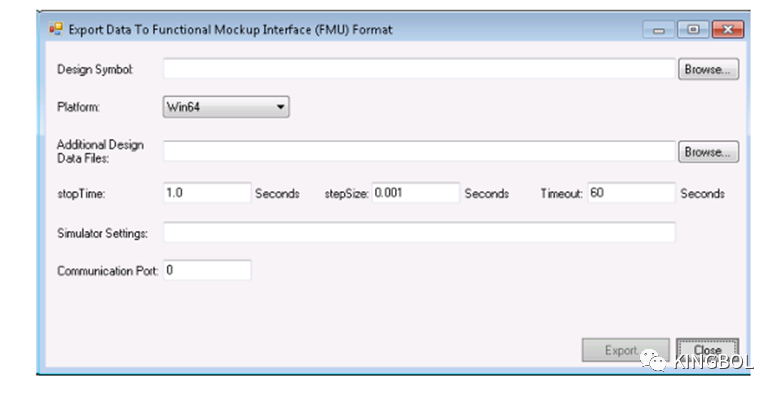

在SaberRD中選擇“File > Export”,選擇“Function Mockup Interface (FMI)....”系統(tǒng)彈出“Export Data To Functional Mockup Interface (FMU) Format”對(duì)話(huà)框,如圖8所示。

Figure 8**Saber FMU export

“Export Data To Functional Mockup Interface (FMU) Format”對(duì)話(huà)框:

Design Symbol: 指定要導(dǎo)出的Saber設(shè)計(jì)的層次符號(hào)名稱(chēng),包括其位置路徑。符號(hào)必須是等級(jí)符號(hào)。與符號(hào)相關(guān)聯(lián)的原理圖文件也應(yīng)該在同一目錄中。這個(gè)字段是強(qiáng)制性的,因?yàn)閷哟畏?hào)是“將Saber設(shè)計(jì)導(dǎo)出到FMU”所必需的。

Platform:指定EMU導(dǎo)出到的系統(tǒng)。支持的系統(tǒng)為win64,win32, linux64, linux32。可以任意選擇其中一個(gè)平臺(tái),默認(rèn)是win64。

Additional Design Data Files:除了模型( .sin, .vhdl), symbols ( .ai_sym)和schematic ( .ai_sch),可在此指定所有其他文件,例如TLU(table Look-up)模型的外部數(shù)據(jù)文件( .ai_dat),這些文件需要使用SaberHDL模擬器運(yùn)行模擬。如果不需要其他設(shè)計(jì)數(shù)據(jù)文件,該字段可以留空。

*stopTime: 指定FMI聯(lián)合仿真的停止時(shí)間。默認(rèn)值是1.0秒。

*stepSize:指定聯(lián)合仿真期間的通信步長(zhǎng)。它必須小于stopTime。默認(rèn)值是0.001秒。

*Timeout:指定了在共同模擬中完成以下所有任務(wù)的最大時(shí)間限制,在此時(shí)間之后,如果沒(méi)有完成,父模擬器將失敗。

*在父模擬器和子模擬器之間建立連接。

*完成一個(gè)單獨(dú)的溝通步驟,包括以下任務(wù):

*父模擬器將輸入數(shù)據(jù)發(fā)送給子模擬器。

*子模擬器完成給定步長(zhǎng)的模擬。

*子模擬器將輸出數(shù)據(jù)發(fā)送回父模擬器。

注意:

1默認(rèn)值為60秒。2.建議增加復(fù)雜Saber設(shè)計(jì)的超時(shí)值,以避免在協(xié)同仿真過(guò)程中出現(xiàn)不必要的故障,因?yàn)橥瓿梢粋€(gè)時(shí)間點(diǎn)的仿真可能需要更長(zhǎng)的時(shí)間。

- Simulator Settings:指定SaberHDL模擬器設(shè)置。該字段是可選的,默認(rèn)模擬器設(shè)置,如tniter(目標(biāo)迭代數(shù))和集成順序從SaberHDL模擬器。

在以下情況下,需要指定模擬器設(shè)置:

*特定模擬器設(shè)置以獲得更好的收斂性:在一些復(fù)雜的Saber設(shè)計(jì)中,可能需要一些特定的高級(jí)模擬器設(shè)置以獲得更好的收斂性。在將設(shè)計(jì)導(dǎo)出到FMU之前,需要設(shè)置這樣的模擬器設(shè)置。在協(xié)同仿真過(guò)程中使用這些設(shè)置來(lái)提高收斂性能。例如: dc; tr -tend 1 -tstep 1 us -tniter 10 -order 1

*Saber設(shè)計(jì)沒(méi)有直流解決方案:如果Saber設(shè)計(jì)沒(méi)有直流解決方案,并且需要-trip zero選項(xiàng)來(lái)啟動(dòng)瞬態(tài)模擬,則可以在模擬器設(shè)置中指定。例如tr -tend 1-tstep 1 ms-trip zero。選項(xiàng) -trip zero允許導(dǎo)出的FMU在共同模擬期間跳過(guò)直流分析。

*保存SaberHDL結(jié)果:大多數(shù)FMI模擬器刪除FMU解壓縮的臨時(shí)目錄。默認(rèn)情況下,SaberHDL在這個(gè)臨時(shí)目錄下的resources子目錄中運(yùn)行模擬,在共同模擬完成后,SaberHDL結(jié)果將被刪除。如果您想保存SaberHDL模擬結(jié)果,可以使用選項(xiàng)-wdir保存SaberHDL結(jié)果。例如,如果你想將Saber結(jié)果保存在一個(gè)名為saber_results的目錄中,設(shè)置應(yīng)該是:dc;Tr-tend 1-tstep 1u-wdir saber_results。

*在FMU中創(chuàng)建默認(rèn)實(shí)驗(yàn):如果你想在modelDescription.xml中創(chuàng)建默認(rèn)實(shí)驗(yàn)定義,那么可以使用模擬器設(shè)置。例如,如果你想創(chuàng)建一個(gè)stopTime=5.0, stepSize=0.01的默認(rèn)實(shí)驗(yàn)定義,那么模擬器設(shè)置應(yīng)該是: dc; tr -tend 5.0 -tstep 0.001.。注意,通信步長(zhǎng)是模擬器設(shè)置中初始時(shí)間步長(zhǎng)的10倍。

*Communication Port:指定在共同模擬期間父模擬器和子模擬器之間用于通信的TCP/IP端口。默認(rèn)值是0,當(dāng)使用它時(shí),導(dǎo)出的FMU自動(dòng)找到下一個(gè)可用端口。但是,可以指定一個(gè)特定的端口來(lái)建立通信。

02

限制

以下是FMI 2.0 Co-Simulation接口下FMU導(dǎo)出的限制:

*導(dǎo)出的Saber FMU僅支持win64、win32、linux64和linux32平臺(tái)。

*FMU中只支持將標(biāo)量數(shù)字、MAST中的字符串、real、integer和VHDL-AMS中的字符串類(lèi)型的參數(shù)導(dǎo)出為參數(shù)。

*只有一些預(yù)定義的離散端口,如MAST中的state nu, state logic_4, state fmi_boolean和VHDL-AMS中的signal std_logic支持導(dǎo)出到FMU。

*只有一些連續(xù)的因果端口,如MAST中的輸入,ref nu, output, var nu和VHDL-AMS中的quantity in/out real支持導(dǎo)出到FMU。

*僅支持以下預(yù)定義物理端口導(dǎo)出到FMU。

*頭文件中定義的所有物理引腳.sin在MAST語(yǔ)言中: electrical, magnetic,thermal_k,thermal_c,rotational_vel,rotational_ang,translational_pos,translational_vel,light,hyd_mks,pneumatic.

*VHDL-AMS中定義的性質(zhì): electrical, magnetic, rotational, rotational_velocity, translational, translational_v, fluidic, thermal, thermal_c, radiant.

*物理端口默認(rèn)只導(dǎo)出一個(gè)組件到FMU。物理端口有兩個(gè)組件,跨變量和通過(guò)變量。但是,默認(rèn)情況下,只有一個(gè)組件被導(dǎo)出到FMU。這是通過(guò)在符號(hào)端口上添加因果關(guān)系行為來(lái)實(shí)現(xiàn)的,例如,交叉輸入或通過(guò)輸出。如果您希望將兩個(gè)組件都導(dǎo)出到FMU,在導(dǎo)出FMU之前,請(qǐng)使用ai_conversion庫(kù)中的域轉(zhuǎn)換模型將跨變量和通過(guò)變量轉(zhuǎn)換為Saber設(shè)計(jì)中的控制變量端口。這將跨組件和通過(guò)組件導(dǎo)出到FMU。

*沒(méi)有提供源代碼。

*導(dǎo)出的FMU不提供輸出變量的導(dǎo)數(shù)。

*在一個(gè)設(shè)計(jì)中只能實(shí)例化一個(gè)Saber FMU。

*導(dǎo)出的FMU不能序列化FMU狀態(tài)。

*導(dǎo)出的FMU不能使用內(nèi)存管理功能。

03

Saber FMU實(shí)例

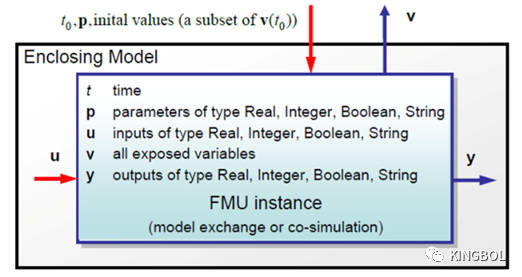

Saber FMU實(shí)例概述

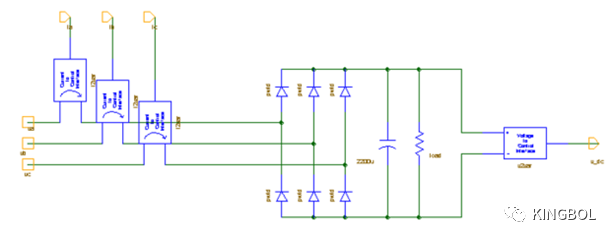

圖9顯示了三相整流器的Saber設(shè)計(jì)示例。

設(shè)計(jì)可以在SaberRD安裝目錄examples/OtherExamples/FMI2.0/export_cs/ precfier_3p中找到。

本設(shè)計(jì)有兩個(gè)設(shè)計(jì)參數(shù):

*von:六個(gè)開(kāi)關(guān)器件的導(dǎo)通壓降。默認(rèn)值是0.7V。

load:輸出級(jí)的電阻性負(fù)載。默認(rèn)為0.5歐姆。

本設(shè)計(jì)有三個(gè)電壓輸入接口:

*va,vb,vc:這三個(gè)輸入都是物理電結(jié)點(diǎn),沒(méi)有方向。我們希望從父模擬器獲得這些端口的跨接電壓輸入。因此,在這三個(gè)符號(hào)端口上需要一個(gè)屬性,與輸入值之間的因果關(guān)系。

本設(shè)計(jì)有四個(gè)輸出端口:

*ia,ib,ic:這三個(gè)節(jié)點(diǎn)將相電流發(fā)送回父模擬器。它們是連續(xù)的模擬輸出,具有輸出的因果關(guān)系,不需要在這些符號(hào)端口上添加特定的因果關(guān)系

*v_dc:這個(gè)節(jié)點(diǎn)是整流器的輸出電壓,它已經(jīng)從兩個(gè)差分電壓轉(zhuǎn)換成一個(gè)控制信號(hào)。它有輸出的方向,所以不需要為它定義因果關(guān)系

Figure9**Three-Phase Rectifier Example

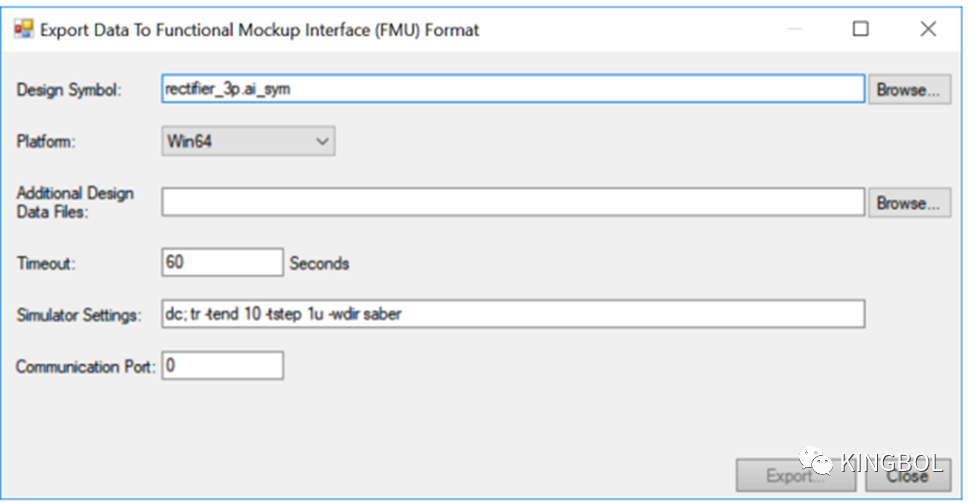

輸出Saber 示例設(shè)計(jì)到FMU

要將Saber示例設(shè)計(jì)導(dǎo)出到FMU,請(qǐng)執(zhí)行以下步驟:

1.將rectifier_3p示例從安裝文件夾復(fù)制到本地目錄。

2.調(diào)用SaberRD并打開(kāi)這個(gè)設(shè)計(jì)。

3.導(dǎo)出rectifier_3p_saberhdl.fmu。

*選擇File->Export,選擇Functional Mockup Interface (FMI)....系統(tǒng)彈出“Export Data To Functional Mockup Interface (FMU) Format”對(duì)話(huà)框。

*選擇rectifier_3p.ai_sym為Design Symbol。

*Simulation Settings設(shè)置為:dc;tr -tend 10-tstep 1u -wdir saber。

*單擊Export,rectifier_3p saberhdl.fmu在同一目錄下生成

Figure 10**Export Data To Functional Mockup Interface (FMU) Format

仿真導(dǎo)出的Saber FMU

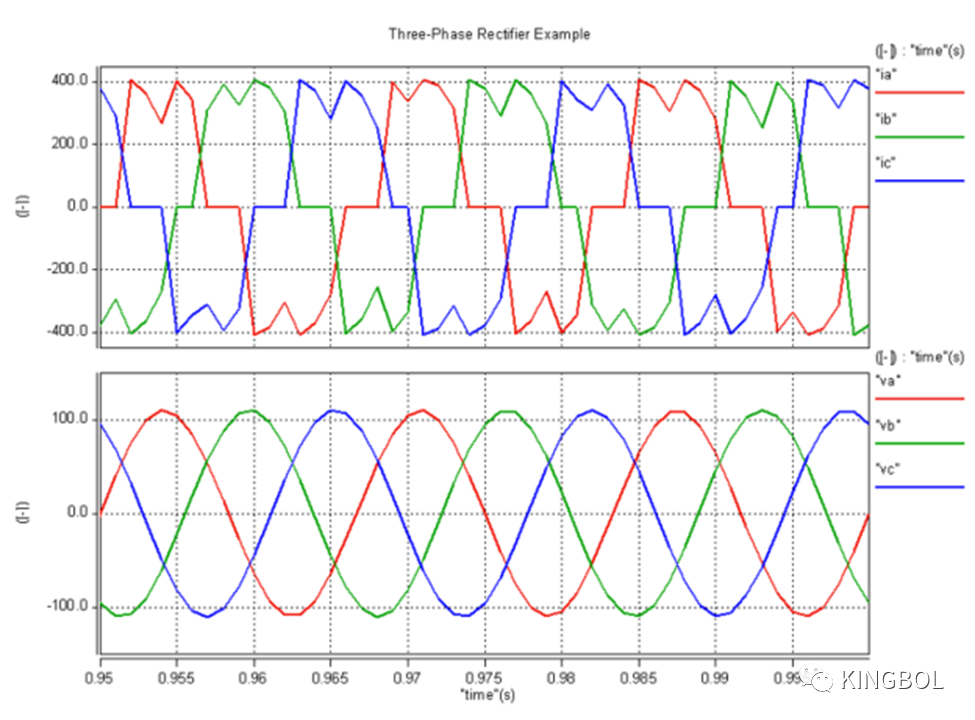

*任何FMI模擬器都可以用來(lái)測(cè)試導(dǎo)出的FMU,rectifier_3p. fmu。

*在FMI標(biāo)準(zhǔn)頁(yè)面上有許多可用的工具:https://fmi-standard.org/download

*在這個(gè)例子中,使用了一個(gè)免費(fèi)的模擬器fmuChecker。

*要運(yùn)行這個(gè)示例,請(qǐng)執(zhí)行以下步驟:

1.將環(huán)境變量SABER_FMU_SOLVER設(shè)置為Saber的安裝路徑。例如,C:SynopsysSaberRD64P-2019.06.

2.運(yùn)行64位版本的fmuChecker: fmuCheck.win64.exe -e log.txt -i v_3p.csv -o result.csv -s 2 -h 1e-3 -n 0 rectifier_3p_saberh.fmu

它運(yùn)行瞬態(tài)模擬2秒,通信步長(zhǎng)為1e-3。輸出信息保存在log.txt文件中,仿真結(jié)果保存在result.csv文件中。

3.在任何兼容的波形查看器(如Scope)中打開(kāi)result.csv文件。

*結(jié)果如圖11所示。

*Figure 11 *Three-Phase Rectifier Results

-

連接器

+關(guān)注

關(guān)注

99文章

15067瀏覽量

138743 -

仿真器

+關(guān)注

關(guān)注

14文章

1027瀏覽量

84621 -

VHDL語(yǔ)言

+關(guān)注

關(guān)注

1文章

113瀏覽量

18406 -

模擬器

+關(guān)注

關(guān)注

2文章

888瀏覽量

43849 -

AMS

+關(guān)注

關(guān)注

10文章

212瀏覽量

87442

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何在Protel軟件中導(dǎo)出元件清單

SaberRD導(dǎo)入FMU的步驟概述

matlab中導(dǎo)出數(shù)據(jù)為txt文件~~ 怎么導(dǎo)出二維數(shù)組中的一列

關(guān)于PCB EDITOR 中導(dǎo)入DXF文件的問(wèn)題

怎么從一個(gè)項(xiàng)目的文件中導(dǎo)出原理圖庫(kù)和pcb庫(kù)

如何使用VSCODE編輯Keil中導(dǎo)出的代碼

如何從keil中導(dǎo)出內(nèi)存數(shù)據(jù)到matlab中?

如何從PADS-LAYOUT中導(dǎo)出BOM清單方法

如何從Protel99文件中導(dǎo)出坐標(biāo)數(shù)據(jù)

LabVIEW中導(dǎo)出波形圖或圖表至文件

OrCAD將原理圖中導(dǎo)出并保存至器件庫(kù)的詳細(xì)步驟

在SaberRD中導(dǎo)出FMU的步驟詳解

在SaberRD中導(dǎo)出FMU的步驟詳解

評(píng)論