1 簡介

SPI(Serial Peripheral Interface) 是串行外設(shè)接口的簡稱,是微控制器(MCU)與外圍設(shè)備通信最常見的接口,常見的外圍設(shè)備包含ADC/DAC、傳感器以及存儲器等。

2 SPI的特點

- SPI有哪些引腳?

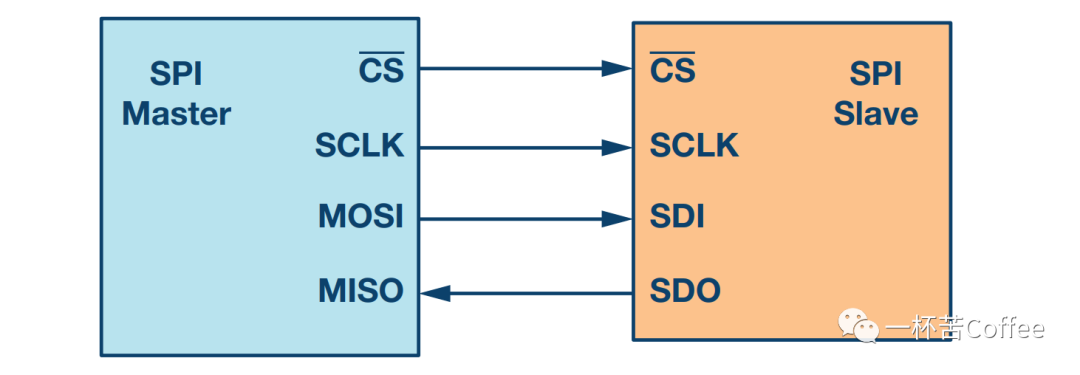

SPI是一種同步全雙工通信方式,我們一般采用四線SPI接口,具體包含以下這些信號:

- 時鐘信號(SPI Clock,SCLK)

- 片選信號(Chip Select,SC)

- 主機輸出,從機輸入(Master Output Slave Inpit,MOSI或DO)

- 主機輸入,從機輸出(Master Inpit Slave Output,MISO或DI)

其中每個PIN腳都有其特定的功能,具體見下:

| 信號名稱 | 功能描述 |

|---|---|

| 時鐘信號CLK | 主機用于產(chǎn)生時鐘信號,主機和從機之間的數(shù)據(jù)同步。 |

| 片選信號CS | 用于選擇從機,常低電平有效。 |

| 數(shù)據(jù)信號(MISO) | 從機將數(shù)據(jù)發(fā)送給主機。 |

| 數(shù)據(jù)信號(MOSI) | 主機將數(shù)據(jù)發(fā)送給從機。 |

- SPI信號與I2C信號有哪些差異?

SPI接口與I2C接口有很明顯的不同,具體體現(xiàn)在以下幾個方面:

- SPI時鐘的頻率比I2C時鐘頻率更高。

- SPI采用四線制,I2C采用二線制。

- SPI只能有一個主機,I2C可以有多個主機(總線仲裁機制)。

- SPI信號數(shù)據(jù)傳輸過程?

SPI通信需要的時鐘由主機(Master)產(chǎn)生,且主機通過片選信號來選擇通信的設(shè)備(低電平有效,由主機主動拉低)。SPI能同時進行數(shù)據(jù)的發(fā)送(MOSI)與接收(MISO),且SPI允許用戶靈活選擇時鐘的上升沿/下降沿進行數(shù)據(jù)的采樣和移位。

3 時鐘極性和時鐘相位

- 什么是時鐘極性(CPOL)和時鐘相位(CPHA)?

在SPI通信中。時鐘極性和時鐘相位是可以由用戶進行設(shè)定的。

時鐘極性(CPOL) :決定了時鐘信號在空閑時的狀態(tài)(高電平或者低電平)。

時鐘相位(CPHA) :決定了是在上升沿或者下降沿進行采樣和移位。

| SPI | CPOL | COHA | 時鐘極性(空閑) | 時間(采樣/移位) |

|---|---|---|---|---|

| 0 | 0 | 0 | 低電平 | 上升沿采樣、下降沿移出 |

| 1 | 0 | 1 | 低電平 | 下升沿采樣、上降沿移出 |

| 2 | 1 | 1 | 高電平 | 下升沿采樣、上降沿移出 |

| 3 | 1 | 0 | 高電平 | 上升沿采樣、下降沿移出 |

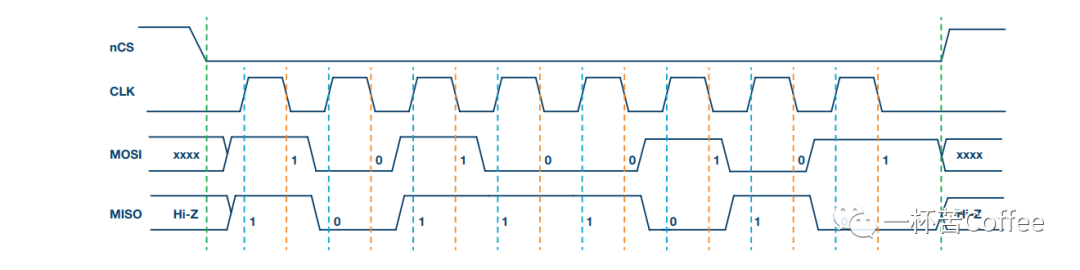

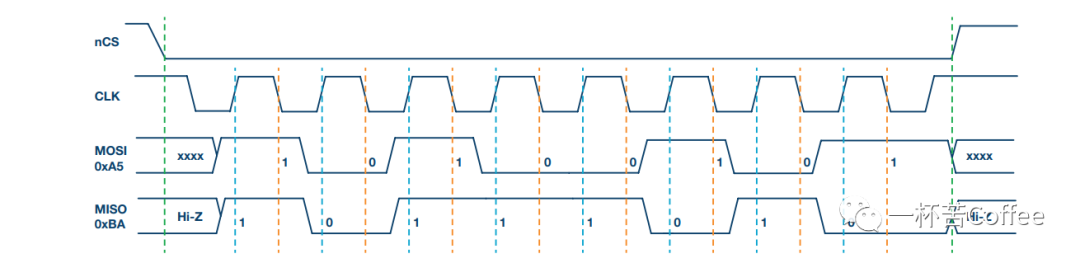

- 時鐘極性(CPOL)和時鐘相位(CPHA)的圖解

說明:

- 綠色:表示數(shù)據(jù)傳輸?shù)拈_始和結(jié)束。

- 橙色:表示數(shù)據(jù)的采樣。

- 藍色:表示數(shù)據(jù)的移位。

- SPI模式0,CPOL = 0,CPHA = 0:CLK空閑狀態(tài) = 低電平,數(shù)據(jù)在上升沿采樣,并在下降沿移出。

- SPI模式1,CPOL = 0,CPHA = 1:CLK空閑狀態(tài) = 低電平,數(shù)據(jù)在下降沿采樣,并在上升沿移出。

- SPI模式2,CPOL = 1,CPHA = 0:CLK空閑狀態(tài) = 高電平,數(shù)據(jù)在下降沿采樣,并在上升沿移出。

- SPI模式3,CPOL = 1,CPHA = 1:CLK空閑狀態(tài) = 高電平,數(shù)據(jù)在上升沿采樣,并在下降沿移出。

4 SPI的級聯(lián)

多個從機可與單個SPI主機一起使用。從機可以采用常規(guī)模式連接,或采用菊花鏈模式連接。

- 常規(guī)模式

在常規(guī)模式下,主機需要為每個從機提供單獨的片選信號。一旦主機使能(拉低)片選信號,MOSI/MISO線上的時鐘和數(shù)據(jù)便可用 于所選的從機。如果使能多個片選信號,則MISO線上的數(shù)據(jù)會被破壞,因為主機無法識別哪個從機正在傳輸數(shù)據(jù)。從下圖可以看出,隨著從機數(shù)量的增加,來自主機的片選線的數(shù)量 也增加。這會快速增加主機需要提供的輸入和輸出數(shù)量,并限制可以使用的從機數(shù)量。可以使用其他技術(shù)來增加常規(guī)模式下的從機數(shù)量,例如使用多路復(fù)用器產(chǎn)生片選信號。

- 菊花鏈模式

在菊花鏈模式下,所有從機的片選信號連接在一起,數(shù)據(jù)從一個從機傳播到下一個從機。在此配置中,所有從機同時接收同一SPI時鐘。來自主機的數(shù)據(jù)直接送到第一個從機,該從機將數(shù)據(jù)提供給下一個從機,依此類推。

使用該方法時,由于數(shù)據(jù)是從一個從機傳播到下一個從機,所以傳輸數(shù)據(jù)所需的時鐘周期數(shù)與菊花鏈中的從機位置成比例。例如在下圖所示的8位系統(tǒng)中,為使第3個從機能夠獲得數(shù)據(jù),需要24個時鐘脈沖,而常規(guī)SPI模式下只需8個時鐘脈沖。圖8顯示了時鐘周期和通過菊花鏈的數(shù)據(jù)傳播。并非所有SPI器件都支持菊花鏈模 式。請參閱產(chǎn)品數(shù)據(jù)手冊以確認(rèn)菊花鏈?zhǔn)欠窨捎谩?/p>

-

微控制器

+關(guān)注

關(guān)注

48文章

7966瀏覽量

155956 -

電路設(shè)計

+關(guān)注

關(guān)注

6713文章

2546瀏覽量

215172 -

接口

+關(guān)注

關(guān)注

33文章

9032瀏覽量

153949 -

SPI

+關(guān)注

關(guān)注

17文章

1806瀏覽量

96316 -

串行外設(shè)接口

+關(guān)注

關(guān)注

0文章

16瀏覽量

4111

發(fā)布評論請先 登錄

硬件電路設(shè)計與開發(fā)項目案例之智能空氣凈化系統(tǒng)

怎么成為硬件電路設(shè)計高手?

硬件電路設(shè)計之接地問題

硬件電路設(shè)計之晶體與晶振電路設(shè)計

硬件電路設(shè)計流程系列

硬件電路設(shè)計的思路分享

硬件電路設(shè)計流程--原理圖設(shè)計

硬件電路設(shè)計之“磁珠”的應(yīng)用資料下載

硬件電路設(shè)計的基本流程、作用和注意事項

硬件電路設(shè)計之SPI電路設(shè)計

硬件電路設(shè)計之SPI電路設(shè)計

評論