1 簡(jiǎn)介

PCIe(Peripheral Component Interconnect Express)是一種應(yīng)用廣泛高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于擴(kuò)充計(jì)算機(jī)系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。

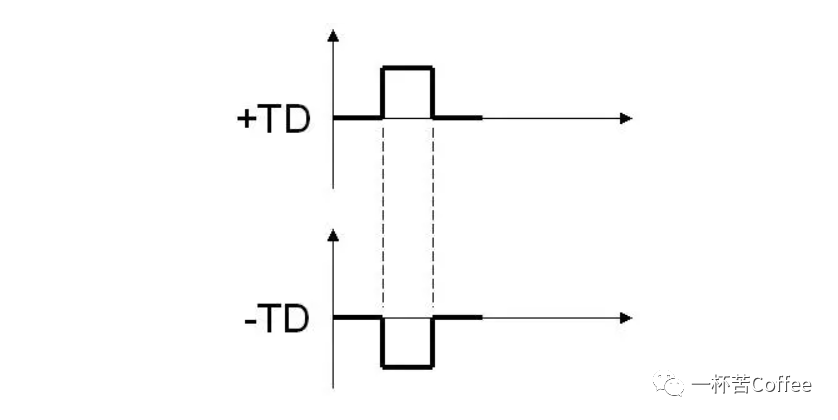

PCIe本質(zhì)上是一種全雙工的的連接總線,傳輸數(shù)據(jù)量的大小由通道數(shù)lane決定的。一般,1個(gè)連接通道lane稱為X1,每個(gè)通道lane由兩對(duì)數(shù)據(jù)線組成,一對(duì)發(fā)送,一對(duì)接收,每對(duì)數(shù)據(jù)線包含兩根差分線。即X1只有1個(gè)lane,4根數(shù)據(jù)線,每個(gè)時(shí)鐘每個(gè)方向1bit數(shù)據(jù)傳輸。依此類推,X2就有2個(gè)lane,由8根數(shù)據(jù)線組成,每個(gè)時(shí)鐘傳輸2bit。類似的還有X12、X16、X32。

2 PCIe的發(fā)展

PCIe的發(fā)展歷史十分長(zhǎng)遠(yuǎn),最早可追溯到1984年,其發(fā)展的歷史見下:

1.ISA (Industry Standard Architecture)

2.MCA (Micro Channel Architecture)

3.EISA (Extended Industry Standard Architecture)

4.VLB (VESA Local Bus)

5.PCI (Peripheral Component Interconnect)

6.PCI-X (Peripheral Component Interconnect eXtended)

7.AGP (Accelerated Graphics Port)

8.PCI Express (Peripheral Component Interconnect Express)

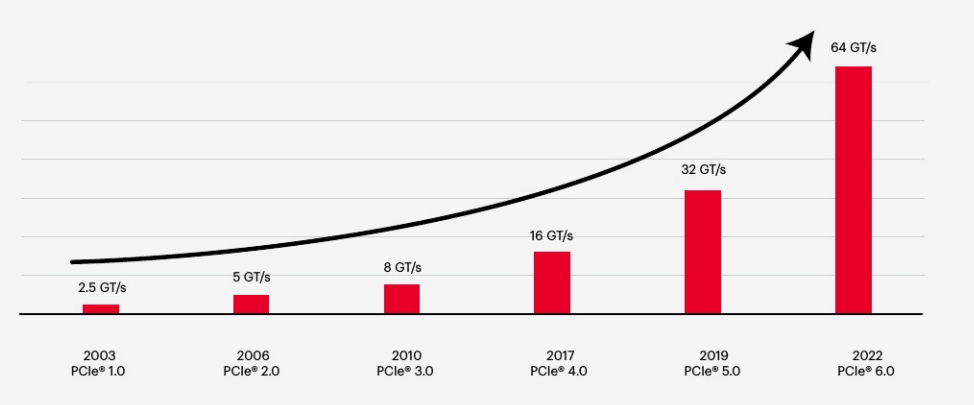

3 PCIe的速率

每一次的升級(jí)換代都是為了解決上一代遺留的問題,而PCIe每次的升級(jí)換代主要是為了解決速率上的不足。詳情見下:

| Lan | PCIe 1.0 | PCIe 2.0 | PCIe 3.0 | PCIe 4.0 |

|---|---|---|---|---|

| x 1 | 250MB/s | 500MB/s | 1GB/s | 2GB/s |

| x 2 | 500MB/s | 1GB/s | 2GB/s | 4GB/s |

| x 4 | 1GB/s | 2GB/s | 4GB/s | 8GB/s |

| x 8 | 2GB/s | 4GB/s | 8GB/s | 16GB/s |

| x 16 | 4GB/s | 8GB/s | 16GB/s | 32GB/s |

4 PCIe通道

PCIe通道比較常見有x1、x4、x8、x16,也有x2的PCIe設(shè)備。這些設(shè)備的主要的差別由

這些連接器主要的差別為:

| 通道數(shù) | PIN腳數(shù) | 主接口區(qū)PIN數(shù) | 總長(zhǎng)度 | 主接口區(qū)總長(zhǎng)度 |

|---|---|---|---|---|

| x1 | 36 | 14 | 25mm | 7.65mm |

| x4 | 64 | 42 | 39mm | 21.65mm |

| x8 | 98 | 76 | 56mm | 38.65mm |

| x16 | 164 | 142 | 89mm | 71.65mm |

注意 :因?yàn)榈诙?shù)據(jù)通道的位置沒有這個(gè)綠色的對(duì)應(yīng)針腳,所以PCI-E X2插槽的設(shè)備并不存在(但是可以用于其他接口,比如X2通道的m.2 NGFF接口和SATA-Express)

5 PCIe的架構(gòu)

PCI-X和AGP都是由PCI發(fā)展而來(lái),為了提高數(shù)據(jù)傳輸?shù)乃俾剩咦吡藘蓷l不同的路徑:

- PCI-X通過不斷提供時(shí)鐘的頻率來(lái)實(shí)現(xiàn)高速數(shù)據(jù)傳輸。

- AGP通過在一個(gè)時(shí)鐘周期內(nèi)傳輸多次數(shù)據(jù)來(lái)實(shí)現(xiàn)高速數(shù)據(jù)傳輸。

但是隨著數(shù)據(jù)速率的提高,數(shù)據(jù)傳輸?shù)目垢蓴_性越來(lái)越差。為了解決這一問題,PCIe采用差分信號(hào)傳輸?shù)姆绞絹?lái)增加數(shù)據(jù)傳輸系統(tǒng)抗干擾性。

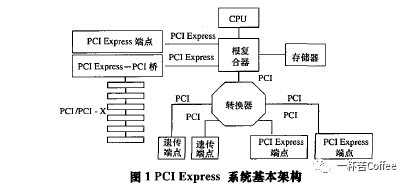

以下是一個(gè)典型的點(diǎn)對(duì)點(diǎn)連接,但是通過PCIe Switch可以連接多個(gè)PCIe設(shè)備。可以很明顯的看出PCI和PCIe的不同:PCI是總線結(jié)構(gòu),而PCIe是點(diǎn)對(duì)點(diǎn)結(jié)構(gòu)。PCIe架構(gòu)包含CPU系統(tǒng)(中央處理器)、Root Complex(根復(fù)合器)、Memory(存儲(chǔ)器)、PCIe Switch(轉(zhuǎn)換器)、PCIe Bridge(PCIe橋)、PCIe設(shè)備。

- CPU系統(tǒng):一般為ARM和X86平臺(tái)。

- Root Complex:CPU和PCle總線之間的接口,可能包含幾個(gè)組件(處理器接口、DRAM接口等),甚至可能包含幾個(gè)芯片。

- Switch:Switch提供了分散或者是聚合的功能,它允許更多的設(shè)備接入到 一個(gè)PCIe Port,它扮演了數(shù)據(jù)包路由的功能。

- PCIe Bridge:Bridge提供了一個(gè)轉(zhuǎn)換接口用來(lái)連接其他的總線,如PCI/PCI-X。這樣可以允許在PCIe的系統(tǒng)中接入一張舊的PCI設(shè)備。

- PCIe設(shè)備:滿足PCIe協(xié)議的總線的設(shè)備被稱為PCIe設(shè)備。

- Memory:用于存儲(chǔ)一些重要的信息。

6 PCIe常見問題

- PCIe x1設(shè)備可以直接使用在x4的卡槽,只是會(huì)浪費(fèi)資源,功能正常使用。

- PCIe x16設(shè)備可以在x8的插槽使用,由于卡槽尺寸的限制,需要另外的轉(zhuǎn)接板實(shí)現(xiàn)。

- PCIe 3.0的設(shè)備可以在PCIe2.0的主板上使用。

-

接口

+關(guān)注

關(guān)注

33文章

8880瀏覽量

152941 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7605瀏覽量

89767 -

總線

+關(guān)注

關(guān)注

10文章

2935瀏覽量

89129 -

PCIe

+關(guān)注

關(guān)注

16文章

1299瀏覽量

84347

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCIe標(biāo)準(zhǔn)的演進(jìn)歷史 各代PCIe標(biāo)準(zhǔn)之間的主要差異

risc-v的發(fā)展歷史

RISC架構(gòu)服務(wù)器簡(jiǎn)介

RTOS發(fā)展歷史

操作系統(tǒng)發(fā)展歷史

FPGA技術(shù)的發(fā)展歷史和動(dòng)向

嵌入式系統(tǒng)的發(fā)展歷史

談?wù)剦好綦娮璧?b class='flag-5'>發(fā)展歷史

單片機(jī)的發(fā)展歷史

Powerpc架構(gòu)與X86架構(gòu)的區(qū)別

PCIE基本概念與拓?fù)?b class='flag-5'>架構(gòu)圖

PCIe?標(biāo)準(zhǔn)演進(jìn)歷史

PCIe串行總線發(fā)展歷史及工作原理

PCIe簡(jiǎn)介、發(fā)展歷史及架構(gòu)

PCIe簡(jiǎn)介、發(fā)展歷史及架構(gòu)

評(píng)論