傳統(tǒng)帶隙電壓基準(zhǔn)

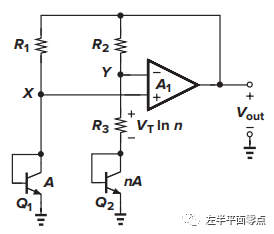

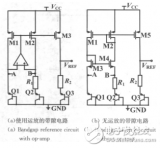

圖1(來(lái)源于《模擬CMOS集成電路設(shè)計(jì)(英文第2版)》)

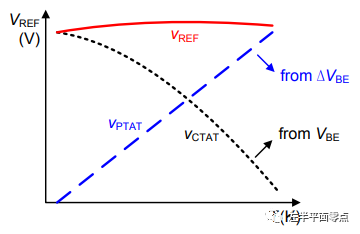

傳統(tǒng)的帶隙電壓基準(zhǔn)如圖1所示,雙極型晶體管基極-發(fā)射極電壓差ΔVBE具有正溫度系數(shù),而雙極型晶體管基極-發(fā)射極電壓VBE具有負(fù)溫度系數(shù),如果將兩個(gè)電壓進(jìn)行相加,理論上就可以通過(guò)設(shè)計(jì)合適的參數(shù)實(shí)現(xiàn)零溫度系數(shù)電壓,如圖2。具體可以參考拉扎維模集的第12章的內(nèi)容。

圖2(來(lái)源于公開(kāi)資料)

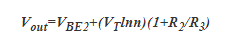

圖1電路輸出電壓為:

其中當(dāng)ln n (1+R2/R3 )約等于17.2時(shí)可以實(shí)現(xiàn)輸出電壓Vout的零溫度系數(shù)。于是該電路有雙極型晶體管不同的電流密度比例n以及R2、R3電阻的阻值3個(gè)設(shè)計(jì)因子。

全CMOS帶隙電壓基準(zhǔn)

與利用雙極型晶體管的基極-發(fā)射極電壓差ΔVBE、基極-發(fā)射極電壓VBE實(shí)現(xiàn)正負(fù)溫度系數(shù)抵不同,全CMOS帶隙電壓基準(zhǔn)利用了增強(qiáng)型MOS與耗盡型MOS閾值電壓不同的原理來(lái)實(shí)現(xiàn)電壓基準(zhǔn)。MOS的閾值電壓均呈現(xiàn)負(fù)溫度系數(shù),但增強(qiáng)型MOS的閾值電壓>0,耗盡型MOS的閾值電壓<0。

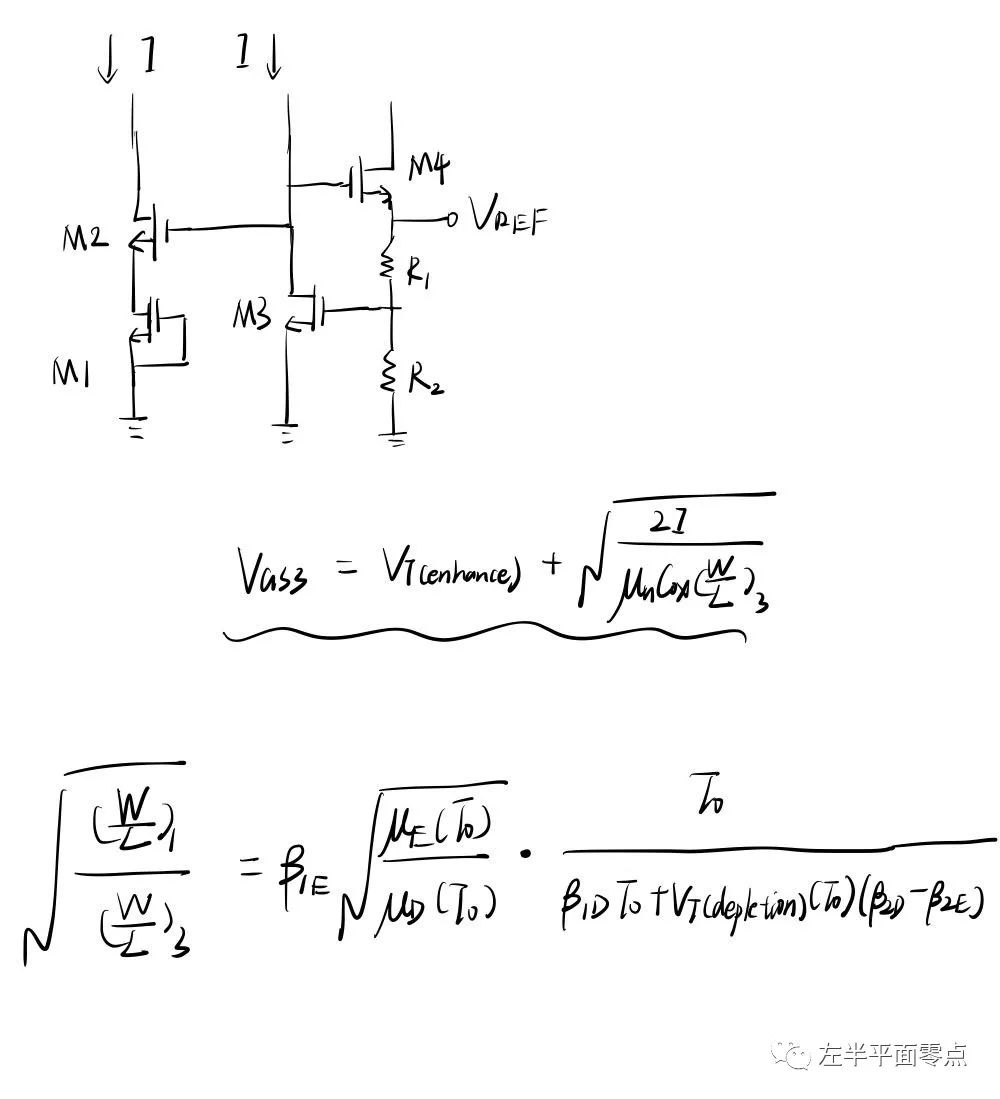

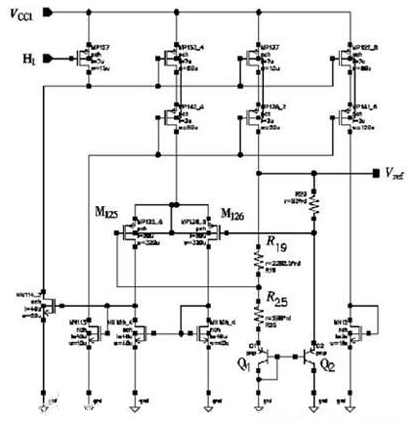

圖3

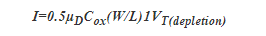

如圖3,其中M1、M2為耗盡型MOS,處于常開(kāi)狀態(tài),此支路必然導(dǎo)通,設(shè)電流為 I ,則I 可以表示為 (其中VT(depletion)為耗盡型MOS的閾值電壓、μD為耗盡型MOS的電子遷移率) :

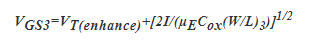

其中M3為增強(qiáng)型MOS,假設(shè)使M3通過(guò)的電流也為I ,那么其柵源電壓可以表示為(其中 VT(enhance)為增強(qiáng)型MOS的閾值電壓、μE為增強(qiáng)型MOS的電子遷移率):

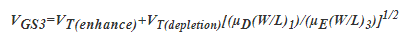

還可以寫(xiě)為:

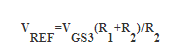

基準(zhǔn)電壓為:

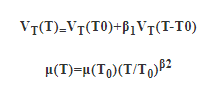

而MOS的閾值電壓以及電子遷移率都會(huì)隨溫度變化,可以寫(xiě)為以下關(guān)系(其中β1為MOS閾值電壓的溫度系數(shù)、β2為電子遷移率的溫度系數(shù),T0為常溫):

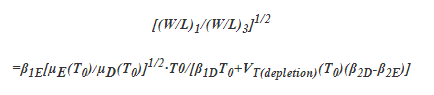

把這兩個(gè)關(guān)系式代回VREF的表達(dá)式中,或者代回VGS3計(jì)算量更小一些,并對(duì)溫度T求導(dǎo),再令其為零。可以自己試著推導(dǎo)一下,公式太長(zhǎng)懶得敲了,就只把結(jié)論給出來(lái)叭,M1與M3的尺寸關(guān)系需滿足(其中β1E 、β2E為增強(qiáng)型MOS的閾值電壓溫度系數(shù)和電子遷移率溫度系數(shù),β1D 、β2D為耗盡型MOS的閾值電壓溫度系數(shù)和電子遷移率溫度系數(shù)):

結(jié)束語(yǔ)

突然覺(jué)得學(xué)模擬真的很難,之前總覺(jué)得看完了拉扎維的模集自己好像沒(méi)什么東西學(xué)了,但現(xiàn)在發(fā)現(xiàn)并不是這樣。拉扎維老先生的模集真的是一本圣經(jīng)!可以說(shuō)早上看跟晚上看有不一樣的收獲、同男生一起看跟同女生一起看有不一樣的收獲甚至吃飯看跟上廁所看也有不一樣的收獲,哈哈哈。所以感覺(jué)一方面要多讀幾遍,另一方面模擬集成電路有意思的電路真的很多,拉扎維老先生也不可能把所有的東西全寫(xiě)上去(都已經(jīng)幾百頁(yè)厚了你還想怎么樣?),所以說(shuō)還要讀各種各樣的文章,堅(jiān)持下去就好了,總有一天會(huì)派上用場(chǎng)。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11971瀏覽量

367393 -

CMOS

+關(guān)注

關(guān)注

58文章

5996瀏覽量

238214 -

電壓基準(zhǔn)

+關(guān)注

關(guān)注

1文章

106瀏覽量

21200 -

晶體管

+關(guān)注

關(guān)注

77文章

9989瀏覽量

140833

發(fā)布評(píng)論請(qǐng)先 登錄

基于LDO穩(wěn)壓器的帶隙基準(zhǔn)電壓源設(shè)計(jì)

請(qǐng)問(wèn)如何實(shí)現(xiàn)低電壓帶隙基準(zhǔn)電壓源的設(shè)計(jì)?

求一種低溫漂輸出可調(diào)帶隙基準(zhǔn)電壓源的設(shè)計(jì)方案

帶隙基準(zhǔn)是什么?帶隙基準(zhǔn)的結(jié)構(gòu)是由哪些部分組成的?

基于汽車(chē)環(huán)境的帶隙基準(zhǔn)電壓源的設(shè)計(jì)

CMOS帶隙基準(zhǔn)電壓源曲率校正方法

CMOS帶隙基準(zhǔn)電壓源中的曲率校正方法

帶隙電壓基準(zhǔn)源的設(shè)計(jì)與分析

用于音頻AD轉(zhuǎn)換器的CMOS帶隙電壓基準(zhǔn)源

cmos帶隙基準(zhǔn)電壓源設(shè)計(jì)

帶隙基準(zhǔn)電路_cmos無(wú)運(yùn)放帶隙基準(zhǔn)源

帶隙基準(zhǔn)是什么_帶隙基準(zhǔn)電路的優(yōu)點(diǎn)

全CMOS帶隙電壓基準(zhǔn)的工作原理

全CMOS帶隙電壓基準(zhǔn)的工作原理

評(píng)論