上次我的文章解釋了所謂的7nm不是真的7nm,是在實際線寬無法大幅縮小的前提下,通過改變晶體管結(jié)構(gòu)的方式縮小晶體管實際尺寸來達到等效線寬的效果

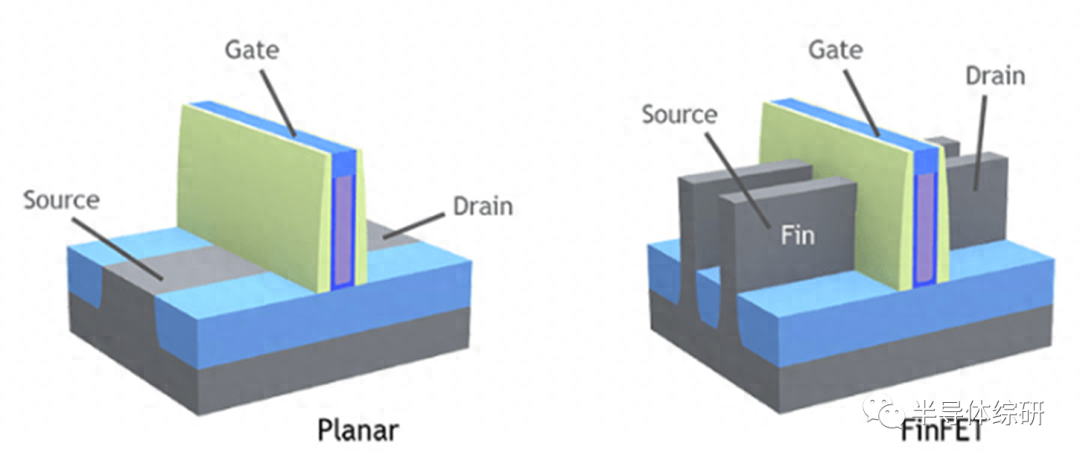

那么新的問題來了:從平面晶體管結(jié)構(gòu)(Planar)到立體的FinFET結(jié)構(gòu),我們比較容易理解晶體管尺寸縮小的原理。如下圖所示:

那么從20nm開始到3nm,晶體管的結(jié)構(gòu)都是FinFET的。結(jié)構(gòu)沒有變化的條件下,晶體管尺寸是如何縮小那么多的呢?

之前網(wǎng)絡(luò)上的解釋是:某公司的7nm技術(shù)是采用了多重曝光方法以后提升了分辨率

其實這種說法是錯誤的,或者說至少是有很大誤導性的

多重曝光技術(shù)是現(xiàn)代先進半導體工藝里的一個通用技術(shù)了,如果我沒有記錯,從32nm或者28nm工藝節(jié)點開始,多重曝光技術(shù)就已經(jīng)被應用了

所以從14nm到7nm工藝,如果不是用EUV替代DUV,那現(xiàn)有的光刻技術(shù)是無法大幅度降低現(xiàn)況的。也就是說,要縮小晶體管的尺寸,必須另找辦法

微縮晶體管的尺寸的方法不少,各家都有自己的絕活和妙招,我這里講幾個常用的方法

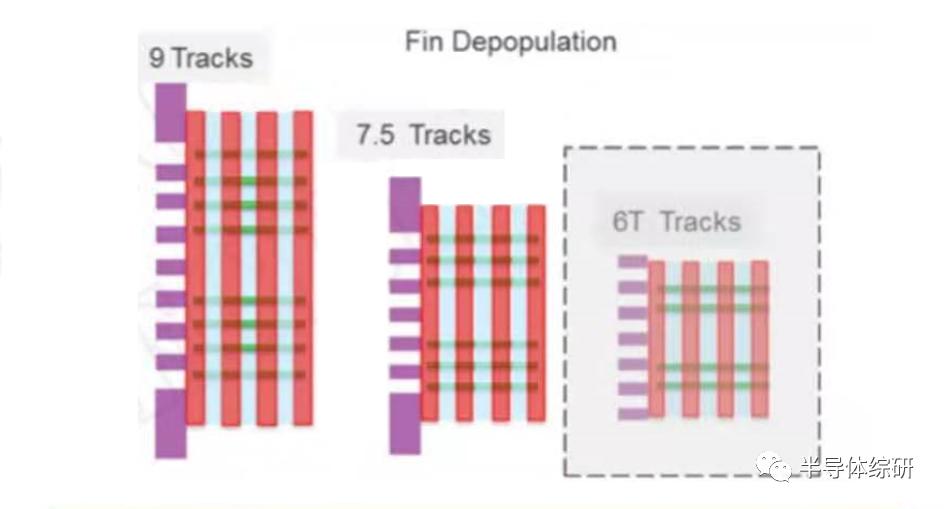

首先,一個CMOS晶體管里無論是P管還是N管,它的鰭片(Fin)的數(shù)量一定不止一個。因為單個Fin太細,通過的電流不夠大,所以需要多個Fin并聯(lián)來提高電流

在Fin的間距不變的情況下,F(xiàn)in的數(shù)量就決定了晶體管的高度。所以行業(yè)里要縮小晶體管的尺寸,就是盡量減少每個MOS管里需要的Fin的數(shù)量

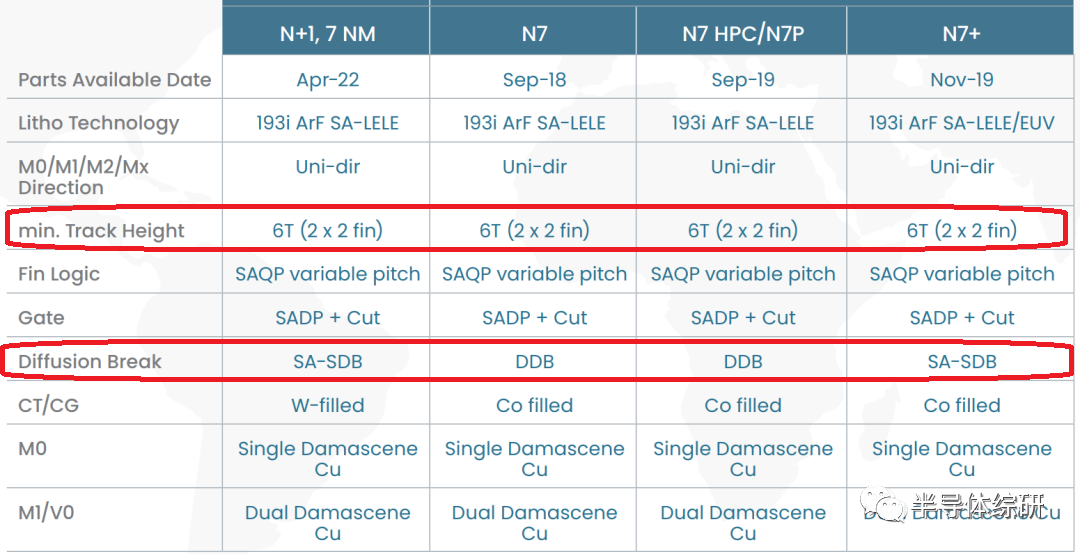

由下圖可知,從左到右,晶體管的鰭片數(shù)量從4個減少到3個,然后是2個。這樣整個晶體管的面積就大幅縮小了。從20nm一直到5nm甚至3nm,這個數(shù)量一直在減少(當然,通過采用EUV和多重曝光技術(shù),F(xiàn)in的間距也是同時在不斷縮小)

上圖里Track這個詞是衡量晶體管高度的一個單位。它實際上是第1、2層金屬層里最細的連線的間距大小。一個間距大小就是一個Track,晶體管高度是連線間距的幾倍,就叫幾個Tracks

金屬連線的間距值MxP和柵極線條最小間距CPP值(上圖里豎直方向的紅色線條)就基本反映了圖形加工工藝的水平,也決定了晶體管的大小

詳細說明見我文章:關(guān)于芯片的7nm到底是個啥,我得繼續(xù)講講

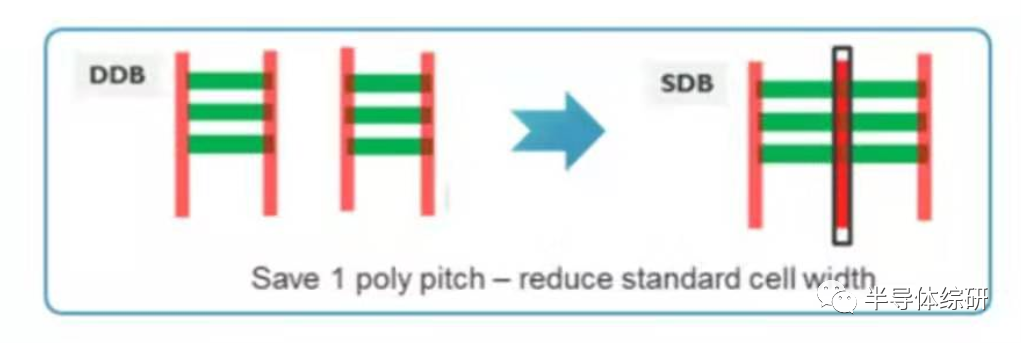

另外,還有一個比較巧妙的路徑就是:如果不能縮小晶體管的面積,那我們也可以縮小晶體管之間的間隔空間來實現(xiàn)密度提升啊

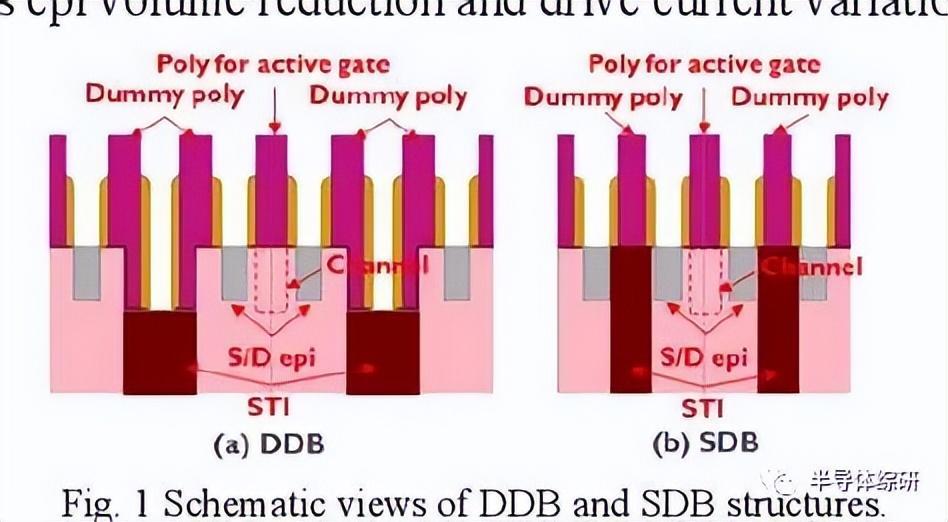

晶體管之間要做電性能隔離,一般都是用擴散層實現(xiàn)的,這個叫Diffusion Breaks。原本每個晶體管各自有一個隔離帶,叫DDB(Double Diffusion Breaks),現(xiàn)在為了節(jié)約空間,只用一個隔離帶了,叫SDB(Single Diffusion Breaks)

就好比你家院子和鄰居院子如果各修一個籬笆,自然會占用更多土地面積。于是你們兩家商量一下,想辦法合建一個籬笆來隔離,自然就能多出一些空間來

下面兩張圖分別是DDB和SDB的俯視圖和橫截面示意圖,大家看了自然就會明白

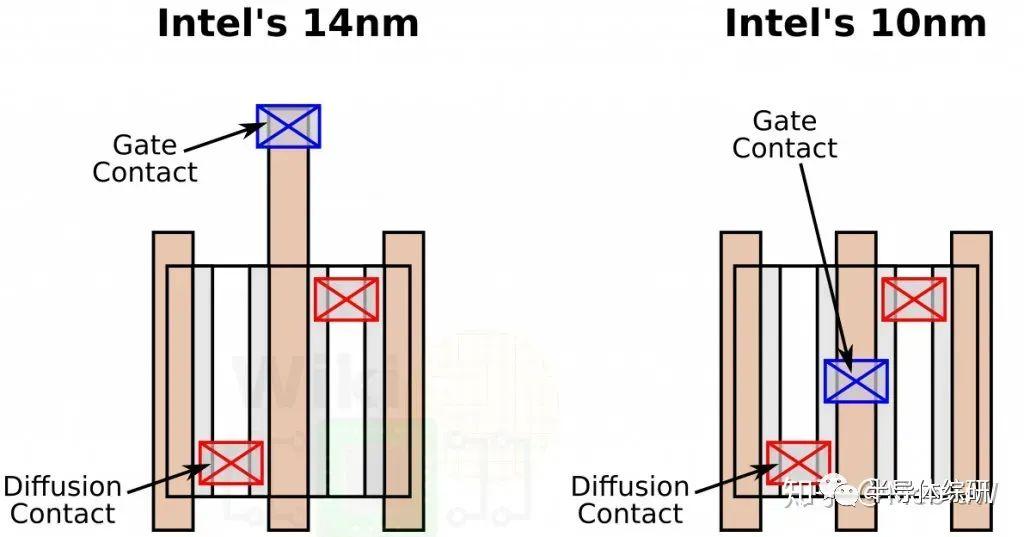

另外,Intel家還在很早就開發(fā)了一種叫COAG(Contact Over Active Gate)的技術(shù)。原本需要在空白地方制作柵極接觸點會占用額外的空間,所以Intel想辦法把接觸點的位置直接做到了柵極的上面,就可以節(jié)約大量空間。如下圖所示:

這個想法當然是非常絕妙的。但可惜的是,由于各種原因,這個技術(shù)的良率一直做不好,直接影響了Intel先進工藝的開發(fā)進度。這也是他家工藝逐漸被臺積電和三星趕上并超越的重要原因之一吧

以上就是幾個縮小晶體管尺寸的常用技術(shù)方案了。其實還有其它很多微縮的方法,比如用金屬鈷(Co)代替銅,用空腔代替?zhèn)鹘y(tǒng)金屬連線介電層等方案來縮小BEOL段的金屬連線尺寸的方法。限于篇幅,我這里就不展開講了

不管如何,怎么樣?上面這張表里紅框部分的內(nèi)容你是不是一下就看懂了?瞬間覺得自己長知識了的感覺有沒有?

注:轉(zhuǎn)載至 半導體綜研 文中觀點僅供分享交流,不代表貞光科技立場,如涉及版權(quán)等問題,請您告知,我們將及時處理!

-

芯片

+關(guān)注

關(guān)注

459文章

52316瀏覽量

438157 -

CMOS

+關(guān)注

關(guān)注

58文章

6002瀏覽量

238374 -

晶體管

+關(guān)注

關(guān)注

77文章

9995瀏覽量

141028

發(fā)布評論請先 登錄

cs1237兩個差分線,正極端電壓大于負極端,兩者相差越大,讀出來的數(shù)據(jù)越來越小

沒有半導體的晶體管有望開啟新的電子設(shè)備時代

晶體管的主要參數(shù)

差分放大器AD8139單端輸入頻率增加,輸出的差分信號幅度會越來越小

概述晶體管

什么是晶體管 晶體管的分類及主要參數(shù)

單電子晶體管

拯救摩爾定律 IBM 9nm工藝碳納米晶體管

MEMS技術(shù)讓麥克風越來越小

為何c盤空間越來越小

晶體管對于CPU有什么影響

人工智能AI正在進入到越來越小的物聯(lián)網(wǎng)設(shè)備中

晶體管是怎么做得越來越小的?

晶體管是怎么做得越來越小的?

評論