歡迎了解

李彥林丑晨甘雨田

(甘肅林業(yè)職業(yè)技術(shù)學院)

摘要:

電子封裝是將裸IC硅片用塑料包起來保護好并制作好外部引腳。外引線越來越多是微電子封裝的一大特點,當然也是難點,引腳間距越小,再流焊時焊料難以穩(wěn)定供給,故障率很高。多引腳封裝是今后的主流,所以在微電子封裝的技術(shù)要求上應盡量適應多引腳。但芯片的封裝都是有一定規(guī)范的,假如每家封裝廠都執(zhí)行各自的標準顯然芯片的通用性會大打折扣,也不可能造就半導體產(chǎn)業(yè)的繁榮。鑒于此,本文對不同電子封裝技術(shù)問題展開討論,分析電子封裝技術(shù)存在的問題,設計具體改進方案,提高產(chǎn)品的可靠性,降低制造成本和安全風險。以期為微電子封裝技術(shù)標準化生產(chǎn)提供借鑒和指導。

引 言

微電子封裝是將一個或多個集成電路和倒裝芯片鍵合連接,使之成為有實用功能的電子元器件或組件。本文探究對微電子封裝技術(shù)的安全可靠性,通過技術(shù)攻關(guān),攻克高密度窄間距小焊盤銅線鍵合工藝關(guān)鍵技術(shù)難題,提升銅線替代金線在小焊盤、窄間距 IC 芯片封裝領(lǐng)域的工藝水平,促進企業(yè)技術(shù)創(chuàng)新和產(chǎn)品的自主開發(fā)能力,縮小與國外封裝技術(shù)的差距,提升產(chǎn)品質(zhì)量和標準化水平。

1微電子封裝技術(shù)和現(xiàn)狀

電子封裝技術(shù)涉及眾多學科,涉及材料學、電磁學、熱管理、微納制造、電子器件等專業(yè)。隨著微電子封裝科學工作者對三維集成電路的研發(fā)逐步深入,電子封裝正在從傳統(tǒng)制造模式,向系統(tǒng)封裝 (SOP - System On Package /SiP - System in Package)、三維封裝 (3D Packaging) 模式轉(zhuǎn)變,系統(tǒng)封裝先進封裝技術(shù)已經(jīng)開始走向市場。而電子技術(shù)發(fā)展迅速,更新?lián)Q代極快,三維封裝 (3D Packaging) 目前尚無具體的國家技術(shù)標準,電子封裝技術(shù)多采用國外研究的機構(gòu)技術(shù)標準。封裝的形式多種多樣,以最普通的雙列直插(DIP,dual in-line package)舉例,DIP8 表示有8 個引腳,引腳的長度、間距、寬度等等都有嚴格的標準去執(zhí)行,封裝廠只會按照這個標準來執(zhí)行,假如現(xiàn)在裸片只有 7 個 PAD 怎么辦?當然還是要用 DIP8,只是一個引腳懸空,當然不可能隨意的設計引腳個數(shù),半導體產(chǎn)業(yè)各個方面都有標準,“無規(guī)矩不成方圓”,微電子封裝技術(shù)從“原始生長”到“成熟發(fā)展”需要進行有機的規(guī)范。通過完善微電子封裝技術(shù)相關(guān)標準,消除不同品牌的微電子封裝技術(shù)硬件設備所采集的數(shù)據(jù)格式和數(shù)據(jù)質(zhì)量存在差異,推動信息的流動和共享,消除數(shù)據(jù)孤島成為新型微電子封裝技術(shù)發(fā)展創(chuàng)新的迫切需求。

1.1 新型微電子封裝技術(shù)

根據(jù)中華人民共和國國家質(zhì)量監(jiān)督檢驗檢疫標準的要求 , 《微電子技術(shù)用貴金屬漿料規(guī)范 (GB/T 17472-2008)》原標準適用范圍,由厚膜微電子技術(shù)用貴金屬漿料擴大至燒結(jié)型及固化型微電子技術(shù)用貴金屬漿料;更注重漿料可焊性、耐焊性。 一般說來,微電子封裝分為三級,包含組裝和封裝的多項內(nèi)容。微電子封裝所包含的范圍應包括單芯片封裝 (SCP) 設計和制造、多芯片封裝 (MCM) 設計和制造、芯片后封裝工藝、各種封裝基板設計和制造、芯片互連與組裝、封裝總體電性能、機械性能、熱性能和可靠性設計、封裝材料、封裝工模夾具以及綠色封裝等多項內(nèi)容。

1.2 新型微電子封裝技術(shù)主要包括以下幾種

發(fā)展微電子封裝技術(shù),旨在使系統(tǒng)向小型化、高性能、高可靠性和低成本目標努力,從技術(shù)發(fā)展觀點來看,作為微電子封裝的關(guān)鍵技術(shù)主要有:(1)3D 封裝,在 2D封裝的基礎(chǔ)上,把多個裸芯片、封裝芯片、多芯片組件甚至圓片進行疊層互連,構(gòu)成立體封裝,這種結(jié)構(gòu)稱作疊層型 3D 封裝(2) 焊球陣列封裝(BGA):陣列封裝(BGA)以圓形或柱狀焊點按陣列形式分布在封裝下面,從而提高了組裝成品率。組裝可用共面焊接,可靠性高;(3) 芯片尺寸封裝(CSP)是芯片級封裝的意思。CSP 封裝可以讓芯片面積與封裝面積之比超過 1:1.14,已經(jīng)相當接近 1:1的理想情況。與 BGA 封裝相比,同等空間下 CSP 封裝可以將存儲容量提高三倍;(4) 系統(tǒng)封裝(SIP)即通過封裝來實現(xiàn)整機系統(tǒng)的功能。

2微電子三維 (3D) 封裝技術(shù)問題分析

2.1 應用范圍不夠廣泛

從微電子封裝技術(shù)的材料可以看出,IC 芯片將向小型化、高性能并滿足環(huán)保要求的方向發(fā)展。微電子封裝技術(shù)應用范圍不夠廣泛 , 在過去幾年中已通用的高于 208 個管腳、256 個管腳、304 個管腳,間距 0.5mm 款式、包括間距 0.4mm 款式 QFPs,其 QFPs 材料多為塑料和陶瓷殼體,通常各類塑料型器件適合于較高的引線數(shù)。

2.2 傳統(tǒng)銅線鍵合工藝問題

由于傳統(tǒng)銅線鍵合工藝的極限能力為芯片焊盤尺寸≥ 50μm×50μm、焊盤間距≥ 60μm,對此尺寸以下的芯片只能采用金線工藝,而在研究過程中,要實現(xiàn)此金線工藝被合理替代,必須解決小焊點、窄間距銅線鍵合所面臨的以下問題:

第一:銅線鍵合空氣球防氧化技術(shù);

第二:防止銅線鍵合焊盤損傷和對“鋁飛濺”控制鍵合技術(shù);

第三:第二焊點鍵合強度的研究;

第四:銅線鍵合防裂紋和彈坑技術(shù)。

隨著 QFP 封裝引線數(shù)的增加,其殼體尺寸急劇地增加,可以替代封裝尺寸增加的是更進一步縮減引線間距。因此,要對高密度窄間距封裝技術(shù)進行研發(fā)與技術(shù)改進。

3具體改進方案

為了解決微電子三維 (3D) 封裝技術(shù)方面的問題,我們制定了以下方案:芯片焊盤尺寸為 38μm×38μm,焊點間距為 43μm 的芯片;焊線材料:普通銅線,直徑為0.7mil。開展不同保護氣體中空氣球尺寸的穩(wěn)定性研究。

3.1 技術(shù)路線方案論證

3.1.1 技術(shù)路線

前期調(diào)研、規(guī)劃→確定工藝流程→關(guān)鍵技術(shù)攻關(guān)→工程批試驗→可靠性考核→風險批試生產(chǎn)→小批量生產(chǎn)→轉(zhuǎn)入量產(chǎn)。

3.1.2 技術(shù)方案

為了解決以上問題,我們制定了以下二種方案:

A. 方案一

(1)銅線鍵合空氣球防氧化研究

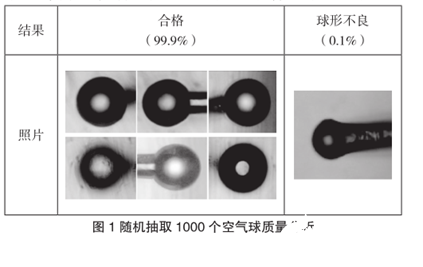

在氫氮混合保護氣體(流量:0.4 ~0.7L/min)下,隨機抽取 1000 個空氣球?qū)Ρ冉Y(jié)果如下:在 N2+H2 保護氣體條件下,0.7mil 普通銅線燒球有 20.03% 的空氣球表面有氧化和桃形球,非對稱球、凹凸球、孔洞球等球形不良比例達到 40% 左右。

(2)第一焊點研究實驗

第 一 焊 點 研 究 實 驗 結(jié) 果 為 : 在 焊 盤 尺 寸 為38μm×38μm、焊點間距為 43μm 的芯片上進行銅線鍵合試驗,球形不良(高爾夫球)占 57%,鍵合強度(不粘和失鋁)不滿足質(zhì)量要求占 6.77%;圖 1 隨機抽取 1000個空氣球質(zhì)量分析 . 球形不良(0.1%)合格(99.9%)。

B. 方案二

芯片焊盤尺寸為 38μm×38μm,焊點間距為 43μm的芯片;

焊線材料:鍍鈀銅線(Pd coat Cu Wire),線徑為0.7mil

(1)銅線鍵合空氣球防氧化研究

通過對不同保護氣體中空氣球尺寸的穩(wěn)定性、不同保護裝置(Kit)中空氣球形狀的穩(wěn)定性、保護氣體流量(Froming Gas)對空氣球影響的研究,達到了銅線鍵合工藝標準。

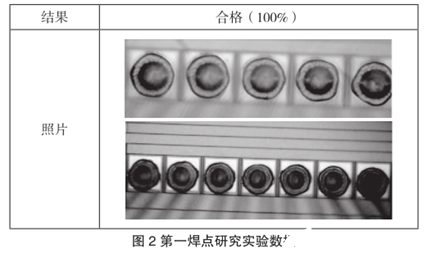

(2)第一焊點研究實驗

選擇配套設備和匹配的劈刀型號,對鍵合工藝參數(shù)進行研究,通過對功率、沖擊力、X/Y 方向摩擦力、旋轉(zhuǎn)摩擦力等參數(shù)進行優(yōu)化試驗,最終確定了一組較為理想的工藝參數(shù)。另外,聯(lián)合芯片商對芯片鋁墊進行了改善,并建立了銅線制程能力評估規(guī)范,使焊盤“鋁飛濺”、失鋁(Peeling)得到有效的控制,最終符合銅線鍵合工藝標準,第一焊點研究實驗數(shù)據(jù)合格(100%)圖 2 所示。

(3)第二焊點研究實驗

通過優(yōu)化劈刀的設計,選擇合適的劈刀型號,增大了第二點接觸的面積和魚尾厚度;通過優(yōu)化線弧參數(shù),使魚尾和 Lead 更貼合; [2] 通過優(yōu)化焊接參數(shù),增大了第二焊點功率、壓力,必要時使用研磨參數(shù),可增強第二焊點拉力并穩(wěn)定線尾(Wire Tail Length);通過以上第二焊點鍵合質(zhì)量的深入研究,達到了銅線鍵合質(zhì)量標準。

(4)銅線鍵合防裂紋和彈坑研究

通過銅線材防氧化措施,焊盤鋁層厚度、成分的控制,銅線鍵合快速確認焊盤鋁殘留厚度的研究,最終使銅線鍵合裂紋和彈坑得到了有效控制。

結(jié)論通過以上研究,使鍍鈀銅線鍵合能力滿足工藝要求,達到了高密度窄節(jié)距(43μm)小焊盤(38μm×38μm)IC 芯片的封裝要求。實現(xiàn)了 SEMI( 國際半導體設備與材料協(xié)會 ) 等國際標準化組織在電子封裝領(lǐng)域內(nèi)電鍍技術(shù)的標準化要求。

4 結(jié)論

該方案采用焊盤尺寸為 38μm×38μm、焊盤間距為43μm、鋁墊厚度為 0.9μm、介質(zhì)結(jié)構(gòu)為 FSG(氟硅酸鹽玻璃)的芯片研究了銅線鍵合技術(shù),建立了線徑為 0.7mil高可靠性鍍鈀銅線鍵合工藝的制程能力,有效保障了小焊盤(38μm×38μm)窄間距(43μm)的銅線鍵合封裝技術(shù)在 LQFP、TQFP 、eLQFP、多圈 QFN 系列產(chǎn)品中的推廣應用。因此,本設計方案能實現(xiàn)該項目的技術(shù)指標,達到研究的目的和意義,為標準化生產(chǎn)提供了技術(shù)保障。

審核編輯 黃宇

-

IC

+關(guān)注

關(guān)注

36文章

6102瀏覽量

178542 -

引腳

+關(guān)注

關(guān)注

16文章

1614瀏覽量

52438 -

微電子封裝

+關(guān)注

關(guān)注

1文章

30瀏覽量

7184

發(fā)布評論請先 登錄

廣凌科技標準化考場建設方案:全系統(tǒng)技術(shù)賦能與場景落地

智能照明互聯(lián)新突破:泰凌微電子邀您共探 Matter 技術(shù)前沿

廣凌創(chuàng)新解決方案:高校標準化考點建設

廣凌高校標準化考場建設解決方案

靈動微電子助力汽車芯片可靠性提升

材料選擇對TNC連接器標準化進程的影響

全國集成電路標準化技術(shù)委員會首次“標準周”活動在滬舉辦

科力銳分布式架構(gòu)災備云入選中國電子技術(shù)標準化研究院典型案例

普源精電榮獲電子測量儀器標準化先進工作單位獎

芯海科技引領(lǐng)智能化浪潮:標準化單鍵壓力按鍵解決方案賦能終端創(chuàng)新

CAN技術(shù)的標準化之旅

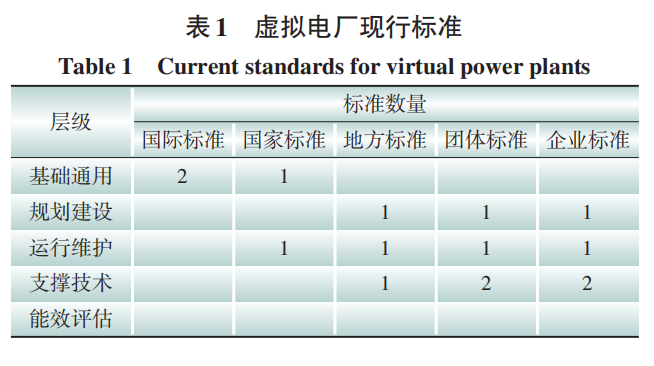

淺談虛擬電廠標準化現(xiàn)狀與需求分析

工信部引領(lǐng)未來科技浪潮,腦機接口標準化技術(shù)委員會籌建方案揭曉

國際標準化組織實驗室設計技術(shù)委員會及中關(guān)村標準化協(xié)會 蒞臨東舟技術(shù)指導創(chuàng)新發(fā)展工作

新型微電子封裝技術(shù)問題及改進方案標準化研究

新型微電子封裝技術(shù)問題及改進方案標準化研究

評論